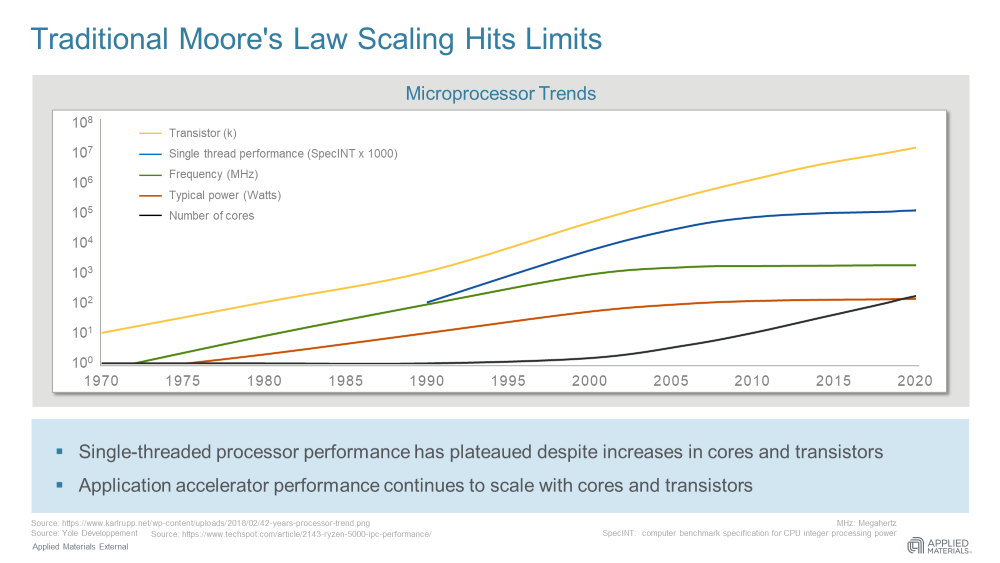

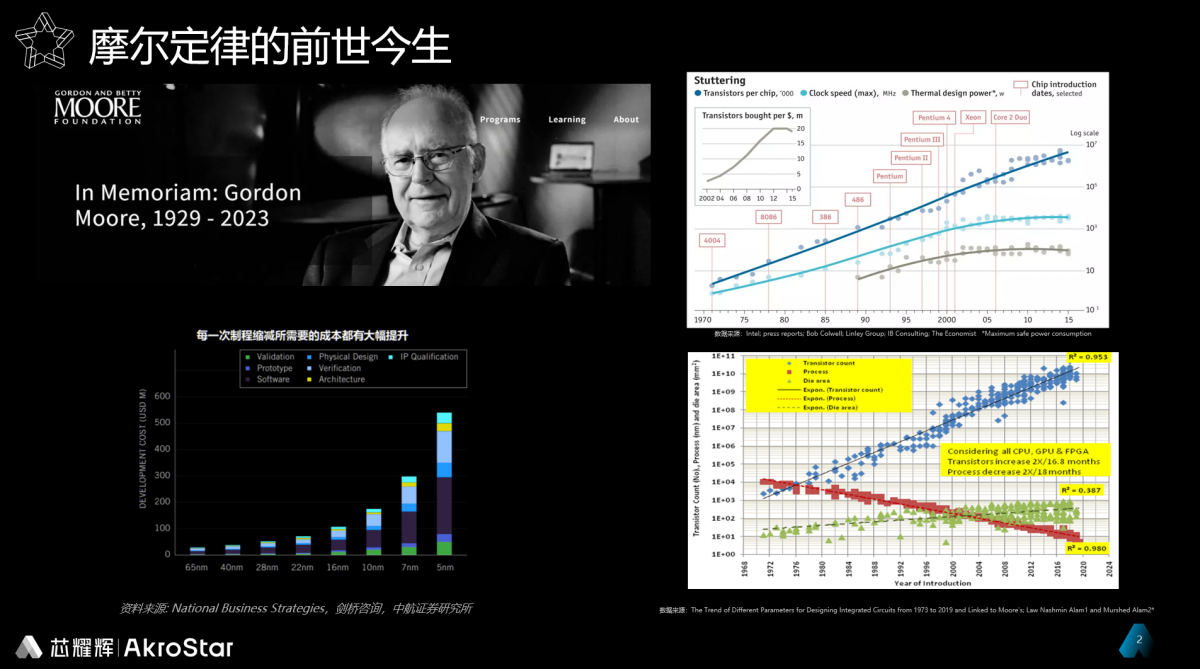

? ? ?隨著FPGA 的作用在系統設計中的日益凸顯,需要更大的邏輯容量和更多的片上資源。到日前為止,FPGA 主要遵循摩爾定律的發展速度來應對這種需求,每一代新工藝技術增加近兩倍的邏輯容量。然而,要跟上當今高端市場的需求增長步伐,就需要必須超越摩爾定律。為了滿足上述需求,賽靈思采用創新堆疊硅片互聯(SSI)技術來構建FPGA,使其與最大型FPGA 芯片相比,帶寬和容量相當甚至更高,同時將功耗降至最低。

世界最大容量FPGA: Virtex-7 2000T

賽靈思推出采用堆疊硅片互聯(SSI)技術的世界最大容量FPGA: Virtex-7 2000T。這款包含68 億個晶體管的FPGA具有1,954,560 個邏輯單元,容量相當于市場同類最大28nm FPGA 的兩倍。這是賽靈思采用臺積電(TSMC) 28nm HPL工藝推出的第三款FPGA,更重要的是,這也是世界第一個采用堆疊硅片互聯(SSI) 技術的商用FPGA。

Virtex-7 2000T 器件為設備制造商提供了一個集成的平臺,能幫助他們在提升性能和功能的同時降低功耗。由于消除了電路板上不同IC 間的I/O 接口,系統的整體功耗得以顯著降低。同時,因為電路板上需要的IC 器件數量減少,客戶能降低材料清單成本、測試和開發成本。此外, 由于芯片在硅中介層上并排放置,SSI 技術能夠避免多個芯片堆疊造成的功耗和可靠性問題。中介層在每個芯片間提供10,000 多個高速互聯,可支持各種應用所需要的高性能集成。

超越摩爾定律,引領FPGA發展新潮流

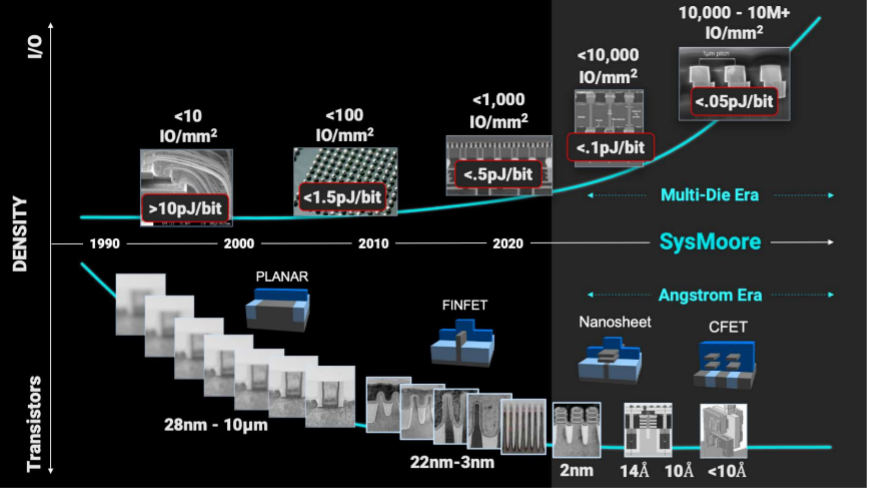

傳統上,FPGA 廠商習慣于采用最新芯片工藝技術來實現他們的新架構,充分發揮摩爾定律的作用,這樣晶體管的數量每22 個月就能隨最新芯片工藝技術的推出而翻一番。過去20 年,FPGA 廠商一直遵循摩爾定律的發展,不斷推出新的FPGA,實現器件容量的倍增。

賽靈思公司全球高級副總裁,亞太區執行總裁湯立人(Vincent Tong)指出:

根據摩爾定律,FPGA做不到200萬的邏輯單元,28nm最大也只可以達到大概100萬邏輯單元,但是由于堆疊互聯技術,我們可以達到200萬邏輯單元,并且,最重要的是我們現在就可以供貨,客戶可以馬上著手如此高性能FPGA的設計。在半導體行業最大的CPU能達到30億左右。而2000T是半導體歷史上最大的半導體,有200萬的邏輯單元,沒有其他的FPGA,也沒有其他的半導體可以做到那么大的容量。

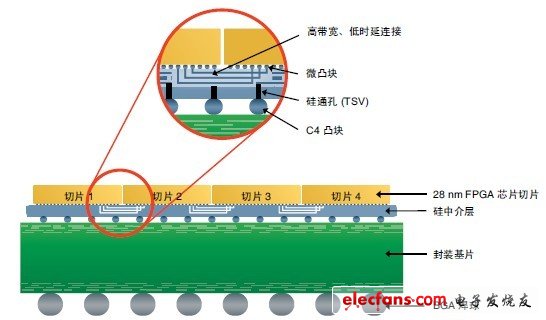

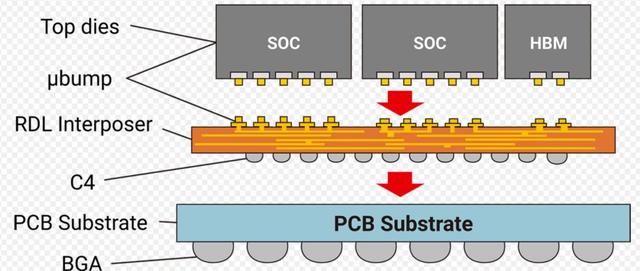

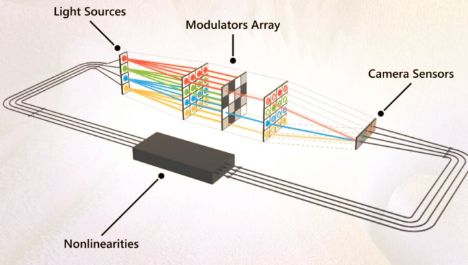

針對Virtex-7 2000T,賽靈思打造了堆疊硅片互聯(SSI) 技術。該技術在無源硅中介層上并排連接著幾個硅切片(有源切片),該切片再由穿過該中介層的金屬連接,與印制電路板上不同IC 通過金屬互聯通信的方式類似。通過這種技術,賽靈思讓器件的發展步伐超過了摩爾定律的速度,使賽靈思站在了28nm FPGA的頂端,引領著FPGA行業的發展。

賽靈思堆疊硅片互聯(SSI)技術

為了克服限制和障礙,賽靈思已經開發出一種新的方法來實現大容量FPGA 的批量生產,那就是堆疊硅片互聯技術。該新型解決方案能夠大量增加連接的數量,實現多個芯片間的高帶寬連接。與多個FPGA 方法相比,還能顯著降低時延和功耗,同時能在單個封裝中集成大量互聯邏輯和片上資源。

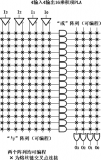

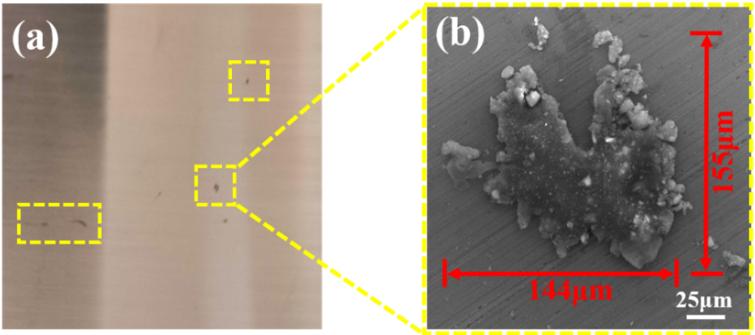

在FPGA 系列的密度范圍內,中密度器件是“最佳選擇”。這是因為與前代器件相比,同一芯片尺寸上的容量和帶寬有顯著提升,而與同一系列中的最大型器件相比,它們能夠在FPGA 產品生命周期的早期階段就可以交付。因此,通過將多個這種芯片集成到單個器件內,就可以達到并超過最大型單片器件所提供的容量和帶寬,但同時又具有小型芯片的生產優勢和即時量產優勢。賽靈思用一種創新方式將多種業經驗證的技術進行優化組合實現了該解決方案。通過將硅通孔(TSV) 和微凸塊技術與其創新型ASMBLTM 架構完美組合,賽靈思正在構建新系列FPGA 產品,其容量、性能、功能和功耗特性足以應對“可編程技術勢在必行”這一發展趨勢。圖1 是由4 個FPGA 芯片切片、硅中介層和封裝基片構成的堆疊芯片頂視圖。賽靈思利用堆疊硅片互聯技術將增強型FPGA 芯片切片與無源硅中介層相集成,所開發出的堆疊芯片實現了成千上萬條芯片間連接,能夠提供超高芯片間互聯帶寬,功耗顯著下降,且時延僅為標準I/O 的五分之一。

2.5D和3D堆疊技術的發展和意義

說到2.5D和3D可能大家都不陌生,賽靈思是全球第一家公司可以做到2.5D堆疊技術的,不僅僅對于賽靈思來說,對整個行業來說,2.5D在FPGA行業中扮演什么角色呢?3D是非常尖端的技術,3D是什么意思呢?湯立人(Vincent Tong)解釋到3D是把不同的IC堆疊在一起。兩個都是IC,都有晶體管在里面。每個IC都是主動的,有功耗,需要電源的。為什么現在變成2.5D呢?2.5D定義就是這兩個主動IC放到被動的介質上。下面有連接,把兩個主動IC連接起來。因為是被動不需要電源,沒有晶體管在里面,因而具有獨特的功耗優勢,也是我們說的SSI——堆疊硅片互聯技術。

現在這個行業要做2.5D,為什么從3D變成2.5D呢?因為現在3D面臨非常多挑戰,主要有3點:首先,3D是垂直的堆疊,把兩個主動IC用微凸快(micropum)連在一起,微凸快是一種新興技術,中間有非常多的挑戰。兩個硅片之間有應力。舉例來說,兩個芯片本身的膨脹系數有可能不一樣,中間連接的micropump受到的壓力就很大,一個膨脹快,一個膨脹慢,應力就比較大。第二,硅通孔(TSV)有應力在,會影響周圍晶體管的性能。如果從上面開到下面,應力非常大,會影響晶體管性能,是整個行業需要面對的問題。第三,熱管理,如果兩個都是主動的IC,散熱就成為很大的問題。所以整個3D行業需要解決上面三個主要問題。

賽靈思在整個行業是具有領導地位的,很多人認為,現在我們做2.5D,2.5D是不是3D中間的過渡技術?我們認為不是。2.5D會一直走下去的,2.5D有自己的應用,不一定被3D所代替,2.5D有自己的路要走,所以我們選擇做2.5D。

賽靈思亞太區銷售及市場總監張宇清(左),賽靈思公司全球高級副總裁,亞太區執行總裁湯立人(Vincent Tong)(中),賽靈思公司產品市場營銷總監Brent Przybus(右)

賽靈思亞太區銷售及市場總監張宇清表示:2.5D還是很重大的跨越,雖然我們同時給大家介紹了現在賽靈思能夠做到的技術和未來的3D技術。大家都覺得還是3D好,一定是未來的比較好。現在2.5D比傳統的多芯片MCM封裝有很大超越了,因為多芯片封裝延時更長,必須要通過金屬線,傳統多核CPU是多芯片的封裝,要消耗很多IO資源。

總結

作為唯一一家采用堆疊硅片互聯技術創造出擁有無以倫比的芯片間帶寬的超高容量FPGA 的制造商,賽靈思在系統級集成領域實現了新的重大突破。堆疊硅片互聯技術使賽靈思的每個工藝節點都能實現最大的邏輯密度、最高的帶寬和最豐富的片上資源,并以最快的速度投入量產。相信摩爾定律的超越一定會給整個FPGA產業帶來翻天覆地的變化,讓我們來期待吧。

?

電子發燒友App

電子發燒友App

評論