文章來源“先進制程貼近物理極限,算力需求Chiplet迎來黃金發展期(精華)”,AI精華系列報告:AMD發布MI300,指引Chiplet等AI芯片新方向,研究機構IBS 統計對比16nm至3nm 的單位數量的晶體管成本指出,隨著制程工藝 的推進,單位數量的晶體管成本的下降幅度在急劇降低。比如從 16nm 到 10nm,每 10 億顆晶 體管的成本降低了 23.5%,而從 5nm 到 3nm 成本僅下降了 4%。 隨著先進制程持續推進,單位晶體管所需要付出的成本降低的速度正在持續放緩,即意味著摩爾定律正在放緩。Chiplet 誕生背景是在摩爾定律放緩。

1、Chiplet 在成本、良率、設計靈活性等方面優勢明顯

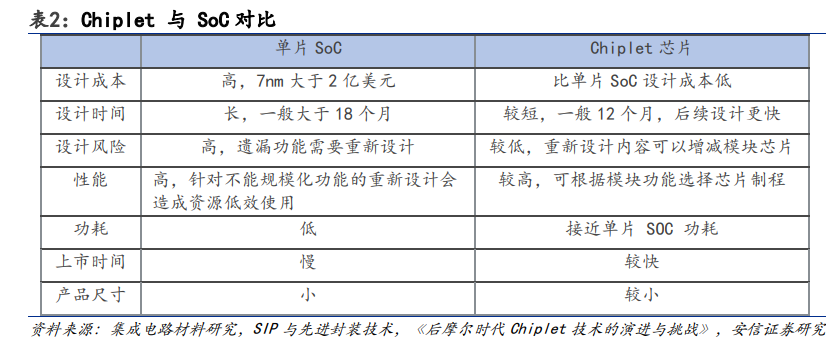

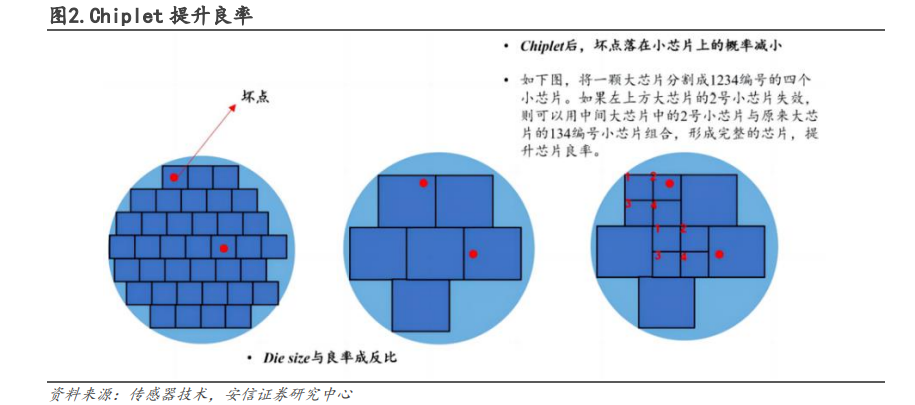

Chiplet 俗稱“芯粒”或“小芯片組”,通過將原來集成于同一 SoC 中的各個元件分拆,獨立 為多個具特定功能的 Chiplet,分開制造后再通過先進封裝技術將彼此互聯,最終集成封裝 為一個系統芯片。 由于Chiplet芯粒可以獨立設計和組裝,因此制造商可以根據自己的需要來選擇不同類型、不同規格和不同供應商的芯粒進 行組合,很大程度上提高了芯片設計的靈活性和可定制化程度;并且制造商可以依賴于預定 好的芯片工具箱來設計新產品,縮短芯片的上市時間。同時,Chiplet 技術可以將 大型 7nm 設計的成本降低高達 25%;在 5nm 及以下的情況下,節省的成本更大。

Chiplet 技術被視為“異構”技術的焦點,也是當下最被企業所認可的新型技術之一。2022 年 3 月,英特爾、AMD、Arm、高通、三星、臺積電、日月光、Google Cloud、Meta、微軟等 全球領先的芯片廠商共同成立了 UCIe 聯盟,旨在建立統一的 die-to-die 互聯標準,促進 Chiplet 模式的應用發展,目前聯盟成員已有超過 80 家半導體企業,越來越多的企業開始研 發 Chiplet 相關產品。

2、Chiplet市場規模快速成長

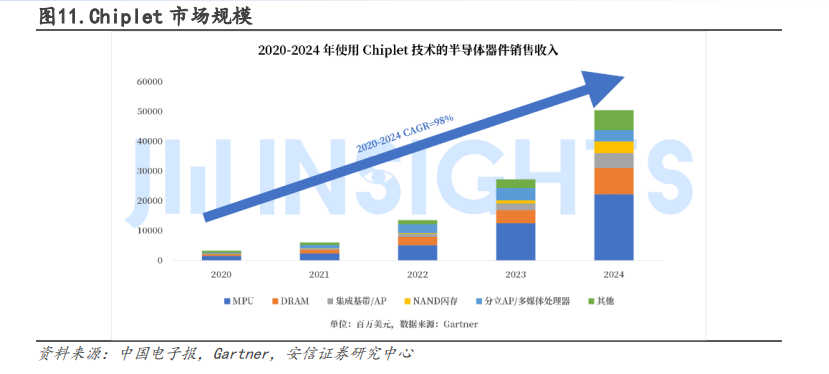

根據 Gartner 數據統計,基于 Chiplet 的半導體器件銷售收入在 2020 年僅為 33 億美元, 2022 年已超過 100 億美元,預計 2023 年將超過 250 億美元,2024 年將達到 505 億美元,復 合年增長率高達 98%。超過 30%的 SiP 封裝將使用芯粒(Chiplet)來優化成本、性能和上市 時間。

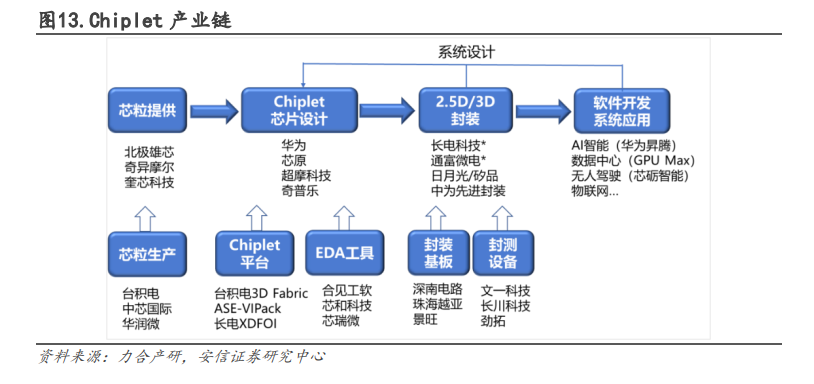

MPU 占據 Chiplet 大部分應用應用場景,Omdia 預測 2024 年用于 MPU 的 Chiplet 約占 Chiplet 總市場規模的 43%。 隨著 Chiplet 技術的發展, Chiplet 產業鏈各環節逐漸完善,即由 Chiplet 系統級設計、EDA/IP、芯粒(核心、非核心、 IO Die、Base Die)、制造、封測組成的完整 Chiplet 生態鏈。

Chiplet 產業鏈主鏈有四大環節,包括芯粒、芯片設計、封裝生產和系統應用,支撐環節包 括芯粒生產、設計平臺、EDA 工具、封裝基板、封測設備等領域。

3、IC 制造及封測廠加碼布局 Chiplet

目前全球封裝技術主要由臺積電、三星、Intel 等公司主導,主要是 2.5D 和 3D 封裝。2.5D 封裝技術已非常成熟,廣泛應用于 FPGA、CPU、GPU 等芯片,目前是 Chiplet 架構產品主要的 封裝解決方案。3D 封裝能夠幫助實現 3D IC,即晶粒間的堆疊和高密度互連,可以提供更為 靈活的設計選擇。但 3D 封裝的技術難度更高,目前主要有英特爾和臺積電掌握 3D 封裝技術 并商用。臺積電比三星、英特爾更早采用 Chiplet 的封裝方式。

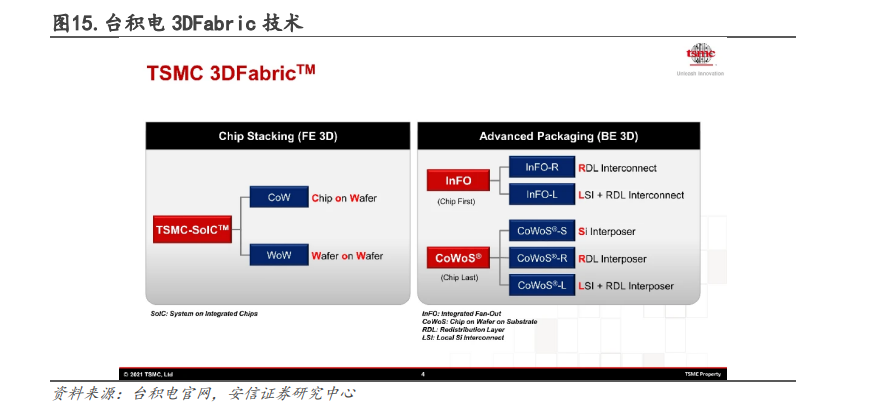

1)、臺積電3DFabric封裝技術

臺積電推出了3D Fabric,搭載了完備的3D硅堆棧(3D Silicon Stacking)和先進的封裝技術。3DFabric 是由臺積電前端 3D 硅 堆棧技術 TSMC SoIC 系統整合的芯片,由基板晶圓上封裝(Chip on Wafer on Substrate, CoWoS)與整合型扇出(Integrated Fan-Out, InFO)的后端 3D 導線連接技術所組成,能夠 為客戶提供整合異質小芯片(Chiplet)的彈性解決方案。該項技術先后被用于賽靈思的 FPGA、 英偉達的 GPU 以及 AMD 的 CPU。

2)、Intel2.5D 封裝技術EMIB

Intel主導的 2.5D 封裝技術為 EMIB,使用多個嵌入式包含多個路由層的橋接芯片,同時內 嵌至封裝基板,達到高效和高密度的封裝。由于不再使用 interposer 作為中間介質,可以去 掉原有連接至 interposer 所需要的 TSV,以及由于 interposer 尺寸所帶來的封裝尺寸的限制,可以獲得更好的靈活性和更高的集成度。 相較于 MCM 和 CoWoS 技術,EMIB 技術獲得更高 的集成度和制造良率。英特爾對各種先進封裝產品組合 (如 Foveros、EMIB 和 Co-EMIB) 的 投資是實施公司新領導層所公布的 IDM2.0 戰略的關鍵。

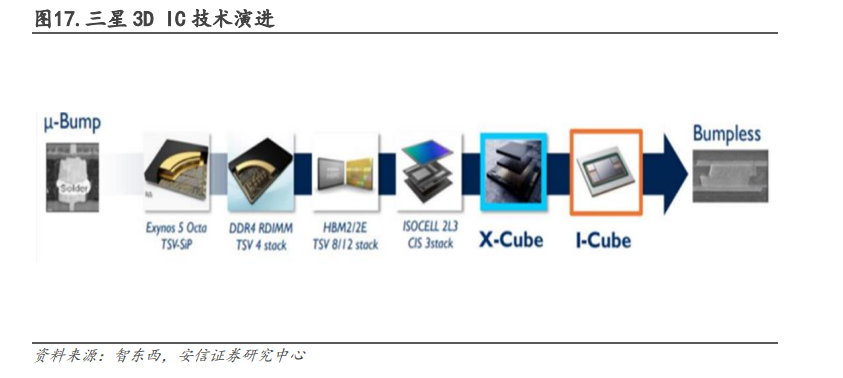

3)、三星公X Cube 3D封裝技術

三星也在積極投資先進的封裝技術,以滿足 HPC 應用在異質芯片整合的快速發展。2020 年 8 月,三星公布了 X Cube 3D 封裝技術。在芯片互連方面,使用成熟的硅通孔 TSV 工藝。目前 X Cube 能把 SRAM 芯片堆疊在三星生產的 7nm EUV 工藝的邏輯芯片上,在更易于擴展 SRAM 容 量的同時也縮短了信號連接距離,提升了數據傳輸的速度。此后發布的 I-Cube 可以將一個 或多個邏輯Die 和多個 HBM die 水平放置在硅中介層,進行異構集成。

4)、日月光FOCoS先進封裝技術

日月光憑借在 FOCoS 先進封裝技術的布局,是目前在封測代工廠中唯一擁有超高密度扇出解 決方案的供應商。日月光的 FOCoS 提供了一種用于實現小芯片集成的硅橋技術,稱為 FOCoSB(橋),它利用帶有路由層的微小硅片作為小芯片之間的封裝內互連,例如圖形計算芯片 (GPU)和高帶寬內存(HBM)。硅橋嵌入在扇出 RDL 層中,是一種可以不使用硅中介層的 2.5D 封 裝方案。與使用硅中介層的 2.5D 封裝相比,FOCoS-B 的優勢在于只需要將兩個小芯片連接在 一起的區域使用硅片,可大幅降低成本。

5)、長電科技2.5D TSV-less封裝技術

長電科技推出的面向Chiplet小芯片的高密度多維異構集成技術平臺 XDFOI可實現 TSV-less 技術,達到性能和成本的雙重優勢,重點應用領域為高性能運算如 FPGA、5G、自動駕駛、智能醫療等。XDFOI是一種以 2.5D TSV-less 為基本技術平臺的封裝技術, 在線寬/線距可達到 2μm/2μm 的同時,還可以實現多層布線層,以及 2D/2.5D 和 3D 多種異 構封裝,能夠提供小芯片(Chiplet)及異構封裝的系統封裝解決方案。目前長電先進 XDFOI 2.5D 試驗線已建設完成,并進入穩定量產階段,同步實現國際客戶 4nm 節點多芯片系統集成 封裝產品出貨。

-

摩爾定律

+關注

關注

4文章

635瀏覽量

79095 -

封裝技術

+關注

關注

12文章

550瀏覽量

67998 -

chiplet

+關注

關注

6文章

434瀏覽量

12606

原文標題:Chiplet技術:即具備先進性,又續命摩爾定律

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

摩爾定律是什么 影響了我們哪些方面

Chiplet在先進封裝中的重要性

后摩爾定律時代,提升集成芯片系統化能力的有效途徑有哪些?

高算力AI芯片主張“超越摩爾”,Chiplet與先進封裝技術迎百家爭鳴時代

國產半導體新希望:Chiplet技術助力“彎道超車”!

創新型Chiplet異構集成模式,為不同場景提供低成本、高靈活解決方案

“自我實現的預言”摩爾定律,如何繼續引領創新

封裝技術會成為摩爾定律的未來嗎?

易卜半導體創新推出Chiplet封裝技術,彌補國內技術空白,助力高算力芯片發展

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

Chiplet技術對英特爾和臺積電有哪些影響呢?

Chiplet技術:即具備先進性,又續命摩爾定律

Chiplet技術:即具備先進性,又續命摩爾定律

評論