摘要:在消費類產品小型化和更輕、更薄發展趨勢的推動下,廠商開發了更小的封裝類型。實際上,封裝已經成為新設計中選擇還是放棄某一器件的關鍵因素。本文首先定義了“倒裝芯片”和“晶片級封裝”兩個名詞,介紹晶片級封裝(WLP)技術的開發。然后,討論使用晶片級封裝器件的實際情況。討論主題包括:如何確定某一器件能否使用倒裝芯片/UCSP?封裝;通過標識識別倒裝芯片/UCSP;晶片級封裝的可靠性;查找適用的可靠性信息。在本文總結部分,展望了今后的封裝技術發展,列出本應用筆記的參考文獻以及本文沒有討論的某些主題和相關資料鏈接等。

晶片級封裝的概念起源于1990年,在1998年定義的CSP分類中,晶片級CSP是多種應用的一種低成本選擇,這些應用包括EEPROM等引腳數量較少的器件,以及ASIC和微處理器等。CSP采用稱為晶片級封裝(WLP)的工藝進行加工,WLP的主要優點是所有裝配和測試都在晶片上進行。隨著晶片尺寸的增大、管芯的縮小,WLP的成本不斷降低。作為最早采用該技術的公司, Dallas Semiconductor在1999年便開始銷售晶片級封裝產品。

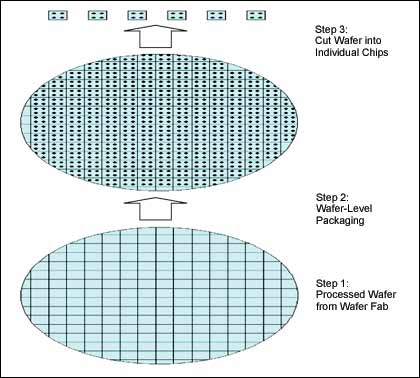

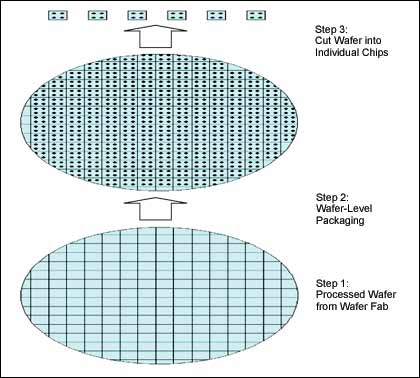

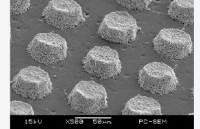

圖1. 晶片級封裝(簡圖)最終將每個芯片從處理過的晶片上分離出來。

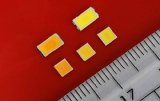

圖2. 12焊球晶片級封裝,3 x 4焊球,2個空焊球位置

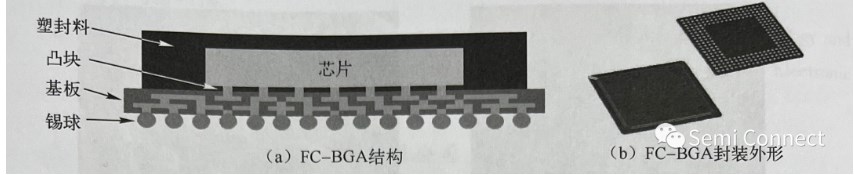

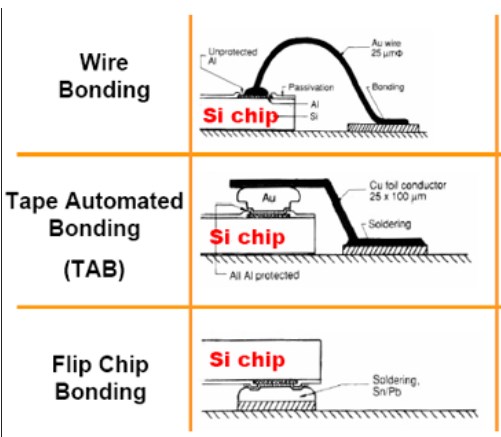

對于Maxim?/Dallas Semiconductor,“倒裝芯片”和“晶片級封裝”最初是所有晶片級封裝的同義詞。過去幾年中,封裝有了進一步的細分。在本文檔以及所有Maxim資料中,包括公司網站,“倒裝芯片”是指焊球具有任意形狀、可放在任何位置的晶片級封裝管芯(邊沿有空隙)。 “晶片級封裝”是指在間隔規定好的柵格上有焊球的晶片級封裝管芯。圖3解釋了這些不同,注意,并不是所有柵格位置都要有焊球。

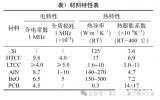

圖3中的倒裝芯片尺寸反映了第一代Dallas Semiconductor的WLP產品;晶片級封裝尺寸來自各個供應商,包括Maxim。目前,Maxim和Dallas Semiconductor推出的新型晶片級封裝產品的關鍵尺寸列在表1中。

圖3. 圖中顯示了晶片級封裝和倒裝芯片封裝的典型尺寸以及區別。

表1. Maxim和Dallas Semiconductor UCSP (晶片級封裝)的標稱尺寸7

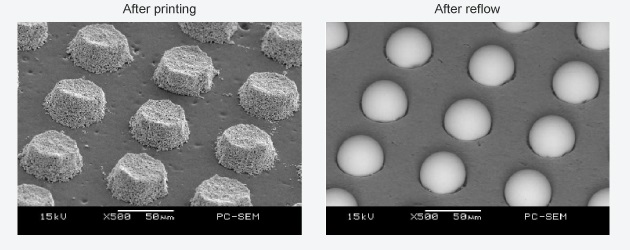

在電路/配線板上將芯片和走線連接在一起的焊球最初采用了錫鉛共晶*合金(Sn63Pb37)。為了減少電子產品中的有害物質(RoHS),半導體行業不得不采用替代材料,例如無鉛焊球(Sn96.5Ag3Cu0.5)或者高鉛焊球(Pb95Sn5)。每種合金都有自己的熔點,因此,在元件組裝回流焊工藝中,溫度曲線比較特殊 (在特定溫度上保持一段時間)。

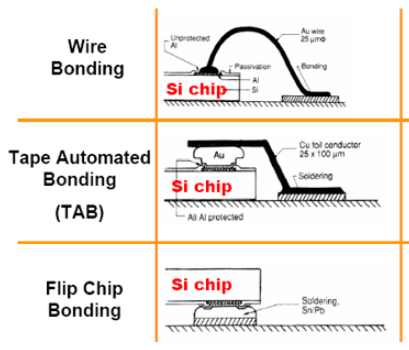

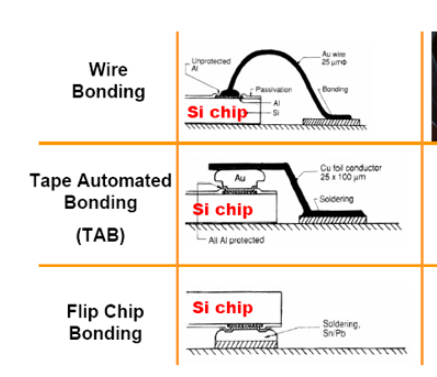

集成電路的目的在于提供系統需要的全部電子功能,并能夠裝配到特定封裝中。芯片上的鍵合焊盤通過線鍵合連接至普通封裝的引腳上。普通封裝的設計規則要求鍵合焊盤位于芯片周界上。為避免同一芯片出現兩種設計(一種是普通封裝,一種是CSP),需要重新分配層來連接焊球和鍵合焊盤。

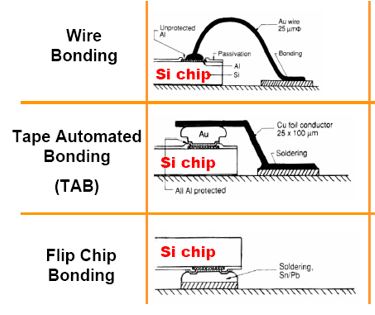

圖4. 倒裝芯片和UCSP標識模板

可以在快速瀏覽頁的更多信息部分了解UCSP的頂標代碼。某些情況下,數據資料中也有這些信息。對于反向查找,例如,從頂標確定器件的封裝,可以使用網站上的頂標代碼功能或下載完整的頂標表13,利用搜索功能識別相應器件。頂標代碼用于包含12個焊球的UCSP。更大的UCSP有足夠的空間打上全部型號以及日期代碼等詳細信息。表2所示為Maxim器件使用的商標。

表2. 典型的Maxim UCSP商標

表3中的商標類型也適用于Dallas Semiconductor的倒裝芯片和UCSP。激光標識非常小,需要放大鏡才能看清楚。Dallas Semiconductor的倒裝芯片對最小器件采用類似方法,2位器件代碼(也稱為系列碼)之后是管芯的版本號,這一方法不需要交叉參考列表。

表3. 典型的Dallas Semiconductor的倒裝芯片和UCSP商標

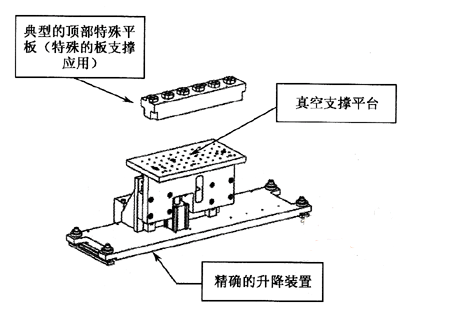

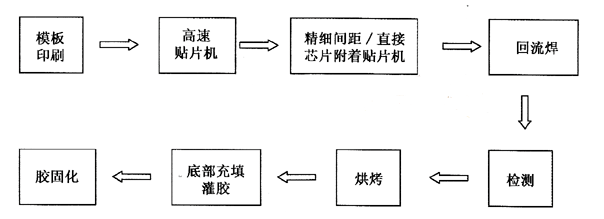

機械壓力性能對WLP而言是較大的問題,倒裝芯片和UCSP直接焊接后,與用戶的PCB連接,從而緩解了封裝產品鉛結構的內部壓力。因此,必須考慮焊接觸點的完整性。Dallas Semiconductor的晶片級封裝裝配指南14提供電路板布板考慮、裝配工藝流程、焊接層絲網印刷、元件布局、回流焊溫度曲線要求、環氧封裝以及視覺檢測標準等方面的詳細信息。應用筆記189115介紹了Maxim的限定規格和測試數據的詳細信息。快速瀏覽頁提供Maxim器件的可靠性信息;公司網站提供Dallas Semiconductor器件的可靠性報告,見表4。

表4. Dallas Semiconductor倒裝芯片和UCSP的可靠性報告

參考

引言

半導體技術的進步大大提高了芯片中的晶體管數量和功能,這一集成規模在幾年前還無法想象。現在我們認識到,如果沒有IC封裝技術同樣令人振奮的發展,也不可能實現便攜式電子產品的設計。在消費類產品小型化和更輕、更薄發展趨勢的推動下,廠商開發了更小的封裝類型。最小的封裝當然是芯片本身,圖1描述了IC從晶片到單個芯片的實現過程,圖2是一個實際的晶片級封裝(CSP)。晶片級封裝的概念起源于1990年,在1998年定義的CSP分類中,晶片級CSP是多種應用的一種低成本選擇,這些應用包括EEPROM等引腳數量較少的器件,以及ASIC和微處理器等。CSP采用稱為晶片級封裝(WLP)的工藝進行加工,WLP的主要優點是所有裝配和測試都在晶片上進行。隨著晶片尺寸的增大、管芯的縮小,WLP的成本不斷降低。作為最早采用該技術的公司, Dallas Semiconductor在1999年便開始銷售晶片級封裝產品。

圖1. 晶片級封裝(簡圖)最終將每個芯片從處理過的晶片上分離出來。

圖2. 12焊球晶片級封裝,3 x 4焊球,2個空焊球位置

命名規則

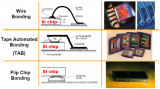

業界在WLP的命名上還有分歧。CSP晶片級技術非常獨特,封裝內部并沒有采用鍵合方式。封裝芯片的命名也有分歧。常用名稱有:倒裝芯片(STMicroelectronics和Dallas Semiconductor?)、CSP、晶片級封裝、WLCSP、WL-CSP、MicroSMD (National Semiconductor)、UCSP (Maxim Integrated Products)、凸起管芯以及MicroCSP (Analog Devices)等。對于Maxim?/Dallas Semiconductor,“倒裝芯片”和“晶片級封裝”最初是所有晶片級封裝的同義詞。過去幾年中,封裝有了進一步的細分。在本文檔以及所有Maxim資料中,包括公司網站,“倒裝芯片”是指焊球具有任意形狀、可放在任何位置的晶片級封裝管芯(邊沿有空隙)。 “晶片級封裝”是指在間隔規定好的柵格上有焊球的晶片級封裝管芯。圖3解釋了這些不同,注意,并不是所有柵格位置都要有焊球。

圖3中的倒裝芯片尺寸反映了第一代Dallas Semiconductor的WLP產品;晶片級封裝尺寸來自各個供應商,包括Maxim。目前,Maxim和Dallas Semiconductor推出的新型晶片級封裝產品的關鍵尺寸列在表1中。

圖3. 圖中顯示了晶片級封裝和倒裝芯片封裝的典型尺寸以及區別。

表1. Maxim和Dallas Semiconductor UCSP (晶片級封裝)的標稱尺寸7

| Parameter | Designator | Value |

| No. of Bumps | (---) | 4 to 36 |

| Bump Diameter | b | 0.30, 0.35mm |

| Bump Height | A1 | 0.25, 0.3mm |

| Bump Pitch | e | 0.5mm |

| Die Thickness | A2 | 0.33, 0.38mm |

晶片級封裝(WLP)技術

提供WLP器件的供應商要么有自己的WLP生產線,要么外包封裝工藝。各種各樣的生產工藝必須能夠滿足用戶的要求,以確保最終產品的可靠性。Wafer-Level Packaging Has Arrived 8、The Wafer-Level Packaging Evolution9、WLCSP Technology Direction 10等文章生動地介紹了WLP的過去和未來。美國亞利桑那州鳳凰城的FCI、美國北卡羅萊納州的Unitive?建立了WLP技術標準,產品名為UltraCSP (FCI)和Xtreme (Unitive)。Amkor在并購了Unitive后,為全世界半導體行業提供WLP服務11。在電路/配線板上將芯片和走線連接在一起的焊球最初采用了錫鉛共晶*合金(Sn63Pb37)。為了減少電子產品中的有害物質(RoHS),半導體行業不得不采用替代材料,例如無鉛焊球(Sn96.5Ag3Cu0.5)或者高鉛焊球(Pb95Sn5)。每種合金都有自己的熔點,因此,在元件組裝回流焊工藝中,溫度曲線比較特殊 (在特定溫度上保持一段時間)。

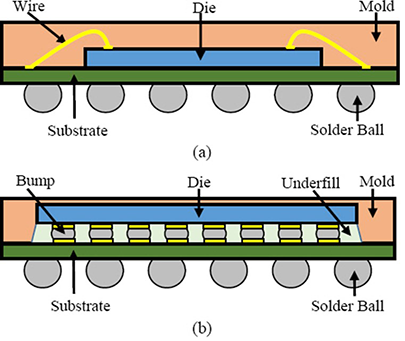

集成電路的目的在于提供系統需要的全部電子功能,并能夠裝配到特定封裝中。芯片上的鍵合焊盤通過線鍵合連接至普通封裝的引腳上。普通封裝的設計規則要求鍵合焊盤位于芯片周界上。為避免同一芯片出現兩種設計(一種是普通封裝,一種是CSP),需要重新分配層來連接焊球和鍵合焊盤。

確定倒裝芯片/UCSP的可行性,符合無鉛要求

Maxim/Dallas Semiconductor只有一小部分器件采用了倒裝芯片或UCSP。識別封裝最簡單的方法是利用公司網站上的器件快速瀏覽網頁。進行型號搜索后,會顯示數據資料的快速瀏覽頁,它包括器件的簡要說明、關鍵特性、封裝選擇以及應用筆記的URL和詳細信息的鏈接(例如,可靠性報告、評估套件)等。在快速瀏覽頁的右上角可以找到型號的數據資料,如果多個型號使用同一份數據資料,型號表上有下拉框選擇特定的型號。點擊Go,打開一個窗口,顯示定購型號、封裝說明、封裝外形的URL、溫度范圍以及封裝是否無鉛等。查找FCHIP或UCSP,Dallas Semiconductor器件的倒裝芯片/UCSP標識符是“X”。Maxim UCSP一般使用后綴“B”,隨后是型號的數字部分12。型號表中的封裝外形總是含有定位標識,由于UCSP外形用于管芯大小不同的多種器件,因此,沒有包括焊球的電配置參數,這些信息在器件的數據資料中提供。而倒裝芯片外形只用于特定芯片,因此,其外形一般包括電配置參數。倒裝芯片/UCSP頂標(器件標識)

與塑料封裝常用的方式不同,大部分倒裝芯片和UCSP沒有給標準標識方式留有足夠的空間。最小的UCSP (4個焊球)只有足夠的定位標識和兩行6字符代碼的空間。定位標識還表明封裝是“標準”(共晶焊球)、高鉛(#)還是無鉛(+),見圖4。

圖4. 倒裝芯片和UCSP標識模板

可以在快速瀏覽頁的更多信息部分了解UCSP的頂標代碼。某些情況下,數據資料中也有這些信息。對于反向查找,例如,從頂標確定器件的封裝,可以使用網站上的頂標代碼功能或下載完整的頂標表13,利用搜索功能識別相應器件。頂標代碼用于包含12個焊球的UCSP。更大的UCSP有足夠的空間打上全部型號以及日期代碼等詳細信息。表2所示為Maxim器件使用的商標。

表2. 典型的Maxim UCSP商標

| Maxim Brand | Legend | ||||||||||||||||

|

| ||||||||||||||||

| |||||||||||||||||

| |||||||||||||||||

| |||||||||||||||||

|

表3中的商標類型也適用于Dallas Semiconductor的倒裝芯片和UCSP。激光標識非常小,需要放大鏡才能看清楚。Dallas Semiconductor的倒裝芯片對最小器件采用類似方法,2位器件代碼(也稱為系列碼)之后是管芯的版本號,這一方法不需要交叉參考列表。

表3. 典型的Dallas Semiconductor的倒裝芯片和UCSP商標

| Dallas Semiconductor Brand | Legend | ||||||||||||||

|

| ||||||||||||||

| |||||||||||||||

|

晶片級封裝器件的可靠性

晶片級封裝(倒裝芯片和UCSP)代表一種獨特的封裝外形,它和利用傳統的機械可靠性測試的封裝產品有所不同。封裝的可靠性主要和用戶的裝配方法、電路板材料以及使用環境有關。用戶在考慮使用WLP型號時應認真考慮這些問題。必須進行工作壽命測試和抗潮濕性能測試,這些性能主要由晶片制造工藝決定。機械壓力性能對WLP而言是較大的問題,倒裝芯片和UCSP直接焊接后,與用戶的PCB連接,從而緩解了封裝產品鉛結構的內部壓力。因此,必須考慮焊接觸點的完整性。Dallas Semiconductor的晶片級封裝裝配指南14提供電路板布板考慮、裝配工藝流程、焊接層絲網印刷、元件布局、回流焊溫度曲線要求、環氧封裝以及視覺檢測標準等方面的詳細信息。應用筆記189115介紹了Maxim的限定規格和測試數據的詳細信息。快速瀏覽頁提供Maxim器件的可靠性信息;公司網站提供Dallas Semiconductor器件的可靠性報告,見表4。

表4. Dallas Semiconductor倒裝芯片和UCSP的可靠性報告

| Device | Applicable Reliability Reports with URL |

| DS2431 | http://www.maxim-ic.com/reliability/dallas/Dallas-8in_CSP20_RDL_3x3.pdf |

| DS2401 | http://www.maxim-ic.com/reliability/dallas/DS2401.pdf http://www.maxim-ic.com/reliability/dallas/Dallas_Backgrind_FC-RDL.pdf |

| DS28E01 | http://www.maxim-ic.com/reliability/dallas/Dallas-8in_CSP20_RDL_3x3.pdf |

| DS1804 | http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20underfill.pdf http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20w-redistribution%20underfill.pdf |

| DS1845 | http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20underfill.pdf http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20w-redistribution%20underfill.pdf |

| DS2406 | http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20underfill.pdf http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20w-redistribution%20underfill.pdf |

| DS2411 | http://www.maxim-ic.com/reliability/dallas/DS2411A1Bump-8in.pdf |

| DS2415 | http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20underfill.pdf http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20w-redistribution%20underfill.pdf |

| DS2417 | http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20underfill.pdf http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20w-redistribution%20underfill.pdf |

| DS2430A | http://www.maxim-ic.com/reliability/dallas/FlipChip_RDL_8in.pdf |

| DS2432 | http://www.maxim-ic.com/reliability/dallas/Dallas-8in_CSP20_RDL_3x3.pdf |

| DS2433 | http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20underfill.pdf http://www.maxim-ic.com/reliability/dallas/Bump%202%20layer%20w-redistribution%20underfill.pdf |

| DS2502 | http://www.maxim-ic.com/reliability/dallas/DS2502Bump.pdf http://www.maxim-ic.com/reliability/dallas/Dallas_Backgrind_FC-RDL.pdf http://www.maxim-ic.com/reliability/dallas/FlipChip_RDL_8in.pdf |

| DS2760 | http://www.maxim-ic.com/reliability/dallas/FlipChip_RDL_8in.pdf |

| DS2761 | http://www.maxim-ic.com/reliability/dallas/FlipChip_RDL_8in.pdf |

| DS2762 | http://www.maxim-ic.com/reliability/dallas/FlipChip_RDL_8in.pdf |

結論

目前的倒裝芯片和CSP還是新技術,處于發展階段。正在改進的措施將采用背面疊片覆層技術(BSL),保護管芯的無源側不受光和機械沖擊的影響,提高激光標識在光照下的可讀性。除了BSL,還會有更小的管芯厚度,保持裝配總高度不變。Maxim UCSP尺寸(參見表1)說明了2007年2月產品的封裝狀況。依照業界一般的發展趨勢,這些尺寸有可能進一步減小。因此,設計人員在完成電路板布板之前,應該從各自的封裝外形上確定設計的封裝尺寸,這一點非常關鍵。此外,了解焊球管芯WLP合金的組成也很重要,特別是器件沒有聲明或標記為無鉛產品時。帶有高鉛焊球(Pb95Sn5)的某些器件通過了無鉛電路板裝配回流焊工藝測試,不會顯著影響其可靠性16, 17。采用共晶SnPb焊球的器件需要同類共晶SnPb焊接面,因此,不能用于無鉛裝配環境。參考

- Analog Devices, 應用筆記617 (PDF, 414kB)

- National Semiconductor, 應用筆記1281 (PDF, 225kB)

- National Semiconductor, 應用筆記1412 (PDF, 828kB)

- STMicroelectronics, 應用筆記1235 (PDF, 328kB)

- STMicroelectronics, 應用筆記2348 (PDF, 333kB)

- Maxim Integrated Products, FCHIP封裝圖

- Maxim Integrated Products, UCSP封裝圖

- Dr. Philip Garrou, IEEE Components, Packaging and Manufacturing Technologies Society, Semiconductor International, October 2000, http://www.reed-electronics.com/semiconductor/index.asp?layout=articlePrint&articleID=CA47705

- Michael T?pper, Fraunhofer Institute for Reliability and Microintegration (Fraunhofer-IZM); Philip Garrou, IEEE Components, Packaging and Manufacturing Technology Society, Semiconductor International, 2004年10月, http://www.reed-electronics.com/semiconductor/index.asp?layout=articlePrint&articleID=CA456679

- M. T?pper, V. Glaw, K. Zoschke, O. Ehrmann, H. Reichl, Fraunhofer IZM - TU Berlin Microperipherics Center, Advancing Microelectronics - 2006年1月/2月, http://www.imaps.org/adv_micro/2006jan_feb/2006jan_feb_full.pdf (PDF, 6.73MB)

- Amkor Technology, Wafer Level Packaging Data Sheet (PDF, 164kB)

- Maxim Product命名規則

- Topmark Cross-Reference Table (PDF, 265kB) (200頁以上)

- Maxim晶片級封裝安裝指南

- 晶片級封裝(WL-CSP)封裝基礎

- 采用無鉛(Pb)裝配流程裝配高含鉛的DS2502倒裝芯片

- 在無鉛裝配流程中安裝含鉛的DS2761倒裝芯片

電子發燒友App

電子發燒友App

評論