資料介紹

芯片級封裝介紹本應(yīng)用筆記提供指引使用與PCB安裝設(shè)備相關(guān)的芯片級封裝。包括系統(tǒng)的PCB布局信息制造業(yè)工程師和制造工藝工藝工程師。

“包”概述

倒裝芯片CSP的“包”概述半導(dǎo)體封裝提供的芯片級封裝代表最小的足跡大小,因為包是同樣大小的模具。安森美半導(dǎo)體提供幾種類型CSP。此應(yīng)用筆記只涵蓋那些較大焊料凸點。倒裝芯片CSP凸模創(chuàng)建附加焊料球體到晶片的活性側(cè)的I / O焊盤。這個I/O布局可以是外圍格式,也可以是數(shù)組格式。一分配層可用于路由設(shè)備墊到凹凸墊。焊料凸點允許封裝的兼容性與標(biāo)準(zhǔn)表面貼裝技術(shù)連接選擇并放置和回流過程和標(biāo)準(zhǔn)倒裝芯片安裝系統(tǒng)。倒裝芯片的較大焊料凸點CSP無需底部填充以提高可靠性性能。焊料的鉛?自由但主要共晶SnPb焊料是可用的。較小的凸塊設(shè)計的設(shè)備通常有周邊墊布局和緊縮間距。在這種情況下,底部填充建議提高板級焊料焊點可靠性。

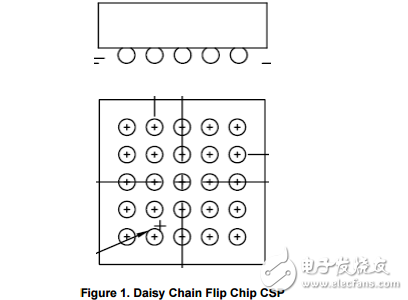

Package Construction and Process Description Flip Chip CSPs are created at the wafer level. Upon completion of standard wafer processing, a polymeric Repassivation layer is applied to the wafer, leaving the bonding pads exposed. In the case where bumps are formed directly over the device bonding pads (Bump on I/O), an under bump metallization (UBM)is applied to the bonding pads to provide an interface between the die pad metallization and the solder bump. The UBM may be a sputtered AlNiVCu thin film or an electroplate Cu. In the case where the solder bumps are offset from the device bonding pads, a plated RDL trace is applied to connect the device bonding pad to the UBM. Solder spheres are placed on each exposed UBM pad and reflowed to create an interconnection system ready for board assembly. Once the bumps are reflowed, wafers are laser marked, electrically tested, sawn into individual die, and packed in tape and reel, bumps down. A typical Flip Chip CSP is represented in Figure 1. Total device thickness varies, depending on customer requirements.

- 先進(jìn)倒裝芯片封裝 8次下載

- 倒裝恒流芯片NU520產(chǎn)品應(yīng)用 0次下載

- 倒裝芯片 CSP 封裝

- 先進(jìn)封裝形式μBGA、CSP的回流焊接技術(shù)說明 4次下載

- 70種電子元器件及芯片封裝類型資源下載 102次下載

- 芯片制造倒裝焊工藝與設(shè)備解決方案 24次下載

- 倒裝芯片凸點制作方法 26次下載

- LED倒裝芯片知識詳解(全) 50次下載

- 支架式倒裝的定義及其與FEMC之間的關(guān)系介紹 9次下載

- 正裝、倒裝、垂直LED芯片結(jié)構(gòu)的介紹及LED倒裝芯片的優(yōu)點 76次下載

- 芯片級封裝器件(CSP)與CSP LED的主流結(jié)構(gòu)介紹 26次下載

- 超級CSP——讓倒裝芯片獲得最大可靠性一種晶圓片級封裝 22次下載

- FC倒裝芯片裝配技術(shù)介紹 46次下載

- 低成本的倒裝芯片封裝技術(shù) 87次下載

- 理解倒裝芯片和晶片級封裝技術(shù)及其應(yīng)用

- 倒裝芯片封裝技術(shù)解析 590次閱讀

- BGA倒裝芯片焊接中的激光植錫球技術(shù)應(yīng)用 741次閱讀

- 倒裝芯片和芯片級封裝的由來 1009次閱讀

- BGA和CSP封裝技術(shù)詳解 2572次閱讀

- 華為具有改進(jìn)的熱性能的倒裝芯片封裝專利解析 829次閱讀

- 先進(jìn)封裝之面板芯片級封裝(PLCSP)簡介 1655次閱讀

- 倒裝芯片尺寸級封裝工藝流程與技術(shù) 3977次閱讀

- led倒裝芯片和正裝芯片差別 2.8w次閱讀

- 倒裝芯片的原理_倒裝芯片的優(yōu)勢 1.2w次閱讀

- 電子元器件電路板的組裝技術(shù)介紹 3916次閱讀

- CSP封裝是什么?具有什么特點 2w次閱讀

- CSP LED封裝技術(shù)會成為主流嗎? 1w次閱讀

- CSP封裝的散熱挑戰(zhàn) 1234次閱讀

- 倒裝cob光源容易損壞么?與正裝COB相比,倒裝COB有何優(yōu)勢? 2w次閱讀

- 什么是CSP封裝,CSP封裝量產(chǎn)測試的問題及解決方案研究 8050次閱讀

下載排行

本周

- 1PIC16F716 數(shù)據(jù)手冊免費下載

- 2.35 MB | 18次下載 | 5 積分

- 2AN158 GD32VW553 Wi-Fi開發(fā)指南

- 1.51MB | 2次下載 | 免費

- 3模擬電路仿真實現(xiàn)

- 2.94MB | 2次下載 | 免費

- 4AN148 GD32VW553射頻硬件開發(fā)指南

- 2.07MB | 1次下載 | 免費

- 5PZT驅(qū)動開關(guān)電路

- 0.09 MB | 1次下載 | 免費

- 6PCB繪制基礎(chǔ)知識

- 2.44MB | 1次下載 | 免費

- 7電子線路板及仿真實現(xiàn)

- 1.54MB | 1次下載 | 免費

- 8AN4873-使用PIC單片機(jī)的集成運算放大器測量水中的總?cè)芙夤腆w

- 591.02KB | 1次下載 | 免費

本月

- 1ADI高性能電源管理解決方案

- 2.43 MB | 452次下載 | 免費

- 2免費開源CC3D飛控資料(電路圖&PCB源文件、BOM、

- 5.67 MB | 139次下載 | 1 積分

- 3基于STM32單片機(jī)智能手環(huán)心率計步器體溫顯示設(shè)計

- 0.10 MB | 133次下載 | 免費

- 4美的電磁爐維修手冊大全

- 1.56 MB | 24次下載 | 5 積分

- 5如何正確測試電源的紋波

- 0.36 MB | 19次下載 | 免費

- 6PIC16F716 數(shù)據(jù)手冊免費下載

- 2.35 MB | 18次下載 | 5 積分

- 7萬用表UT58A原理圖

- 0.09 MB | 9次下載 | 5 積分

- 8Q/SQR E8-4-2024乘用車電子電器零部件及子系統(tǒng)EMC試驗方法及要求

- 1.97 MB | 8次下載 | 10 積分

總榜

- 1matlab軟件下載入口

- 未知 | 935121次下載 | 10 積分

- 2開源硬件-PMP21529.1-4 開關(guān)降壓/升壓雙向直流/直流轉(zhuǎn)換器 PCB layout 設(shè)計

- 1.48MB | 420062次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233088次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費下載

- 340992 | 191367次下載 | 10 積分

- 5十天學(xué)會AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183335次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81581次下載 | 10 積分

- 7Keil工具M(jìn)DK-Arm免費下載

- 0.02 MB | 73810次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65988次下載 | 10 積分

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論