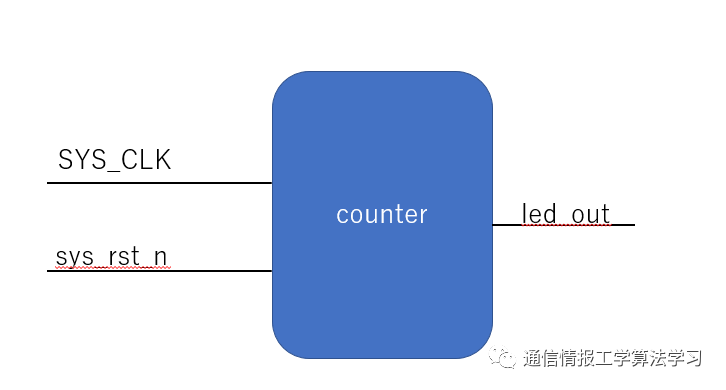

第二十七講 同步時序邏輯電路的設計

7.5 同步時序邏輯電路的設計

用SSI觸發器

16進制以內

7.5.1 同步時序邏輯電路的設計方法

設計關鍵:

設計步驟:

1.根據設計要求,設定狀態,畫出狀態轉換圖。

2.狀態化簡

3.狀態分配,列出狀態轉換編碼表

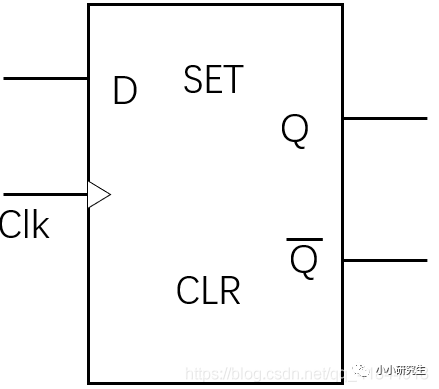

4.選擇觸發器的類型,求出狀態方程、驅動方程、輸出方程

5.根據驅動方程和輸出方程畫邏輯圖。

6.檢查電路有無自啟動能力

7.5.2 同步時序邏輯電路的設計舉例

[例7.5.1] 試設計一個同步七進制加法計數器。

按設計步驟進行

[例7.5.2] 設計一個脈沖序列為10100的序列脈沖發生器。

按設計步驟進行

思考:若設計異步時序電路,與同步時序電路應有何不同?

.5 同步時序邏輯電路的設計

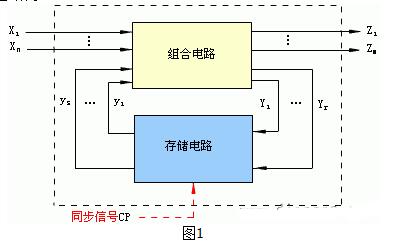

設計:根據給定邏輯功能的要求,設計出能滿足要求的同步時序邏輯電路。

和分析正好相反,因此先回憶同步時序電路的分析,已經學習過的知識點就可以略講,而強調與分析過程中不同的新知識。

用SSI觸發器(用MSI器件實現的方法已經講過了)

16進制以內(更大容量的計數器采用級聯法實現)

7.5.1 同步時序邏輯電路的設計方法

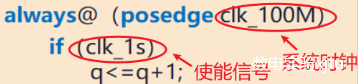

設計關鍵:根據設計要求→確定狀態轉換的規律→求出各觸發器的驅動方程。

設計步驟:(先簡單介紹,通過以下的舉例后,再進行總結,特別再點出設計關鍵)

1.根據設計要求,設定狀態,畫出狀態轉換圖。

2.狀態化簡

前提:保證滿足邏輯功能要求。

方法:將等價狀態(多余的重復狀態)合并為一個狀態。

3.狀態分配,列出狀態轉換編碼表

通常采用自然二進制數進行編碼。N為電路的狀態數。

每個觸發器表示一位二進制數,因此,觸發器的數目n可按下式確定![]() (7.5.1)

(7.5.1)

4.畫狀態轉換卡諾圖,求出狀態方程、輸出方程

選擇觸發器的類型(一般可選JKF/F或DF/F,由于JK觸發器使用比較靈活,因此,在設計中多選用JK觸發器。)

將狀態方程和觸發器的特性方程進行比較→驅動方程。

5.根據驅動方程和輸出方程畫邏輯圖。

6.檢查電路有無自啟動能力。

如設計的電路存在無效狀態時,應檢查電路進入無效狀態后,能否在時鐘脈沖作用下自動返回有效狀態工作。如能回到有效狀態,則電路有自啟動能力;如不能,則需修改設計,使電路具有自啟動能力。

7.5.2 同步時序邏輯電路的設計舉例

掌握一種方法,需要通過一定的舉例、做練習。因此本節內容的學習方法:課堂上聽懂方法、步驟、關鍵點,再通過一定量的課后作業鞏固。

[例7.5.1] 試設計一個同步七進制加法計數器。

解:設計步驟

(1)根據設計要求,設定狀態,畫狀態轉換圖。

七進制→7個狀態→用S0,S1,…,S6表示

狀態轉換圖如教材中圖7.5.1所示。

(2)狀態化簡。

本例中7個狀態都是有效狀態。

3)狀態分配,列狀態轉換編碼表。

根據式![]() ,→ N=7,n=3,即采用三個觸發器。

,→ N=7,n=3,即采用三個觸發器。

選用三位自然二進制加法計數編碼→列出狀態轉換編碼表。

(4)選擇觸發器的類型,求出狀態方程,驅動方程和輸出方程。

根據狀態轉換編碼表→圖7.5.2所示的各觸發器次態和輸出函數的卡諾圖。得

(5)根據驅動方程和輸出方程畫邏輯圖。教材中圖7.5.3所示。

(6)檢查電路有無自啟動能力。

電路有一個無效狀態111,將該狀態代入狀態方程中得000。這說明一旦電路進入無效狀態時,只要再輸入一個計數脈沖CP,電路便回到有效狀態000。

因此,具有自啟動能力。

[例7.5.2] 設計一個脈沖序列為10100的序列脈沖發生器。

解:設計步驟

(1)根據設計要求設定狀態,畫狀態轉換圖。

由于串行輸出Y的脈沖序列為10100,故電路應有5個狀態,即N=5,它們分別用S0 ,S1 ,…,S4表示。輸入第一個時鐘脈沖CP時,狀態由S0轉到S1 ,輸出Y=1:輸入第二個CP時,狀態由S1轉為S2 ,輸出Y=0;其余依次類推。

畫狀態轉換圖,教材中圖7.5.4所示。

(2)狀態分配,列出狀態轉換編碼表。

根據式![]() 可知,在N=5時,n=3,即采用三位二進制代碼。

可知,在N=5時,n=3,即采用三位二進制代碼。

可列出表7.5.2所示的狀態轉換編碼表。

(3)選擇觸發器類型,求輸出方程、狀態方程和驅動方程。

根據狀態轉換編碼表→圖7.5.5所示的各觸發器次態和輸出函數的卡諾圖。得

(4)根據驅動方程和輸出方程畫邏輯圖。如圖7.5.6所示。

(5)檢查電路有無自啟動能力。

該電路的3個無效狀態101、110、111代入狀態方程中進行計算后獲得的010、010、000都為有效狀態,這說明一旦電路進入無效狀態時,只要繼續輸入時鐘脈沖CP,電路便可自動返回有效狀態工作。

電路有自啟動能力。

思考:若設計異步時序電路,與同步時序電路應有何不同?

電子發燒友App

電子發燒友App

評論