時序邏輯電路分析

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發器功能,尤其是各種觸發器的特征方程與觸發模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

首先應該注意,時序邏輯電路之所以叫做時序,是因為電路的輸出不單單與輸入有關,還與電路本身的狀態有關,即次態受到現態和輸入的共同作用。 但是什么時候才能作用呢,是在時鐘脈沖到來時電路可以作用,可能作用的是脈沖沿,也可能是整個時鐘的高電平,這取決于你的觸發器的選擇,因而其本質上就是在時鐘CP的作用下,電路狀態不斷被刷新的過程。

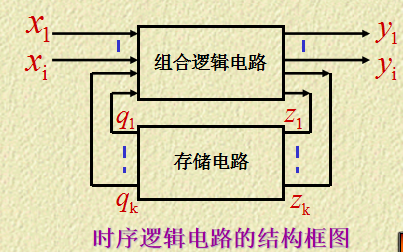

時序邏輯電路的基本結構如下圖,存儲電路就是由觸發器組成的,實現存儲功能。 設計和分析的主體即是這一部分,因為一般的組合邏輯電路較為簡單,甚至可以沒有。

我們從圖中可以明顯的看出時序邏輯電路的輸出輸入關系,即次態受到現態和輸入的共同作用這一特點。 分析時,顯然要表示出圖中的未知量,也就是除了輸入X之外的剩余三個量——Y(輸出信號)、Z(驅動信號)、Q(狀態信號)。 并且顯然他們的函數關系如下,這三大方程就是時序邏輯電路分析和設計的最核心部分,其中最重要的是驅動方程(敲黑板劃重點)。

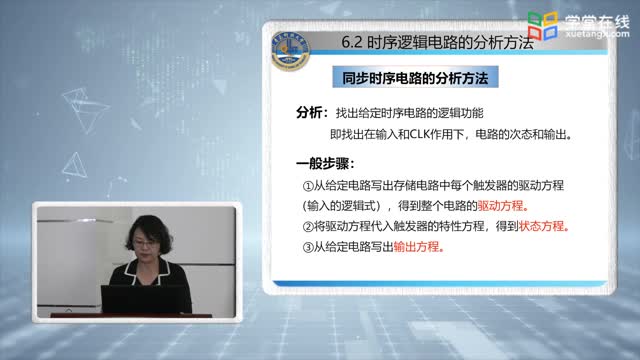

同步時序邏輯電路的分析方法

所謂的同步,意思就是觸發器的時鐘脈沖都接入的同一個CP,觸發器狀態變化在同一時鐘信號作用下

同時發生。 例如

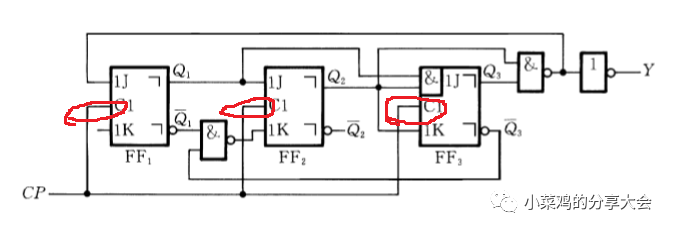

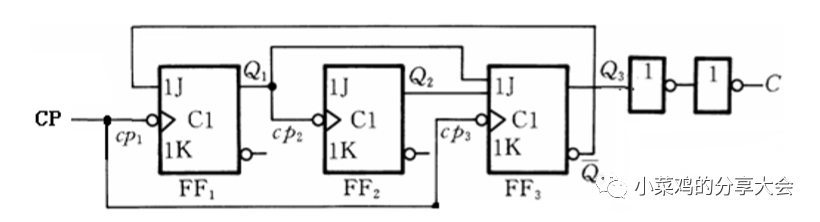

圖中畫圈部分就是這個電路的所有時鐘信號,很明顯的是他們都是同一個信號CP,因此這是一個同步電路。 接下來找三大方程,但是這里的順序很重要,一般的步驟是:

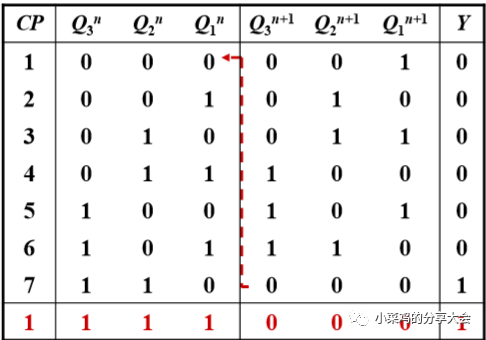

①寫出每個觸發器的驅動方程;

②把驅動方程代入相應觸發器的特性方程,得出每個觸發器的狀態方程;

③根據給定的邏輯圖,寫出電路的輸出方程。

首先寫驅動方程的意義在于,驅動方程是每個觸發器的輸入,比如上圖就是找每個J等于什么,每個K又等于什么,是一個關于輸入信號X和所有觸發器現態的函數,在得到了J和

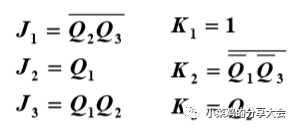

K之后代入觸發器的特征方程【比如JK觸發器就是Qn+1=JQn(非)+K(非)Qn】,我們就得到了觸發器的狀態方程,即次態,也就是真值表或者波形圖中要求的最主體的部分。 最后根據整個電路分析出輸出方程(這個比較簡單,不贅述)。 例如這里的驅動方程如下:

從而得到狀態方程

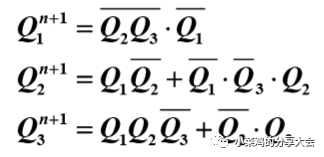

做完上述工作,分析就結束了一大半了,接下來就是分析電路功能的時候。 這里要注意的是,千萬不要嘗試去畫波形圖來解決這個事情,因為既麻煩也不好看,不如直接列真值表找主循環。 如圖

很明顯這是一個同步七進制加法計數器,比畫波形圖要直觀的多。

到這里還并沒有結束,還需要檢查自啟動問題,也就是上圖最下面的那個不在主循環的紅色狀態(無效態),看看它是不是能進入主循環(經過多少步驟都可以),只要這些無效態自己不成循環,就是可以自啟動了。 最后可以看要求畫一畫狀態轉換圖,注意標定圖例就好,這里不再贅述。

異步時序邏輯電路的分析方法

異步的意思就是觸發器的時鐘脈沖不再全都是同一個CP,它可能是另一個CP‘,也可能是某一個觸發器的輸出,但歸根結底不是同一個CP。

異步電路的分析方法與同步電路基本相同,唯一的不同點就是要在分析方程之前先要分析每個觸發器的時鐘信號CPi,并且需要在真值表中列出各個CP,在對應CP有效的情況下(如上升沿、下降沿、高電平等等),觸發器的狀態再去發生對應信號的變化,例如下圖

很明顯可以得到時鐘信號:

cp1 = cp3 = cp,cp2 = Q1

余下步驟同同步電路相同,參照前文。

-

電路分析

+關注

關注

62文章

521瀏覽量

99255 -

觸發器

+關注

關注

14文章

2029瀏覽量

61754 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16722 -

同步時序

+關注

關注

0文章

12瀏覽量

7941 -

異步時序

+關注

關注

0文章

6瀏覽量

8676

發布評論請先 登錄

相關推薦

數字電路教程之時序邏輯電路課件的詳細資料免費下載

模擬電路教程之時序邏輯電路的課件資料免費下載

評論