加法電路實驗

一、 實驗?zāi)康?/font>

2、? 分析直流輸入加法器。

3、? 分析交直流輸入加法器。

4、? 分析交流輸入加法器。

二、 實驗器材

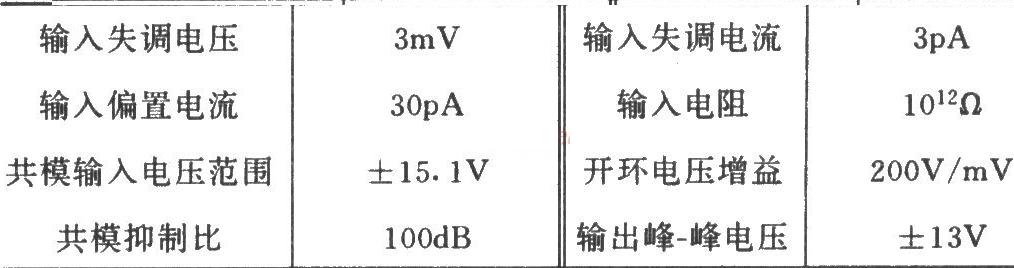

LM741 運算放大器?????????????????????????? 1個

直流電源???????????????????????????????????? 2個

0—20mA毫安表?????????????????????????????? 4個

萬用表?????????????????????????????????????? 1個

信號發(fā)生器??? ???????????????????????????????1臺

示波器??????????????????????????????????????? 1臺

電阻:2.5KΩ 2個,5kΩ 3個,?? 10kΩ????????? 1個

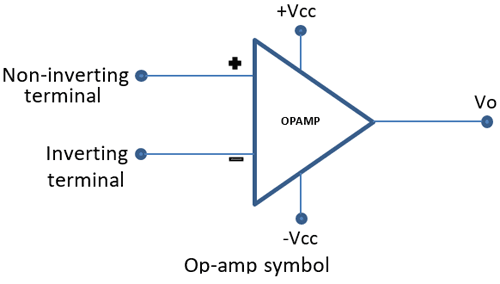

三、 實驗原理

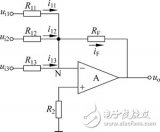

在圖1所示的加法電路中,運放的反相輸入端為虛地端。因此,輸入電流

???????????????????????? ??,?

由基爾霍夫電流定律,總電流為

???? ?????????????????????I=I1+I2

??????? 因為運放的輸入電阻很大,所以反饋電流

????????????????????????????? If≈I=I1+I2

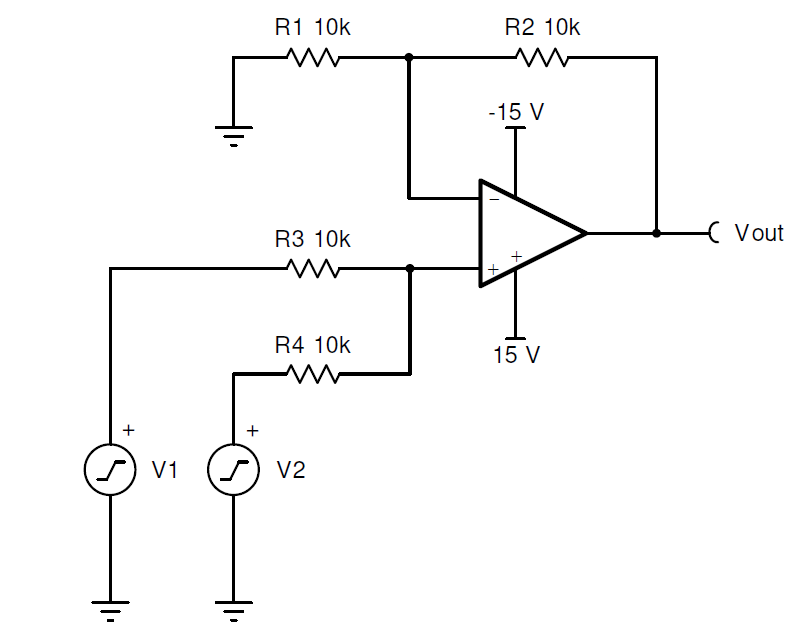

圖1 直流電壓輸入加法器

由于運放反相輸入端虛地,因此加法器的輸出電壓V0為反饋電阻Rf兩端電壓的負(fù)值

即???????????????????????

????????????????????????????

????????????????? ???????????

?????????????????????????????

式中R=R1=R2。

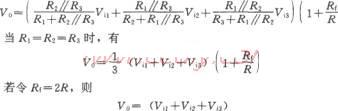

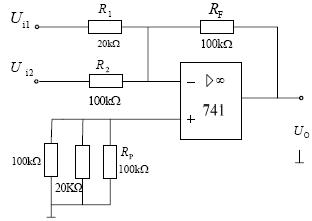

對于圖1和2所示的電路,輸出電壓為

?????????????????????????????

?????????????????????????????????

??????????????????? ??????????????

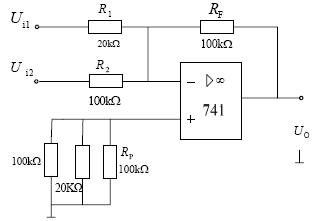

圖2 交直流輸入加法器

圖3 交流輸入加法器

四、 實驗步驟

1、? 在EWB平臺上建立如圖1 所示的實驗電路,萬用表按圖設(shè)置。單擊仿真開關(guān)運行動態(tài)分析。記錄I1、I、I2、If、V1、V2、及Vo。

2、? 根據(jù)電路元件值,計算I1、I2、I、及If。

3、? 根據(jù)步驟2的電流計算值,計算輸出電壓V0。另外,用V1和V2計算V0.

4、? 在EWB平臺上建立如圖2 所示的實驗電路,儀器按圖設(shè)置。單擊仿真開關(guān)運行動態(tài)分析。在坐標(biāo)紙上畫出輸入及輸出波形,并記錄直流輸出偏移電壓。

| ? | ? | ? | ? | ? | ? | V | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | 0 | ? | ? | ? | ? |

T |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

?

5、? 根據(jù)電路元件值,用V1和V2計算輸出電壓V0。

6、? 將電阻R2改為2.5KΩ,再次單擊仿真開關(guān)運行動態(tài)分析。在下面的坐標(biāo)紙上畫出輸入和輸出波形,并記錄直流輸出偏移電壓。

| ? | ? | ? | ? | ? | ? | V | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | 0 | ? | ? | ? | ? |

T |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

?

7、? 根據(jù)電路元件值,用V1和V2 計算輸出電壓V0 。

8、? 在EWB平臺上建立如圖3所示的實驗電路,儀器按圖設(shè)置。單擊仿真開關(guān)運行動態(tài)分析。在下面的坐標(biāo)紙上畫出輸入和輸出波形,并在曲線圖中標(biāo)明輸入及輸出峰值電壓。

| ? | ? | ? | ? | ? | ? | V | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | 0 | ? | ? | ? | ? |

T |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

| ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? | ? |

9、? 根據(jù)電路元件值,用V1和V2計算輸出電壓V0。

五、 思考與分析

1、? 在步驟1中電流I1、I2、I及If的測量值與計算值比較,情況如何?

2、? 在步驟1中輸出電壓V0的測量值與計算值比較,情況如何?為什么V0為負(fù)值?

3、? 在步驟1、3中輸出電壓與輸入電壓之間有何關(guān)系?

4、? 在步驟5中,輸入電壓與輸出電壓之間有何關(guān)系?

5、? 、在步驟6,輸入電壓與輸出電壓之間有何關(guān)系?

6、? 在步驟8中,輸入電壓與輸出電壓之間有何關(guān)系?

電子發(fā)燒友App

電子發(fā)燒友App

評論