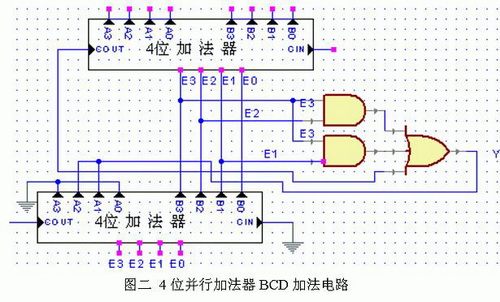

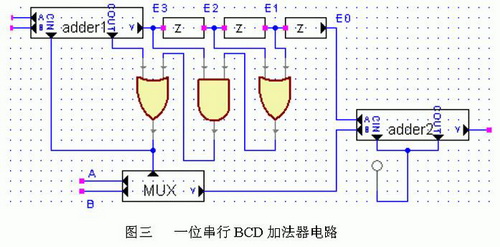

圖二所示為4位并行的BCD加法器電路。其中上面加法器的輸入來自低一級的BCD數字。下面加法器BCD的輸出E3、E2、E1、E0和COUT至高一級 BCD數字,其A3和A1位接地,即當BCD校驗信號為真時Y=1,A3A2A1A0= 0110,以實現加6的調整.當不需要BCD調整時Y=0,此時A3A2A1A0=0000,從而使輸出結果無變化.

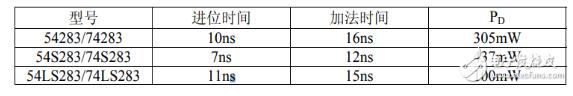

雖然4位并行加法器運算速度較快,但是所用邏輯門較多。

電子發燒友App

電子發燒友App

硬聲App

硬聲App

完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網>電子技術應用>電子技術>電路圖>信號處理電子電路圖>4位并行的BCD加法器電路圖

圖二所示為4位并行的BCD加法器電路。其中上面加法器的輸入來自低一級的BCD數字。下面加法器BCD的輸出E3、E2、E1、E0和COUT至高一級 BCD數字,其A3和A1位接地,即當BCD校驗信號為真時Y=1,A3A2A1A0= 0110,以實現加6的調整.當不需要BCD調整時Y=0,此時A3A2A1A0=0000,從而使輸出結果無變化.

雖然4位并行加法器運算速度較快,但是所用邏輯門較多。

相關推薦

431

431

1320

1320

1542

1542

2245

2245 1

1 7919

7919

20

20 4558

4558

14

14 29303

29303

23685

23685

6914

6914 4

4 18610

18610

254409

254409

79946

79946

30686

30686

134108

134108

27671

27671

10327

10327

16643

16643

157219

157219

143816

143816

22064

22064

11

11 54133

54133

33

33 47

47 17

17 6279

6279 62

62 5885

5885 12142

12142 10796

10796 2486

2486

41

41 26072

26072

3233

3233

評論