什么是全加法器?

加法器可以是半加法器或全加法器。不同之處在于半加法器僅用于將兩個(gè) 1 位二進(jìn)制數(shù)相加,因此其總和只能從 0 到 2。為了提高這種性能,開(kāi)發(fā)了FullAdder。它能夠添加三個(gè) 1 位二進(jìn)制數(shù),實(shí)現(xiàn)從 0 到 3 的總和范圍,可以用兩個(gè)輸出位 (“11”) 表示。

如果按照上面的真值表,A 和 B 表示要添加的輸入變量,而 C在是進(jìn)位輸入。S

是總和輸出,C外是指示是否發(fā)生了進(jìn)位的輸出。但是在二進(jìn)制邏輯中,進(jìn)位是什么意思?好吧,讓我們看看下一個(gè)示例:

請(qǐng)注意,當(dāng)您添加“0”和“0”或“1”和“0”時(shí),結(jié)果可以用一位表示,但是當(dāng)您添加“1”和“1”時(shí),您需要兩個(gè)位,其中一個(gè)是進(jìn)位。

但是,為什么在全加法器中需要進(jìn)位輸入呢?好吧,當(dāng)您想對(duì)超過(guò) 1 位數(shù)字的輸入求和時(shí),例如添加兩個(gè) 4位二進(jìn)制數(shù),您需要組合多個(gè)加法器并在它們之間提供進(jìn)位輸入,以表示之前不太重要的操作產(chǎn)生了進(jìn)位。

完整的加法器電路

可以使用兩個(gè)半加法器電路和一個(gè)OR門來(lái)構(gòu)建全加法器。前半加法器有兩個(gè) 1 位二進(jìn)制輸入,分別是 A 和 B。它產(chǎn)生兩個(gè)輸出;求和和結(jié)轉(zhuǎn)。

第一個(gè)半加法器的 Sum 輸出將是第二個(gè)半加法器的第一個(gè)輸入。第一個(gè)半加法器的進(jìn)位輸出將是附加OR門的第二個(gè)輸入。

第二個(gè)半加法器的第二個(gè)輸入變?yōu)檫M(jìn)位輸入 (C在) 的全加法器。

第二個(gè)半加法器還將提供求和和進(jìn)位輸出。其 Sum 輸出表示 Full Adder 的 Sum 輸出 (S),其 Carry 輸出是附加 OR門的第一個(gè)輸入。最后,OR門將生成進(jìn)位輸出(C外) 的全加法器。

讓我們用實(shí)際電路替換塊:

全加器的應(yīng)用:4位二進(jìn)制加法器

假設(shè)您要添加以下兩個(gè) 4 位二進(jìn)制數(shù) A 和 B:

A = 1111 B = 1111

結(jié)果將是一個(gè) 5 位數(shù)字:

11110

其中,最高有效位表示進(jìn)位。

因此,為了如上所述添加兩個(gè) 4 位二進(jìn)制數(shù),您需要組合四個(gè)完整加法器,如下所示:

如您所見(jiàn),每個(gè)加法器的輸入 A 和 B 包含兩個(gè) 4位二進(jìn)制數(shù)的元素,從右到左從其不太重要的位分布。另外,觀察一個(gè)完整加法器的進(jìn)位輸出如何成為下一個(gè)加法器的進(jìn)位輸入。請(qǐng)記住,這是要考慮到之前不太重要的操作是否產(chǎn)生了攜帶。

查看可以添加兩個(gè) 4008 位二進(jìn)制數(shù)的 CMOS CD4 芯片。

-

電路

+關(guān)注

關(guān)注

172文章

5962瀏覽量

172723 -

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30183

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

加法器,加法器是什么意思

十進(jìn)制加法器,十進(jìn)制加法器工作原理是什么?

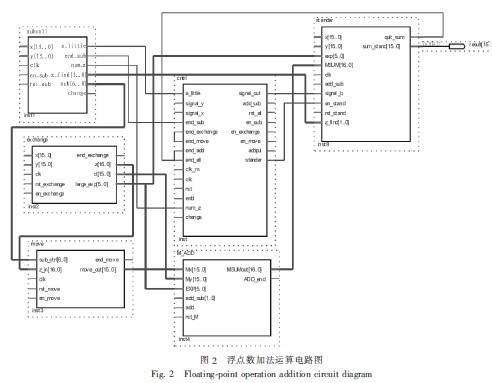

FPU加法器的設(shè)計(jì)與實(shí)現(xiàn)

同相加法器電路原理與同相加法器計(jì)算

加法器工作原理_加法器邏輯電路圖

超前進(jìn)位加法器是如何實(shí)現(xiàn)記憶的呢

加法器的原理及采用加法器的原因

半加法器的工作原理及電路解析

同相加法器和反相加法器的區(qū)別是什么

加法器的原理是什么 加法器有什么作用

全加法器的工作原理和電路解析

全加法器的工作原理和電路解析

評(píng)論