文章來源:半導體與物理

原文作者:jjfly686

隨著半導體技術不斷逼近物理極限,傳統的平面晶體管(Planar FET)、鰭式場效應晶體管(FinFET)從平面晶體管到FinFET的演變,乃至全環繞柵或圍柵(GAA, Gate-all-Around)全環繞柵極晶體管(GAAFET)等先進結構,在減少漏電、降低功耗方面雖然取得了顯著成就,但進一步微縮的挑戰日益顯現。為了延續摩爾定律的發展趨勢,并滿足未來高性能計算的需求,業界正積極研發下一代晶體管架構——互補場效應晶體管(Complementary FET, CFET)。

一、為什么需要CFET?

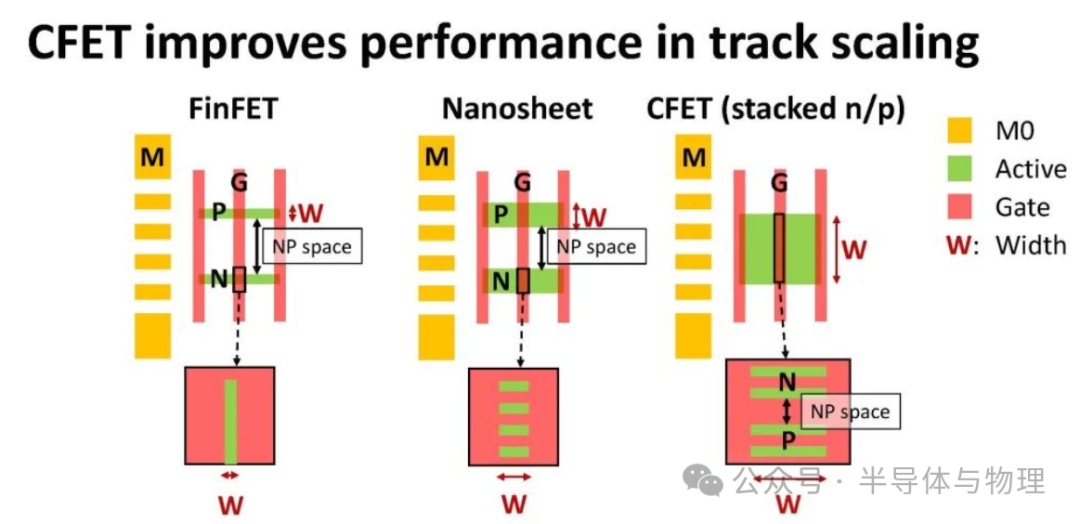

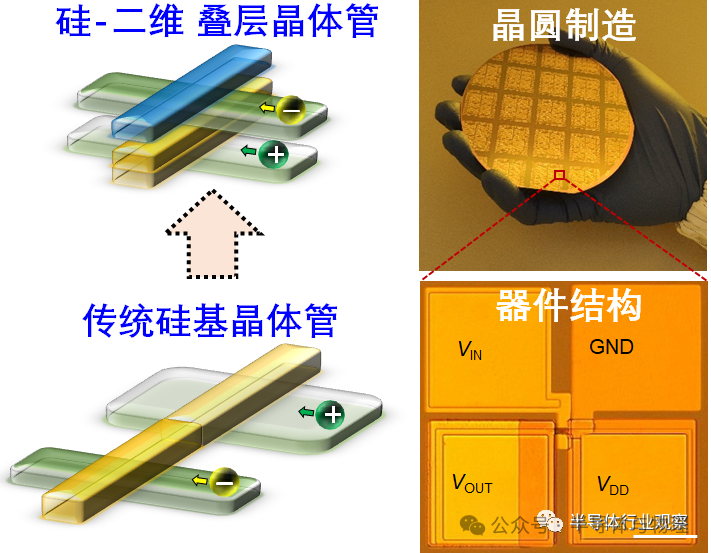

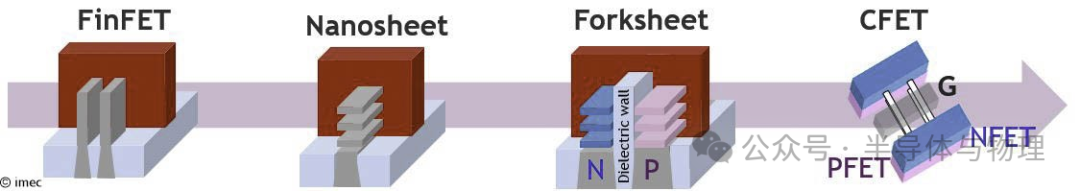

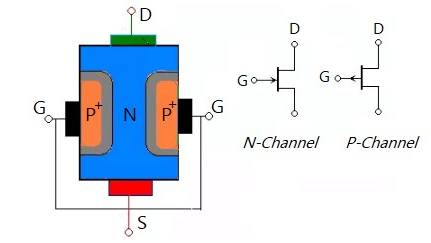

在過去的幾十年里,傳統的平面晶體管(Planar FET)、鰭式場效應晶體管(FinFET),乃至全環繞柵或圍柵(GAA, Gate-all-Around)等先進結構,你始NMOS與PMON都是在一個平面上制造,這樣無形減少了晶體管密度。在這種背景下,CFET則使用了NMOS與PMOS垂直空間上疊加。它不僅能夠在更小的空間內實現更高的晶體管密度,還能夠實現更佳的性能。

二、CFET的結構

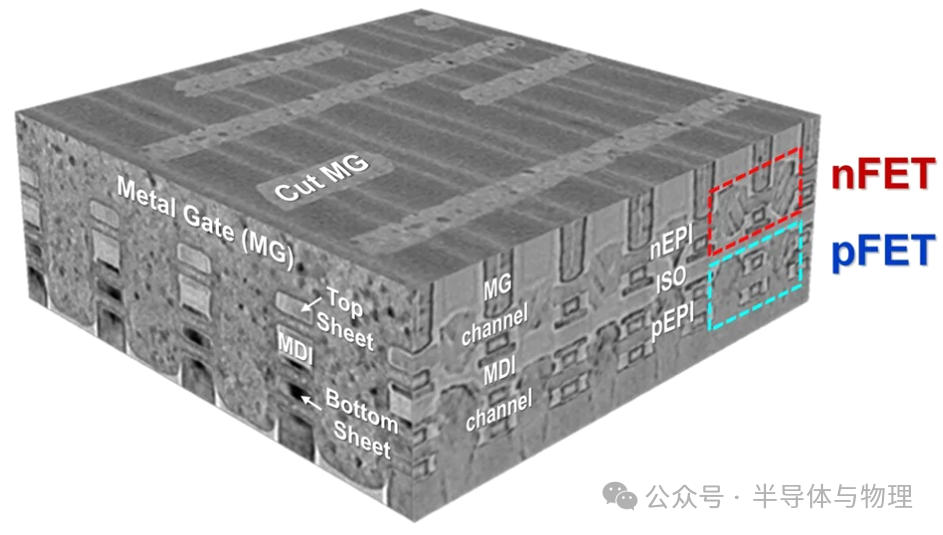

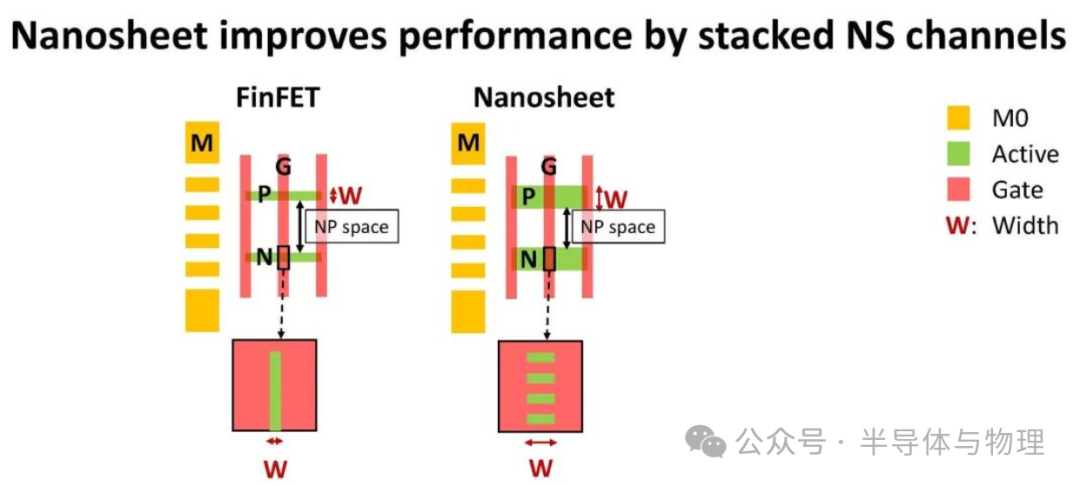

下圖左圖為FinFET的俯視結構圖,中間為GAA的俯視圖,GAA的NMOS與PMONS間距小于FinFET,但是再去減小NP間距的難度是極大的,所以CEFT就應運而生。如下圖最右CEFT俯視結構,其中NMOS與PMOS兩種不同導電類型的晶體管被垂直堆疊在一起,而不是像之前的邏輯工藝那樣位于同一平面上,很大程度上增加了晶體管集成的密度。

三、CFET的作用

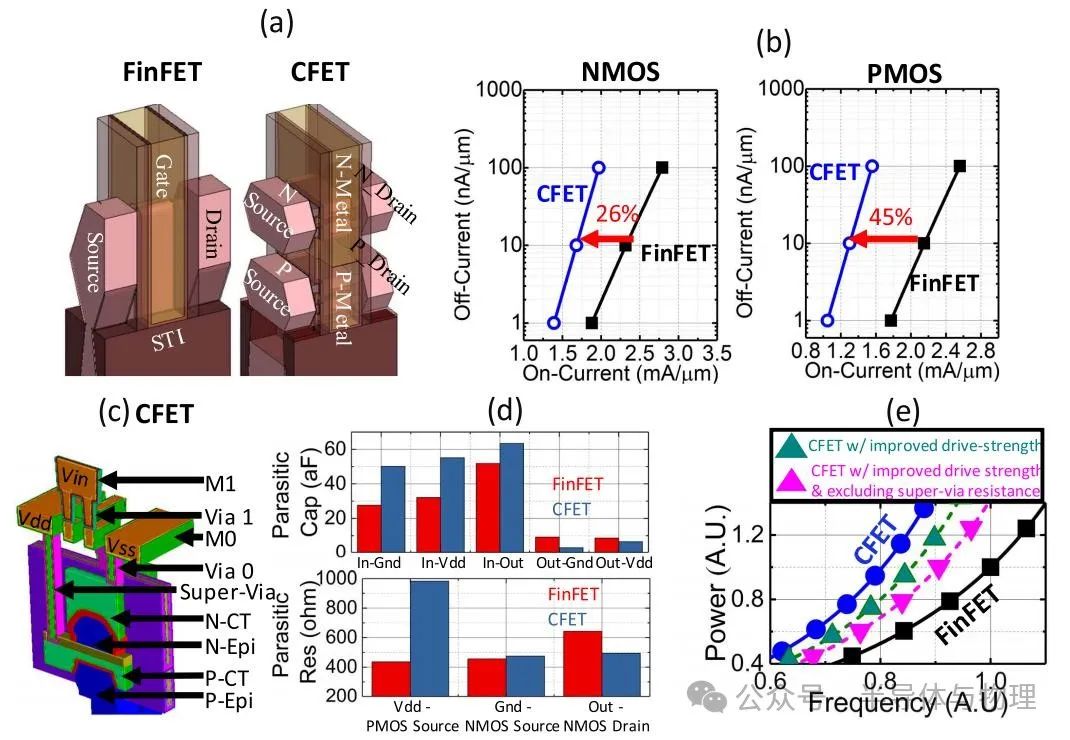

增強電流驅動能力:通過優化晶體管的設計和布局,CFET互聯可以實現更低的電阻和更高的電流導通能力,這對于提升芯片的工作速度有很大的提升。

改善短溝道效應:在納米尺度下,傳統晶體管結構面臨的主要問題是短溝道效應,這會導致漏電流增加及開關性能下降。而CFET采用的垂直堆疊結構能夠有效緩解這些問題。

四、CFET有哪些提升?

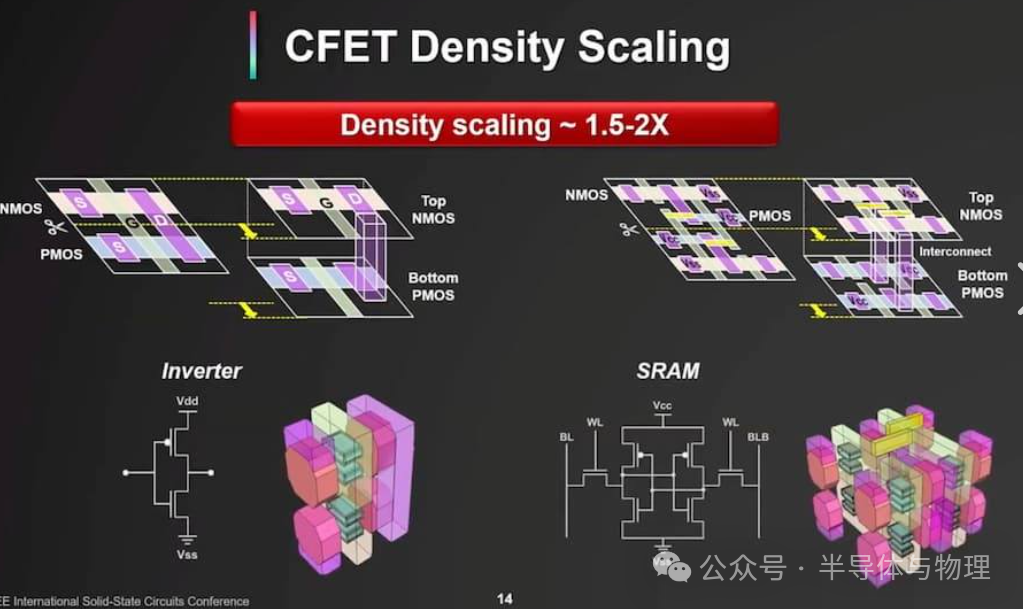

工藝尺寸微縮:IMEC的研究表明,憑借CFET晶體管技術,2032年將有望進化到5埃米(0.5nm),2036年則可能達到2埃米(0.2nm)。此外,CFET重新設定了縮放限制,因為nFET和pFET堆疊在一起,器件之間的np間距變為垂直而非水平,使得片材更寬,從而允許更大的有效溝道寬度。

高性能與低功耗:在相同的功耗條件下,N2制程下的CFET相比于N3制程下的GAA納米片晶體管,速度提升了約15%;而在相同的速度條件下,功耗則減少了大約30%,并且集成度達到了1.15倍。新的N2平臺還采用了迄今為止最密集的SRAM后端互連(~38Mb/mm2)。

-

半導體

+關注

關注

335文章

28315瀏覽量

229854 -

NMOS

+關注

關注

3文章

327瀏覽量

35211 -

晶體管

+關注

關注

77文章

9907瀏覽量

140144 -

FET

+關注

關注

3文章

690瀏覽量

63768

原文標題:互補場效應晶體管(CFET)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何判斷場效應晶體管方向,學會這幾步輕松搞定

MOS管與場效應晶體管背后的聯系,看完后就全明白了

場效應晶體管在電路中的特別應用,你未必全都清楚

場效應晶體管的分類及作用

場效應晶體管的選用經驗分享

什么是鰭式場效應晶體管?鰭式場效應晶體管有哪些優缺點?

場效應晶體管的分類及使用

什么是場效應晶體管

功率場效應晶體管的工作特性

如何進行場效應晶體管的分類和使用

場效應晶體管的分類說明

場效應晶體管的作用

評論