1 引言

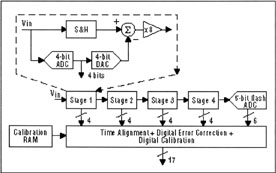

隨著現(xiàn)代電子技術(shù)迅猛發(fā)展,電子產(chǎn)業(yè)逐步形成了以數(shù)字為主的格局。數(shù)字信號(hào)處理 技術(shù)日漸成熟的同時(shí), 對(duì)模擬信號(hào)和數(shù)字信號(hào)的轉(zhuǎn)換接口電路模數(shù)轉(zhuǎn)換器 (Analog-to-Digital Converter 簡(jiǎn)稱ADC)的速度和精度方面的要求也越來越高。ADC 的性能在整個(gè)信號(hào)處理系統(tǒng)中起到至關(guān)重要的作用,成為限制整個(gè)系統(tǒng)性能的瓶頸。在整個(gè) ADC 系統(tǒng)中,前級(jí)采樣保持電路(sample-and-hold circuit 簡(jiǎn)稱S/H)的性能直接影響到 后續(xù)電路對(duì)采樣保持信號(hào)處理的正確性,從而影響整個(gè)系統(tǒng)的性能,因此對(duì)其速度和精度要 求十分嚴(yán)格。S/H 電路的精度很大程度上取決于運(yùn)放的增益,S/H 電路的帶寬則取決于運(yùn)放 的帶寬,所以設(shè)計(jì)一個(gè)相對(duì)高增益、高帶寬的運(yùn)放是整個(gè)ADC 設(shè)計(jì)的關(guān)鍵,本文采用的是增 益自舉運(yùn)放結(jié)構(gòu),可以在增益和帶寬方面得到較好的效果。此外,隨著采樣的速度和精度的 不斷提高,簡(jiǎn)單的CMOS 開關(guān)已經(jīng)不能滿足設(shè)計(jì)的需要,本文采用了柵壓自舉開關(guān)[2],可以 得到較好的采樣精度和線性度。針對(duì)運(yùn)放的增益誤差和開關(guān)電路誤差所引起S/H 電路速度受 限的問題,在整個(gè)S/H 電路結(jié)構(gòu)方面采用了雙采樣技術(shù)[3],使同一周期內(nèi)的采樣保持工作由 原來的一次變?yōu)閮纱危麄€(gè)S/H 電路的速度得到極大的提高。

2 運(yùn)放的設(shè)計(jì)

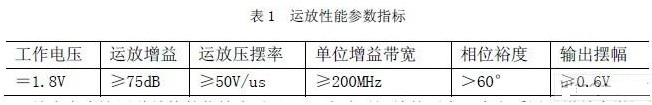

運(yùn)放是S/H 電路中的核心模塊。CMOS 的運(yùn)放主要包括四種常見結(jié)構(gòu):簡(jiǎn)單兩級(jí)運(yùn)算放大器、套筒式的共源共柵放大器、折疊式共源共柵放大器、增益自舉運(yùn)算放大器[4,5]。比較 四種結(jié)構(gòu)的性能發(fā)現(xiàn),套筒式共源共柵在速度、功耗和噪聲方面具有優(yōu)勢(shì),但是它的增益和 輸出擺幅有限,不適用于采樣增益電路中。折疊式共源共柵的速度較高,但其他四個(gè)性能參 數(shù)一般,也不采用。兩級(jí)運(yùn)放最大的缺點(diǎn)是速度提升較為困難。增益自舉運(yùn)放在增益、帶寬、 速度等方面表現(xiàn)較好。根據(jù)S/H 電路的設(shè)計(jì)要求,對(duì)運(yùn)放的各參數(shù)的性能指標(biāo)為:

綜合考慮這四種結(jié)構(gòu)的優(yōu)缺點(diǎn)以及S/H 電路對(duì)運(yùn)放的要求,本文采用了增益自舉運(yùn)放來作為S/H 電路中的核心模塊。

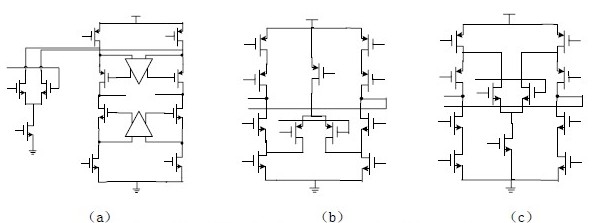

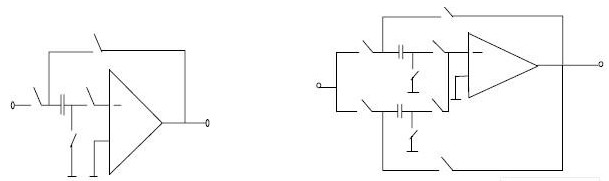

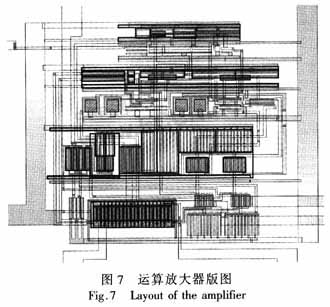

增益自舉運(yùn)放在增益和帶寬方面都具有明顯的優(yōu)勢(shì),基本的增益自舉運(yùn)放為一個(gè)主運(yùn) 放內(nèi)連接四個(gè)輔運(yùn)放構(gòu)成,這種結(jié)構(gòu)在功耗和面積方面沒有優(yōu)勢(shì)。本文設(shè)計(jì)的增益自舉運(yùn)放 只采用三個(gè)運(yùn)放構(gòu)成,主運(yùn)放采用全差分折疊共源共柵結(jié)構(gòu),考慮到匹配問題,兩個(gè)輔運(yùn)放 也采用全差分折疊共源共柵結(jié)構(gòu)設(shè)計(jì)。輔運(yùn)放單位增益頻率的選擇根據(jù)經(jīng)驗(yàn)[7]單位增益帶 寬應(yīng)大于主運(yùn)放的-3dB 帶寬,這樣主運(yùn)放就能保持原有的的高頻特性。具體電路布局如下 圖:

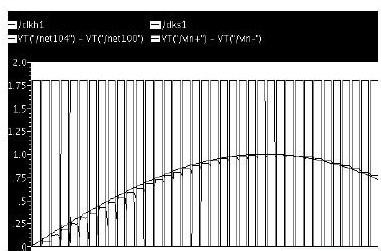

對(duì)運(yùn)放采用SMIC0.18um 工藝庫進(jìn)行仿真,得到仿真結(jié)果如下:

仿真波形如下圖所示:

3、柵壓自舉開關(guān)設(shè)計(jì)

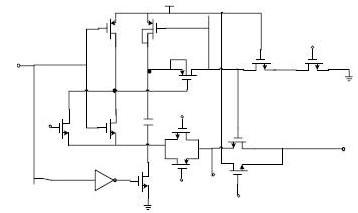

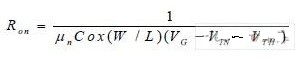

在流水線結(jié)構(gòu)中,采樣模式的開關(guān)等效為一個(gè)阻抗為 Ron 的電阻,忽略體襯偏效應(yīng)的影響,Ron 的值為:

影響開關(guān)主要性能的因素包括:開關(guān)導(dǎo)通阻抗的非線性、開關(guān)電荷注入效應(yīng)以及時(shí)鐘 饋通效應(yīng)等。開關(guān)導(dǎo)通阻抗的非線性主要影響著無雜散動(dòng)態(tài)范圍(spurious free dynamic range,SFDR);電荷注入效應(yīng)給電路引入了非線性;時(shí)鐘饋通效應(yīng)帶來了一個(gè)與輸入電壓 無關(guān)的固定失調(diào)。針對(duì)這些問題,設(shè)計(jì)選用了帶時(shí)鐘饋通補(bǔ)償結(jié)構(gòu)的柵壓自舉開關(guān)。

當(dāng)時(shí)鐘 CLK 為高電平時(shí),開關(guān)處于采樣狀態(tài),當(dāng)CLK 為低電平時(shí),開關(guān)處于保持狀 態(tài)。MS 為柵壓自舉開關(guān)中的開關(guān)管,DS 為引入的虛擬開關(guān),其作用是在時(shí)鐘由高變低的 時(shí)刻在輸出端產(chǎn)生一個(gè)補(bǔ)償電壓,用于補(bǔ)償時(shí)鐘饋通效應(yīng)帶來的影響。在開關(guān)電路中,電容 兩端電壓雖然在保持階段能夠被充到電源電壓值,但在采樣階段由于寄生電容的影響,使得 電容兩端電壓值產(chǎn)生變化,這將給開關(guān)電路帶來非線性。因此在設(shè)計(jì)時(shí),對(duì)電容值的選取要 求較高。

4、雙采樣技術(shù)采樣保持電路

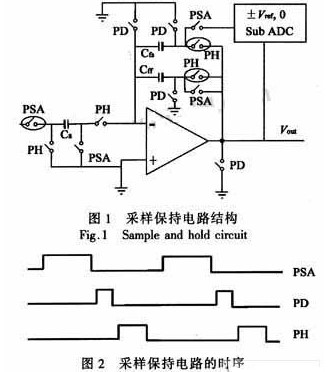

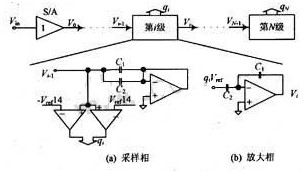

采樣保持電路是流水線 ADC 中至關(guān)重要的部分。特別是前端采樣保持電路,它將直接 影響到后續(xù)電路對(duì)采樣保持信號(hào)處理的正確性,從而影響整個(gè)系統(tǒng)的性能。基本采樣保持電 路由開關(guān)和電容組成,電容翻轉(zhuǎn)結(jié)構(gòu)的采樣保持電路,在采樣時(shí)刻,電容C 采集輸入信號(hào) 量,在保持時(shí)刻電容C 輸出電壓為采樣時(shí)刻電壓,從而實(shí)現(xiàn)采樣保持。電容翻轉(zhuǎn)結(jié)構(gòu)在功 耗與噪聲較低,適用于該流水線結(jié)構(gòu)ADC 的設(shè)計(jì)。

通過研究電路的時(shí)序發(fā)現(xiàn),基本的采樣保持結(jié)構(gòu)在采樣周期,保持電路處于空閑,在 保持周期,采樣電路處于空閑,一個(gè)時(shí)鐘周期內(nèi)電路只能對(duì)輸入信號(hào)進(jìn)行一次處理。雙采樣 結(jié)構(gòu)的采樣保持電路對(duì)電容翻轉(zhuǎn)結(jié)構(gòu)進(jìn)行擴(kuò)展,利用兩個(gè)采樣電容交替工作。在時(shí)鐘信號(hào)為高電平時(shí)刻,電容 C1 進(jìn)行采樣,輸出端保持電容C2 的采樣信號(hào);時(shí)鐘信號(hào)為低電平時(shí)刻, 電容C2 進(jìn)行采樣,輸出端保持電容C1 的采樣信號(hào)。在一個(gè)時(shí)鐘周期內(nèi)兩個(gè)電容如此交替工 作,完成兩次采樣保持過程。

整體采樣保持電路采用SMIC0.18um 工藝,利用spectre 進(jìn)行仿真。輸出的仿真結(jié)果為, 電路工作電壓1.8V,輸入信號(hào)頻率為800KHZ,采樣頻率為50MHZ。滿足流水線ADC 系統(tǒng)中 對(duì)采樣保持電路的設(shè)計(jì)要求,下圖為雙采樣技術(shù)的采樣保持電路仿真波形圖。

5、結(jié)束語

本文設(shè)計(jì)了一種采用雙采樣技術(shù)、全差分增益自舉運(yùn)放和柵壓自舉開關(guān)的采樣保持電 路。采用增益自舉運(yùn)放達(dá)到較好的增益和帶寬性能指標(biāo);采用柵壓自舉開關(guān)克服了開關(guān)導(dǎo)通 阻抗的非線性、開關(guān)電荷注入效應(yīng)以及時(shí)鐘饋通效應(yīng)等不良影響;雙采樣電路的使用使得采 樣速率達(dá)到同等結(jié)構(gòu)單采樣速率的兩倍。通過對(duì)這幾種結(jié)構(gòu)進(jìn)行分析設(shè)計(jì),最終得到的采樣 保持電路能夠滿足10bits50MS/s 的流水線ADC 的應(yīng)用。整個(gè)電路設(shè)計(jì)基于SMIC0.18um 工 藝,仿真結(jié)果表明,該采樣保持電路達(dá)到設(shè)計(jì)要求,能夠滿足中高精度高速流水線ADC 的 應(yīng)用。

-

CMOS

+關(guān)注

關(guān)注

58文章

5733瀏覽量

235865 -

adc

+關(guān)注

關(guān)注

99文章

6531瀏覽量

545400 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3217瀏覽量

126938

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

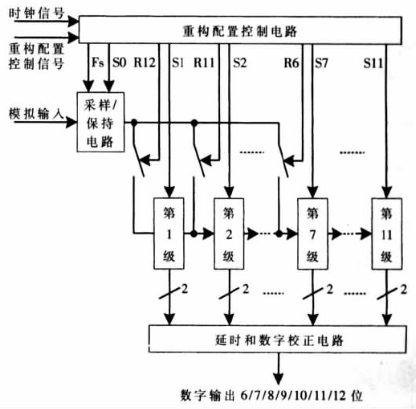

適用于多標(biāo)準(zhǔn)收發(fā)器中的可重構(gòu)流水線ADC的應(yīng)用設(shè)計(jì)

流水線ADC結(jié)構(gòu)解析 流水線ADC和其它ADC的比較

一種用于高速ADC的采樣保持電源電路的設(shè)計(jì)

如何設(shè)計(jì)一個(gè)適用于12bit流水線ADC采樣保持電路?

求一種高性能低功耗流水線ADC設(shè)計(jì)方法

流水線技術(shù)在高速數(shù)字電路設(shè)計(jì)中的應(yīng)用

適用于12 bit流水線ADC采樣保持電路的設(shè)計(jì)

13bit 40MS/s流水線ADC中的采樣保持電路設(shè)計(jì)

高速ADC的采樣保持電源電路的設(shè)計(jì)方案解析

用于高速ADC的采樣保持電源電路的設(shè)計(jì)方案解析

高性能低功耗的采樣保持電路的設(shè)計(jì)與實(shí)現(xiàn)

CEA技術(shù)的原理特點(diǎn)及在流水線ADC中的應(yīng)用

了解流水線型ADC

適用于高速流水線ADC中基于雙采樣技術(shù)的高性能采樣/保持電路設(shè)計(jì)

適用于高速流水線ADC中基于雙采樣技術(shù)的高性能采樣/保持電路設(shè)計(jì)

評(píng)論