本文介紹流水線模數轉換器(ADC)的架構和工作原理。它討論了架構、延遲、數字糾錯、元件精度和數字校準等關鍵性能特征。本文還簡要比較了流水線ADC與其他數據轉換器架構。

流水線模數轉換器(ADC)已成為最流行的ADC架構,采樣速率從每秒幾兆采樣(Msps)到100Msps+。分辨率范圍從較快采樣率的 16 位到較低采樣率的 <> 位。這些分辨率和采樣率涵蓋了廣泛的應用,包括 CCD 成像、超聲醫學成像、數字接收器、基站、數字視頻(例如 HDTV)、xDSL、電纜調制解調器和快速以太網。

采樣率較低的應用仍然是逐次逼近寄存器(SAR)和集成架構的領域,以及最近的過采樣/Σ-Δ型ADC。最高采樣速率(幾百Msps或更高)仍然使用閃存ADC獲得。盡管如此,近年來,各種形式的流水線ADC在速度、分辨率、動態性能和低功耗方面都有了很大的改進。

流水線型 ADC 架構

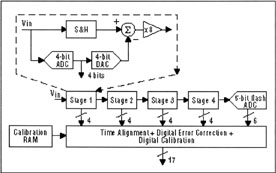

圖1所示為12位流水線ADC的框圖。

圖1.具有四個3位級的流水線ADC(每級解析<>位)。

在本原理圖中,模擬輸入,V在,首先通過采樣保持(S&H)進行采樣并保持穩定,而第一階段的閃存ADC將其量化為三位。然后將3位輸出饋送到3位DAC(精確到約12位),并從輸入中減去模擬輸出。然后將該“殘留物”增加四倍并送入下一階段(階段2)。這種增益殘差繼續通過流水線,每級提供4位,直到到達4位閃存ADC,后者解析最后<>LSB位。由于每個階段的位是在不同的時間點確定的,因此對應于同一樣本的所有位在饋送到數字糾錯邏輯之前,都與移位寄存器進行時間對齊。請注意,當一個階段完成對樣品的處理、確定位并將殘余物傳遞到下一個階段時,它可以開始處理從每個階段中嵌入的采樣保持接收的下一個樣品。這種流水線操作是高吞吐量的原因。

數據延遲

由于每個樣本必須在整個流水線中傳播,然后其所有相關位才能組合到數字糾錯邏輯中,因此數據延遲與流水線ADC相關聯。在圖 1 的示例中,此延遲約為三個周期(參見圖 2)。

圖2.流水線 ADC 中的數據延遲。

數字糾錯

大多數現代流水線ADC采用一種稱為“數字糾錯”的技術,以大大降低閃存ADC(從而降低各個比較器)的精度要求。在圖1中,請注意,求和節點輸出端的3位殘差的動態范圍是原始第1級輸入的八分之一(V在),但隨后的增益僅為4。因此,第2級的輸入僅占第3級2位ADC范圍的一半(即,當第3級的第一個1位轉換沒有誤差時)。

如果第一個3位閃存ADC中的一個比較器在施加接近該比較器跳變點的模擬輸入時具有明顯的失調,則會導致錯誤的3位代碼,從而導致錯誤的3位DAC輸出,從而產生不同的殘余。只要該增益殘差不會超出后續3位ADC的范圍,就可以證明剩余流水線生成的LSB代碼(當添加到不正確的3位MSB代碼時)將給出正確的ADC輸出代碼。這意味著圖1中沒有一個閃存ADC必須與整個ADC一樣精確。事實上,第3至1級的4位閃存ADC只需要大約<>位精度。

數字糾錯不會校正最終4位閃存轉換中的錯誤。在該轉換中發生的任何錯誤都會被大 (44) 4 位閃存之前的累積增益。因此,最后階段只需要精度超過4位。

雖然在圖1示例中,每級產生三個原始位,但由于級間增益僅為4,因此每級(級1至4)僅有效解析3位。如上所述,額外的位只是將殘余的大小減小一半,從而在下一個1位ADC中允許額外的范圍用于數字糾錯。此過程稱為相鄰階段之間的“2 位重疊”。因此,整個ADC的有效位數為2 + 2 + 2 + 4 + 12 = <>位。

組件精度

數字糾錯不能校正單個DAC和增益放大器中的增益或線性誤差。前端S&Hs和DAC實際上需要大約12位精度,而后續階段的組件需要較低的精度(例如,第10級為2位精度,第8級為3位,依此類推)。這種降低精度的需求是因為后期級的誤差項除以前面的級間增益。這一事實經常被用來通過使流水線級逐漸變小來節省額外的功率。

在大多數采用CMOS或BiCMOS技術設計的流水線ADC中,S&H、DAC、求和節點和增益放大器通常作為單個開關電容電路模塊實現,稱為乘法DAC(MDAC)。限制MDAC精度的主要因素是固有的電容失配。純雙極性實現將更加復雜,并且主要受到電流源DAC和級間增益放大器中的電阻失配的影響。

通常,對于大約12位或更高的精度,需要某種形式的電容/電阻調整或數字校準,特別是對于前兩級。

數字校準

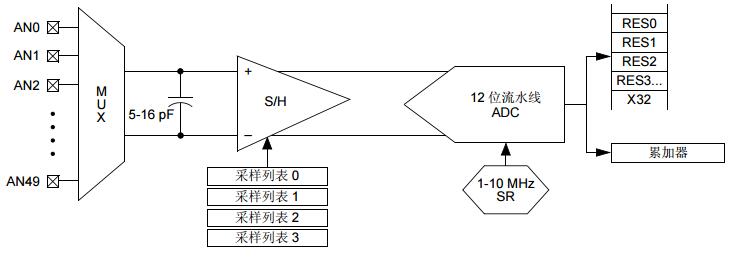

MAX1200 (16位,1Msps)、MAX1201 (14位2Msps)和MAX1205 (14位,1Msps)系列ADC1采用數字校準,以確保出色的精度和動態性能。 每個器件都是一個CMOS流水線ADC,具有四個4位級(具有1位重疊),末端有一個5位閃存ADC,總共提供3 + 3 + 3 + 3 + 5 = 17個原始位(見圖3)。數字校準需要額外的14到16位來量化誤差項,使其比ADC本身更高精度;額外的位也被丟棄,以提供 <> 位或 <> 位。

校準從第三階段的MDAC開始;超出第三級后,MDAC 誤差項足夠小,無需校準。第三級輸出由剩余的流水線ADC數字化,誤差項存儲在片內RAM中。校準第三個 MDAC 后,可用于以類似的方式校準第二個 MDAC。同樣,一旦校準了第二個和第三個 MDAC,它們就會用于校準第一個 MDAC。使用平均(特別是在第一個和第二個MDAC中)來確保校準是無噪聲的。在正常轉換期間,這些誤差項從RAM中調用,并用于調整數字糾錯邏輯的輸出。

圖3.MAX1200流水線ADC架構

不同的變化

圖1中的示例顯示,流水線ADC可以有很多變化,取決于幾個變量:每級解析多少位;LSB閃存ADC中的位數;以及是否使用數字校準或調整來提高前幾個階段的精度。每級的位劃分部分由目標采樣速率和分辨率決定。一般而言,高速CMOS流水線ADC傾向于每級較低的位數(每級低至2位,因此級間增益僅為<>),因為在CMOS中很難實現增益非常高的寬帶放大器。采樣速率較低的CMOS流水線ADC和雙極性流水線ADC(即使是采樣速率非常高的ADC)往往有利于每級使用更多位。這也減少了數據延遲。

CMOS MAX1425 (10位,20Msps)和MAX1426 (10位,10Msps)系列采用流行的每級1.5位架構;每個階段解析一位,具有 0.5 位重疊。每個1.5位級都有一個1.5位閃存ADC(只有兩個比較器),而全2位閃存ADC則為一個。可以證明,通過數字糾錯,這與具有2位閃存ADC和DAC的常規MDAC級的工作方式相同。這些轉換器實現了 59dB 的高 SNR,10MHz 模擬輸入采樣速率為 20Msps。

MAX1444/MAX1446/MAX1448/MAX1449系列(分別為10位、40/60/80/105Msps)是最新一代高速、超低功耗、10位ADC,采用每級1.5位架構。這些CMOS器件集成了寬帶低失真采樣保持放大器,以確保在整個奈奎斯特頻段內外具有出色的動態性能。欠采樣是數字接收器設計中常見的,這些ADC系列可以實現。

每級1.5位流水線ADC

圖4.V殘留與 V在傳輸特性

1.5位閃存ADC(兩個比較器)將模擬輸入與比較器門限進行比較,在本例中為-0.25V和+0.25V。然后,ADC提供與模擬輸入落點區域相對應的數字輸出。1.5 位表示 V 上有三個區域殘留與 V在轉移特性。1 位 ADC 在傳輸特性上有兩個區域(1/高或 0/低),2 位 ADC 在傳輸特性上有兩個區域(00、01、10 和 11)。

根據閃存ADC輸入的下降區域,殘余電壓計算如下,并作為輸入電壓饋送到下一級。

表1舉例說明了在0級流水線ADC中,采樣的+6.7模擬輸入電壓如何轉換為數字輸出。流水線ADC的第一級負責最高有效位,第七級提供數字輸出的最低有效位。

| 階段 | V在(五) |

V 上的區域殘留與 V在傳輸特性 (見圖4) |

數字輸出(- 1、0 或 +1) | 小數位值 | V殘留(五在下一階段) |

| 1 | 0.6 | 區域 3 | +1 | 64 | 2 × 0.6 - 1 |

| 2 | 0.2 | 區域 2 | 0 | 32 | 2 × 0.2 |

| 3 | 0.4 | 區域 3 | +1 | 16 | 2 × 0.4 - 1 |

| 4 | -0.2 | 區域 2 | 0 | 8 | 2 × (-0.2) |

| 5 | -0.4 | 區域 1 | -1 | 4 | 2 × (-0.4) + 1 |

| 6 | 0.2 | 區域 2 | 0 | 2 | 2 × 0.2 |

| 7 | 0.4 | 區域 3 | 1 | 1 | 不需要 |

使用每級的數字輸出及其小數位,采樣的+0.6V模擬輸入電壓對應于:

[(64 × 1) + (32 × 0) + (16 × 1) + (8 × 0) + (4 × -1) + (2 × 0) + (1 × 1)] = 77

127(全部1s)的數字輸出對應于1V的模擬輸入。因此,77的數字輸出將對應于77/127 = 0.606V,這是施加到流水線ADC的采樣模擬輸入的良好近似值。

流水線型模數轉換器與其他模數轉換器的比較

與SAR相比

在逐次逼近寄存器(SAR)ADC中,位由單個高速、高精度比較器逐位決定,從MSB到LSB。SAR ADC將模擬輸入與DAC進行比較,DAC的輸出按先前確定的位更新,并依次接近模擬輸入。SAR的這種串行特性將其工作速度限制在不超過幾個Msps,對于非常高的分辨率(14至16位)仍然較慢。然而,流水線ADC采用并行結構,其中每級同時處理1到幾位(連續采樣)。雖然SAR中只有一個比較器,但該比較器必須快速(時鐘頻率約為位數x采樣速率),并且與ADC本身一樣精確。相比之水線ADC內部的比較器都不需要這種速度或精度。

然而,流水線ADC通常需要比等效SAR多得多的硅面積。SAR 還顯示僅一個周期的延遲(一個周期 = 1/F樣本),而典型流水線ADC中的周期約為12個或更多。與流水線一樣,精度超過<>位的SAR通常需要某種形式的調整或校準。

與閃光燈

盡管具有固有的并行性,但流水線ADC仍然需要在DAC和級間增益放大器中進行精確的模擬放大,因此需要很長的線性建立時間。然而,純閃存ADC具有大量比較器,每個比較器由寬帶、低增益前置放大器組成,后跟一個鎖存器。與流水線ADC中的放大器不同,前置放大器必須提供不需要線性或精度的增益;只有比較器的跳變點必須準確。因此,流水線ADC的速度無法與設計良好的閃存ADC的速度相媲美。

極快的8位閃存ADC(或其折疊/插值變體)的采樣速率高達1.5Gsps(例如MAX104/MAX106/MAX108)。找到10位閃存要困難得多,而12位(或更高)閃存ADC不是商業上可行的產品。這僅僅是因為在閃存ADC中,每增加一位分辨率,比較器的數量就會增加2倍;同時,每個比較器的精度必須提高一倍。然而,在管道中,對于一階,復雜性僅隨分辨率線性增加,而不是呈指數增加。

在流水線和閃存轉換器均可獲得的采樣速率水線器件的功耗通常比閃存低得多。流水線ADC通常不太容易受到比較器亞穩態的影響。閃存中的比較器亞穩態可能導致閃光碼誤差,在這種情況下,ADC會提供不可預測的不穩定轉換結果。

與Σ-Δ轉換器相比

傳統上,數字音頻中常用的過采樣/Σ-Δ型轉換器的帶寬有限,約為22kHz。最近,一些高帶寬Σ-Δ轉換器的帶寬達到1MHz至2MHz,分辨率為12至16位。這些規格表明,集成了多位ADC和多位反饋DAC的非常高階Σ-Δ調制器(例如,第四個甚至更高)。它們的主要應用是在ADSL中。Σ-Δ轉換器不需要特殊的調整/校準,即使是16至18位的分辨率。它們還要求在模擬輸入端使用陡峭的滾降抗混疊濾波器,因為采樣速率遠高于有效帶寬。后端數字濾波器負責該任務。Σ-Δ轉換器的過采樣特性也傾向于“平均”模擬輸入端的任何系統噪聲。

Σ-Δ轉換器以速度換取分辨率。需要多次采樣(例如,至少16次,但通常要高得多)才能產生一個最終采樣,導致Σ-Δ調制器中的內部模擬元件的運行速度比最終數據速率快得多。數字抽取濾波器的設計也很簡單,并且消耗大量的硅面積。最快的高分辨率Σ-Δ型轉換器預計在不久的將來不會有超過幾MHz的帶寬。與流水線ADC一樣,Σ-Δ轉換器也存在延遲。

與半(兩步)閃光相比

兩步閃存轉換器可以概括為兩級流水線器件。然而,隨著數字糾錯時位數的增加(例如,12位或更高),每級都需要集成一個6至7位閃存ADC。級間增益放大器也需要非常高的增益。因此,對于更高的分辨率,使用兩個以上的階段是更明智的。

結論

流水線型ADC是采樣速率從幾Msps到100Msps+的首選架構。設計復雜性僅隨位數線性(非指數)增加,因此同時為轉換器提供高速、高分辨率和低功耗。流水線ADC在廣泛的應用中非常有用,尤其是在數字通信中,轉換器的動態性能通常比傳統的直流規格(如差分非線性(DNL)和積分非線性(INL))更重要。在大多數應用中,流水線ADC的數據延遲幾乎無關緊要。 Maxim不斷為其流水線ADC產品組合開發新的轉換器。這些流水線ADC很好地補充了其采用其他架構設計的ADC系列。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8742瀏覽量

147739 -

Maxim

+關注

關注

8文章

859瀏覽量

87327 -

adc

+關注

關注

99文章

6533瀏覽量

545434

發布評論請先 登錄

相關推薦

流水線ADC結構解析 流水線ADC和其它ADC的比較

驅動流水線型ADS5500 ADC的運放電路抗混疊RC阻容設計是否與SAR ADC一樣的呢?

請教流水線型 AD 的優缺點

流水線型ADC MAX1200 及其與DSP 的接口

流水線ADC

流水線ADC的行為級仿真

如何選擇合適的LED生產流水線輸送方式

12bit200MSPS時間交織流水線ADC研究與設計

什么是流水線 Jenkins的流水線詳解

ADS822和ADS825流水線型CMOS模數轉換器(ADC)數據表

了解流水線型ADC

了解流水線型ADC

評論