以下文章來(lái)源于泰豐瑞電子,作者Fiona

一種新型RDL PoP扇出晶圓級(jí)封裝工藝芯片到晶圓鍵合技術(shù)

扇出型晶圓級(jí)中介層封裝( FOWLP)以及封裝堆疊(Package-on-Package, PoP)設(shè)計(jì)在移動(dòng)應(yīng)用中具有許多優(yōu)勢(shì),例如低功耗、短信號(hào)路徑、小外形尺寸以及多功能的異構(gòu)集成。此外,它還可以應(yīng)用于多種封裝平臺(tái),包括PoP、系統(tǒng)級(jí)封裝(SiP)和芯片尺寸封裝( CSP)。這些優(yōu)勢(shì)來(lái)源于一種稱為再分布層(Redistribution Layer, RDL)的先進(jìn)互連技術(shù)。

然而,PoP類型的基于RDL的平臺(tái)需要在頂部和底部?jī)蓚?cè)都制作再分布層(RDL),以便能夠在上面堆疊另一個(gè)封裝。在一個(gè)整體工藝流程中,這意味著第二層RDL只能在完成所有第一層RDL以及諸如倒裝芯片鍵合、塑封和晶圓背面研磨等組裝工序之后才能制造。因此,這種工藝流程不像非PoP類型平臺(tái)那樣具有優(yōu)勢(shì),因?yàn)樵诘诙覴DL工藝過(guò)程中芯片可能會(huì)損 失或損壞。

為了解決基于RDL的中介層封裝堆疊(PoP)挑戰(zhàn),引入了一種真正的芯片最后工藝流程(chip-last process flow),并采用了芯片到晶圓(Chip-to-Wafer, C2W)鍵合技術(shù)。文章展示了構(gòu)建和測(cè)試一個(gè)基于RDL的晶圓級(jí)中介層PoP封裝的結(jié)果,該封裝的尺寸為12.5 x 12.5 mm2,厚度為0.357 mm 包括植球。底部側(cè)具有三層再分布層(RDL)結(jié)構(gòu),而用于封裝堆疊的頂部RDL為單層結(jié)構(gòu)。這些RDL使用銅(Cu)線實(shí)現(xiàn),線寬/間距(L/S)為5 μm/10 μm,并且采用銅芯焊球(Copper-Cored Solder Balls, CCSBs)作為垂直互連組件。通過(guò)可靠性測(cè)試確認(rèn)了硅片和CCSBs的連接質(zhì)量。測(cè)試樣品封裝通過(guò)了所有可靠性測(cè)試,包括濕氣敏感性測(cè)試(Moisture Resistance Test, MRT)L3、溫度循環(huán)測(cè)試(TCB)1,000次循環(huán)以及高溫存儲(chǔ)( HTS)1,000小時(shí)。

一、介紹

中介層封裝堆疊( PoP)是一種實(shí)現(xiàn)三維(3D)結(jié)構(gòu)需求的封裝技術(shù),通過(guò)堆疊兩個(gè)不同的層壓基板(頂部中介層和底部基板),并使用銅芯焊球(Copper-Cored Solder Balls, CCSBs)或通孔(Through Mold Vias, TMVs)進(jìn)行垂直互連。使用兩個(gè)基板提供了更容易的翹曲管理以及更具成本效益的靈活構(gòu)造的優(yōu)勢(shì)。通過(guò)優(yōu)化基板材料和設(shè)計(jì),可以控制封裝的翹曲。頂部中介層為商業(yè)現(xiàn)成或定制內(nèi)存的使用提供了設(shè)計(jì)靈活性。

由于這些原因,中介層封裝堆疊(Interposer PoP)主要用于移動(dòng)應(yīng)用處理器(APs。盡管基于層壓基板技術(shù)的中介層PoP是一個(gè)非常強(qiáng)大的平臺(tái),能夠滿足當(dāng)前行業(yè)的需求,但它在減少封裝厚度和本體尺寸方面仍存在局限性,這是由于當(dāng)前基板制造能力的限制所致。除了封裝尺寸的限制外,5G時(shí)代的先進(jìn)封裝還需要更高的輸入/輸出(I/O)數(shù)量,這需要更精細(xì)的互連、更細(xì)的凸點(diǎn)間距以及多芯片集成。

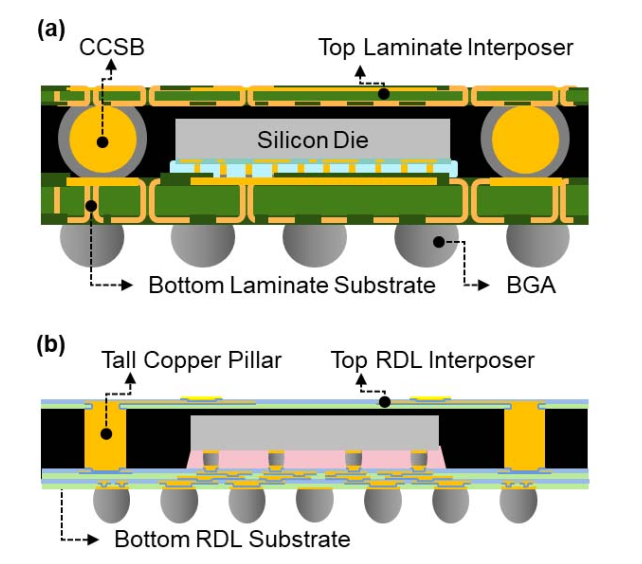

先進(jìn)封裝專注于新材料和組裝技術(shù),以滿足上述新的需求。其中一項(xiàng)有前景的技術(shù)是利用銅再分布層(RDL)技術(shù)的中介層封裝堆疊(Interposer PoP)平臺(tái),該技術(shù)已經(jīng)應(yīng)用于旗艦移動(dòng)處理器中。基于RDL的3D封裝具有許多優(yōu)勢(shì),如外形尺寸、特征尺寸、電氣和熱性能等。圖1展示了兩種不同的中介層PoP:(a) 基于層壓基板的中介層PoP,以及 (b) 基于RDL的中介層PoP。圖1顯示了兩種不同的PoP:(a)層壓式,(b)基于RDL的。

圖1. 中介層PoP的示意圖

a) 基于層壓基板

b) 基于RDL(再分布層)

RDL制造技術(shù)基于晶圓處理,能夠?qū)崿F(xiàn)更薄和更精細(xì)的電氣走線。RDL傳統(tǒng)上是通過(guò)在硅或玻璃晶圓上采用加成層方法(additive layer method)制造的。通過(guò)重復(fù)構(gòu)建鈍化層和金屬互連層,可以實(shí)現(xiàn)多層RDL。每條金屬線通過(guò)鈍化層中圖案化的過(guò)孔(vias)進(jìn)行機(jī)械和電氣連接。

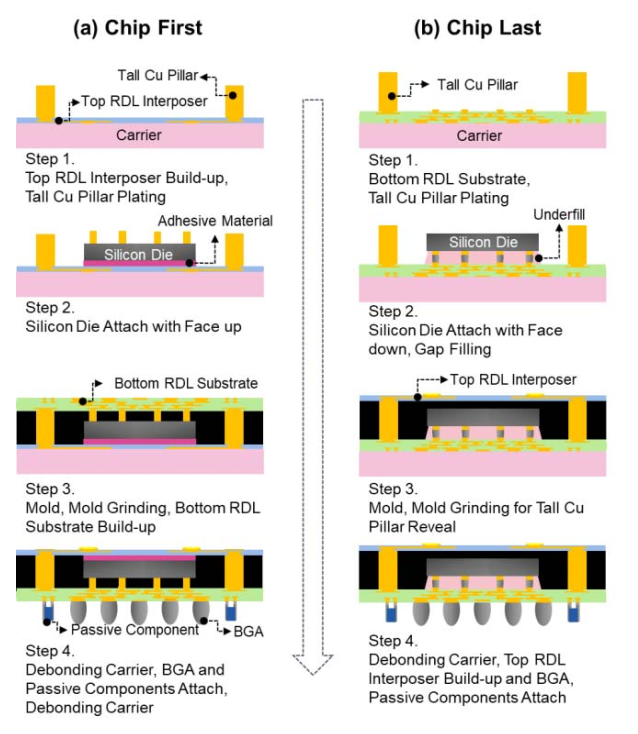

基于RDL的中介層PoP有兩種主要的工藝概念,如圖2所示:(a) 芯片優(yōu)先和 (b) 芯片最后。在芯片優(yōu)先工藝中,芯片以正面朝上的方式鍵合到帶有或不帶中介層RDL的基板上,然后使用環(huán)氧模塑料(EMC)材料進(jìn)行封裝。為了實(shí)現(xiàn)電氣連接,通過(guò)晶圓研磨暴露芯片上的金屬焊盤(pán)。最后,在塑封暴露的一側(cè)制造多層RDL。這些多層RDL作為底部RDL基板。在制造復(fù)雜的多層底部RDL之前,芯片已經(jīng)被附著在晶圓上。芯片最后工藝的流程與芯片優(yōu)先相反。首先在晶圓上準(zhǔn)備底部RDL基板層,然后如圖2(b)所示,將芯片以倒裝芯片的方式鍵合上去。頂部RDL中介層可以根據(jù)需求進(jìn)行制造。

圖2. 工藝流程示意圖

a)芯片優(yōu)先

b)芯片最后

這兩種選項(xiàng)在良率管理和建程周期控制方面各有優(yōu)缺點(diǎn)。然而,如果需要制造頂部和底部的RDL層,兩種選項(xiàng)都無(wú)法避免芯片損失的風(fēng)險(xiǎn),因?yàn)橹辽儆幸粚覴DL(頂層或底層)必須在芯片鍵合之后進(jìn)行制造。這種工藝流程還會(huì)因?yàn)轫樞蚬に嚵鞒潭鴮?dǎo)致工藝周期時(shí)間增加。

一種新的混合組裝工藝已經(jīng)被引入,可以克服上述技術(shù)障礙。通過(guò)使用扇出型測(cè)試樣品進(jìn)行樣件制造,以評(píng)估封裝在結(jié)構(gòu)和可靠性方面的特性。新工藝的關(guān)鍵區(qū)別在于每個(gè)RDL層是分別準(zhǔn)備的,并在芯片附著后進(jìn)行組裝。這種工藝的一個(gè)好處是在實(shí)際芯片組裝步驟之前可以進(jìn)行中間測(cè)試,以識(shí)別已知良好的位置。這樣,實(shí)際芯片僅被放置在已知良好的RDL位置上。換句話說(shuō),通過(guò)分離RDL準(zhǔn)備過(guò)程,可以在RDL工藝過(guò)程中防止實(shí)際芯片的損失。另一個(gè)好處是樣本處理效率的提高,因?yàn)轫敳亢偷撞縍DL層都是直接在載體晶圓上形成的,而不需要任何如EMC底填料等中間材料。因此,在RDL工藝過(guò)程中,晶圓提供了平坦的表面,最終這些工藝特點(diǎn)有助于整體RDL和組裝工藝良率的提升。

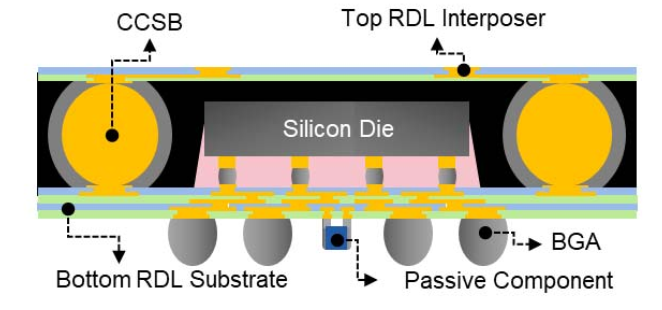

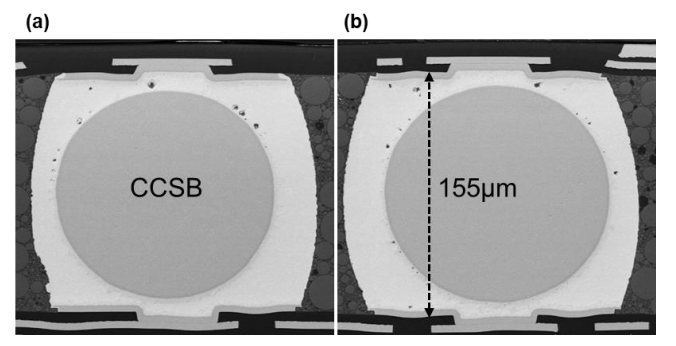

代替高銅柱用于垂直互連,在混合工藝中應(yīng)用了銅芯焊球(CCSBs),如圖3所示的基于層壓基板的中介層PoP。最新的基于RDL的3D封裝平臺(tái)采用高銅柱。然而,在這種新工藝中,電鍍銅柱可能在組裝過(guò)程中無(wú)法提供足夠的堅(jiān)固性。CCSB技術(shù)是垂直互連中一種成熟且可靠的方法,特別適用于基于層壓基板的移動(dòng)封裝,因?yàn)樵谂炕亓骱高^(guò)程中不熔化銅芯球,可以控制頂部中介層和底部基板之間的間隙高度。

評(píng)估封裝在結(jié)構(gòu)和可靠性方面的特性。新流程的一個(gè)關(guān)鍵區(qū)別在于,每個(gè)RDL都是單獨(dú)準(zhǔn)備的,并在芯片附著后進(jìn)行組裝。該流程的一個(gè)好處是,在實(shí)際芯片組裝步驟之前可以進(jìn)行臨時(shí)測(cè)試,以識(shí)別已知良好的位置。然后,實(shí)際芯片僅可以分配到已知良好的RDL位置。換句話說(shuō),通過(guò)分離RDL準(zhǔn)備過(guò)程,可以防止RDL過(guò)程中實(shí)際芯片丟失。另一個(gè)好處是樣本處理效率,因?yàn)轫敳亢偷撞縍DL層直接形成在載體晶圓上,無(wú)需任何中間材料,如EMC灌封料。因此,晶圓在RDL工藝過(guò)程中提供了平坦的表面,最終,這些工藝特征有助于整體RDL和組裝工藝的產(chǎn)量提高。

圖3. 帶有CCSB的基于RDL的

中介層PoP示意圖

提供了使用新工藝流程構(gòu)建測(cè)試樣品的結(jié)果及其可靠性性能。以下部分還將討論該工藝的優(yōu)勢(shì)。

二、測(cè)試樣品信息

A封裝結(jié)構(gòu)

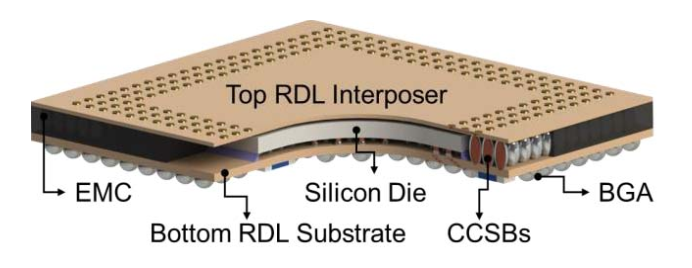

圖4展示了一個(gè)中介層PoP測(cè)試樣品的三維示意圖。該結(jié)構(gòu)包括一個(gè)硅片、銅芯焊球(CCSBs)、頂部RDL中介層以及底部RDL層。硅片以倒裝芯片的方式鍵合在底部RDL基板上,其中外圍陣列使用45 μm的凸點(diǎn),而核心陣列則使用65 μm的凸點(diǎn)進(jìn)行微凸點(diǎn)布局。環(huán)氧模塑料(EMC)被填充在這兩層RDL之間,并用來(lái)封裝硅片和CCSBs,確保整個(gè)結(jié)構(gòu)的穩(wěn)定性和可靠性。

圖4. 基于RDL的中介層PoP的

3D示意圖

頂部RDL中介層設(shè)有凸塊下金屬(UBM)焊盤(pán)陣列,用于與移動(dòng)內(nèi)存封裝或如電容器和電感器等無(wú)源組件建立電氣連接。頂部RDL中介層的信號(hào)路徑通過(guò)連接兩層之間的CCSBs擴(kuò)展到底部RDL層。360個(gè)CCSBs的間距為250 μm。

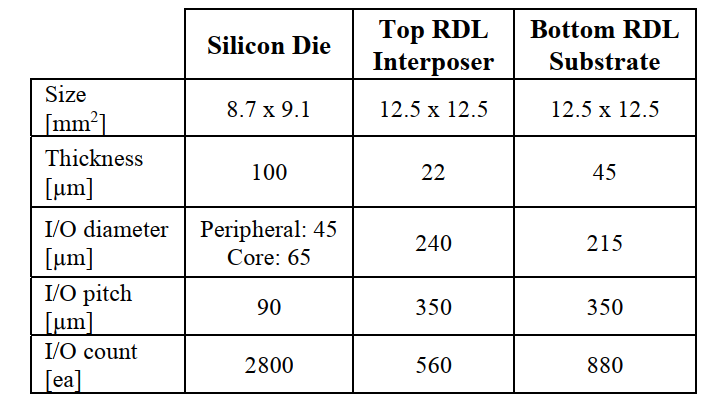

底部RDL基板由三層金屬層和四層介電有機(jī)鈍化層構(gòu)成。底部RDL的最小線寬(L)和間距(S)分別是5 μm和10 μm。這種精細(xì)的金屬互連線寬度在維持封裝尺寸有限的同時(shí),提升了信號(hào)集成度。封裝用的環(huán)氧模塑料(EMC)為硅片和銅芯焊球(CCSBs)提供了結(jié)構(gòu)強(qiáng)度、電氣絕緣和環(huán)境保護(hù)。在封裝底部形成了一個(gè)球柵陣列(BGA)。經(jīng)過(guò)批量回流焊后,焊球的高度為135 μm,間距為350 μm。頂部RDL中介層和底部RDL基板的尺寸均為12.5 x 12.5 mm2。包括焊球在內(nèi)的總封裝厚度為357 μm。表1匯總了測(cè)試樣品封裝的相關(guān)信息。

表1. 測(cè)試樣品的信息

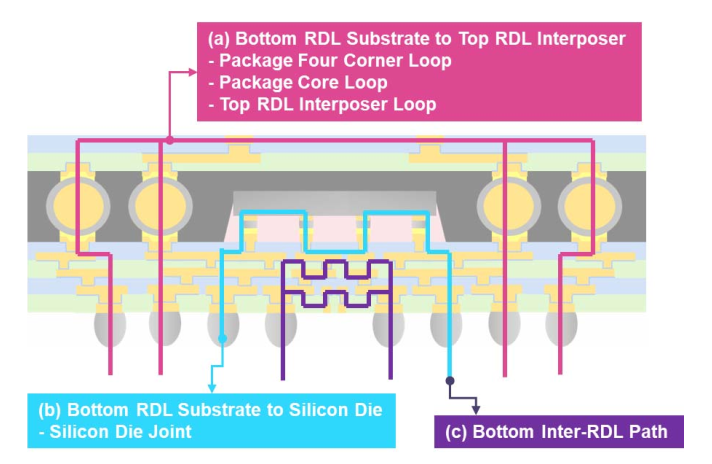

B菊花鏈設(shè)計(jì)

測(cè)試樣品中設(shè)有用于在可靠性測(cè)試前后進(jìn)行電氣開(kāi)路/短路(O/S)測(cè)試的菊花鏈。總共嵌入了七條菊花鏈,這些菊花鏈可以分為三條主要的互連路徑,如圖5所示:(a) 從底部RDL到頂部RDL,(b) 從底部RDL到硅片,(c) 底部RDL之間的互連路徑。

圖5. 三條菊鏈路示意圖

從底部RDL到頂部RDL的路徑通過(guò)三條菊花鏈檢查垂直連通性。這三條鏈中的一條環(huán)繞四個(gè)封裝角,這些區(qū)域是對(duì)熱循環(huán)測(cè)試最敏感的部位。另外兩條鏈分別用于封裝的核心區(qū)域和頂部RDL中介層區(qū)域。從底部RDL到硅片的路徑設(shè)計(jì)用于測(cè)試底部RDL基板與硅片之間的微凸點(diǎn)連接。最后一條路徑檢查底部RDL基板內(nèi)部的金屬互連線。這些菊花鏈幫助在可靠性測(cè)試前后識(shí)別故障位置。

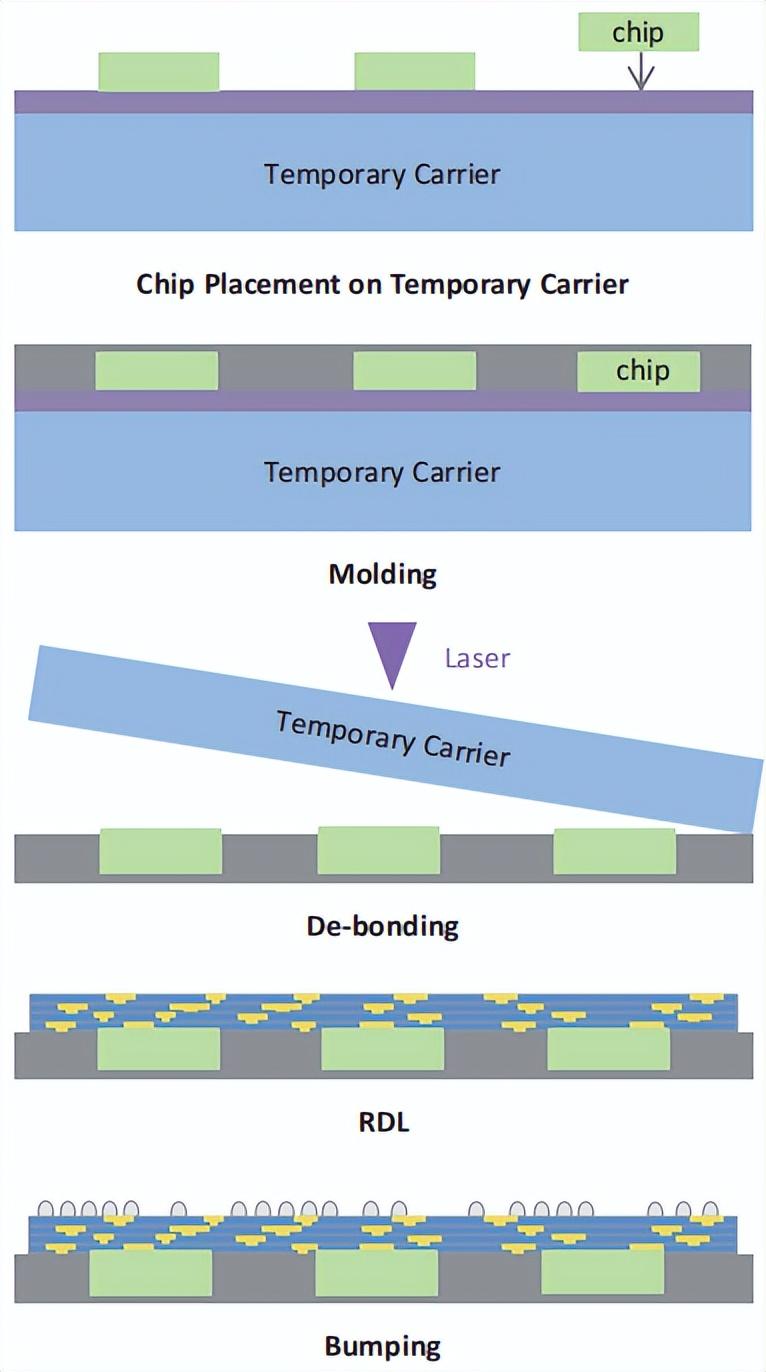

三、流程圖

A頂部和底部RDL的制備

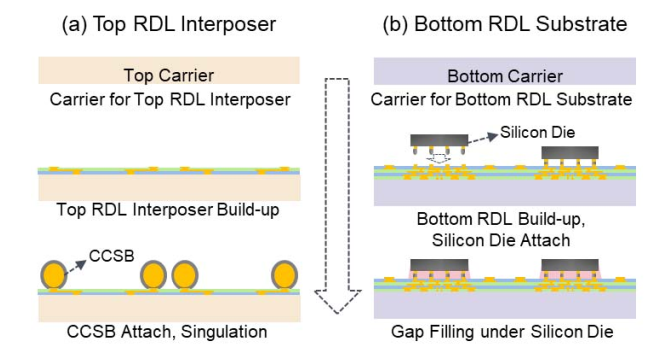

正如所提到的,這種新工藝的關(guān)鍵優(yōu)勢(shì)在于在芯片附著之前分別構(gòu)建頂部和底部RDL層。每個(gè)RDL層都在晶圓級(jí)別進(jìn)行準(zhǔn)備。圖6說(shuō)明了制備序列。晶圓充當(dāng)臨時(shí)載體,并將在最終制造階段被移除。

圖6. (a) 頂部RDL中介層的制備

(b) 底部RDL基板的制備

頂部RDL中介層由一層銅金屬線和用于CCSBs的凸塊下金屬(UBM)焊盤(pán)組成。有機(jī)鈍化材料封裝了金屬互連線。每個(gè)UBM焊盤(pán)上放置一個(gè)CCSB,并在晶圓級(jí)別進(jìn)行回流焊。如圖6-a所示。每個(gè)頂部RDL中介層隨后被單獨(dú)切割,以便以倒裝芯片方式附著到底部RDL基板晶圓上。

底部RDL基板有多層金屬線,各層金屬線之間使用了相同的有機(jī)材料。硅芯片以倒裝芯片方式鍵合到底部RDL晶圓上。通過(guò)在芯片附著前檢查底部RDL,可以確保硅芯片僅附著在已知良好的位置,從而避免在實(shí)際生產(chǎn)中損失昂貴的應(yīng)用特定集成電路(ASIC)芯片。由于底部RDL晶圓幾乎沒(méi)有翹曲,可以應(yīng)用傳統(tǒng)的批量回流焊工藝進(jìn)行倒裝芯片鍵合。如圖6-b所示,芯片與底部基板之間的間隙用底填材料填充。

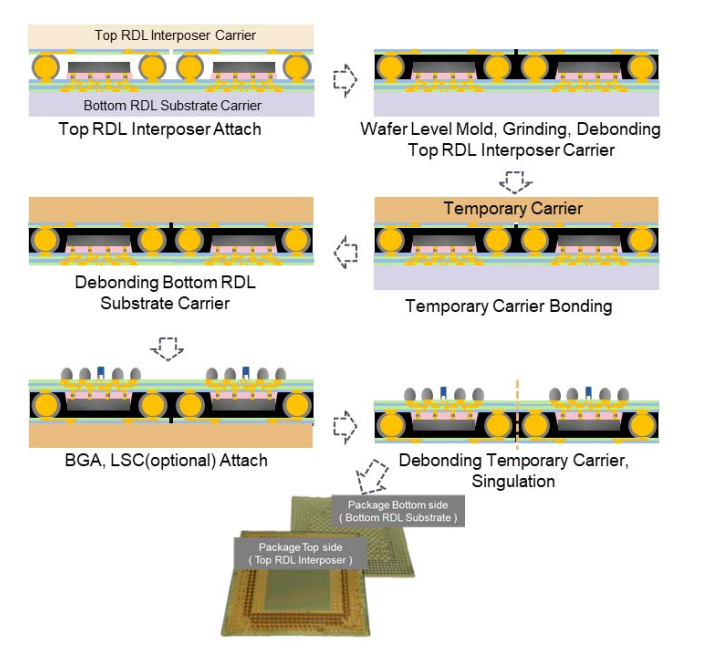

B頂部中介層與底部RDL基板的組裝

經(jīng)過(guò)分別制備后,單獨(dú)切割的頂部RDL中介層以倒裝芯片方式鍵合到底部RDL基板晶圓上,如圖7所示。所有樣品可以在鍵合前進(jìn)行檢查,以確保沒(méi)有缺陷,因此只有已知良好的頂部中介層附著在已知良好的底部基板位置上。這是將兩個(gè)RDL層分開(kāi)制備的一個(gè)關(guān)鍵優(yōu)勢(shì)。

圖7. 基于RDL的中介層PoP

帶CCSBs的工藝流程

在下一步中,通過(guò)在晶圓級(jí)別進(jìn)行的填膠工藝完成頂部和底部層之間的間隙填充。底真化合物完全填滿間隙,沒(méi)有空隙。然后,通過(guò)激光解粘工藝移除每個(gè)單獨(dú)的頂部RDL層上的晶圓片。為了進(jìn)行基板載體分離和BGA附著工藝,一個(gè)臨時(shí)載體被鍵合到頂部RDL層上。在通過(guò)批量回流焊工藝將BGA安裝到底部RDL基板上之后,對(duì)最終的單個(gè)封裝進(jìn)行了分割,以得到最終的單個(gè)封裝。。

四、關(guān)鍵技術(shù)和制造結(jié)果

基于RDL的集成PoP是使用以下三項(xiàng)關(guān)鍵技術(shù)制造的:

(a) 晶圓支持系統(tǒng)(WSS)

(b) RDL制造

(c) 用于垂直互連的銅芯焊球(CCSBs)

A晶圓支持系統(tǒng) (WSS)

薄的頂部和底部RDL層利用WSS技術(shù)同時(shí)進(jìn)行制備。臨時(shí)載體晶圓在RDL制造過(guò)程中作為支撐結(jié)構(gòu),因?yàn)镽DL層的厚度小于50 μm。大多數(shù)可用的WSS工藝在載體晶圓和RDL之間使用了一層犧牲層,以便于分離。犧牲層材料可以是液體或薄膜類型,它應(yīng)該能在高溫工藝中不發(fā)生任何降解或分層。分離方法包括熱滑動(dòng)、化學(xué)蝕刻、機(jī)械分離和激光輻照等。載體晶圓還需要在整個(gè)RDL加工過(guò)程中保持其平整度。因此,所有材料的特性和特性都應(yīng)仔細(xì)審查和測(cè)試,以確保穩(wěn)定的制造。

BRDL技術(shù)

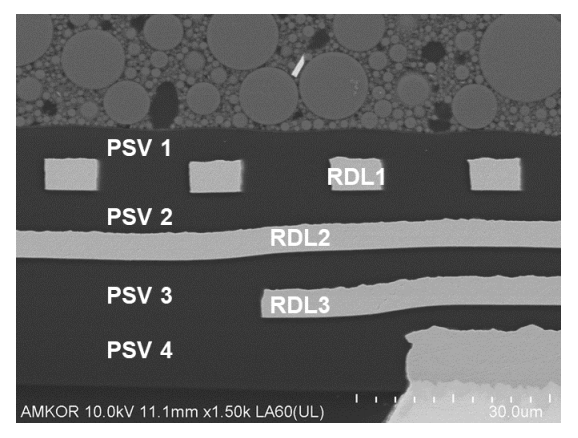

RDL技術(shù)的引入導(dǎo)致了中介層PoP在形狀因子和電訊號(hào)路徑的線寬/間距(L/S)方面的顯著變化。為了制造底部RDL基板,依次構(gòu)建了四層介電有機(jī)鈍化層和三層銅金屬線。最后,為硅片和CCSB附著電鍍了UBM焊盤(pán)。最小線寬/間距(L/S)為5 μm/10 μm,包含UBM在內(nèi)的總厚度為45 μm。圖8顯示了底部RDL基板的代表性橫截面圖像。

圖8. 底部RDL基板的截面圖像

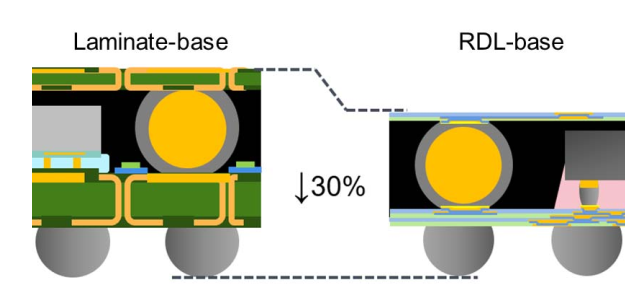

使用RDL構(gòu)建集成PoP的一個(gè)主要好處是減少了厚度。基于RDL的集成PoP的封裝厚度比傳統(tǒng)層壓基板封裝大約薄30%。圖9說(shuō)明了層壓基板和RDL集成PoP之間的厚度對(duì)比。

圖9. 層壓基板和基于RDL中介層

PoP之間的比較

CCCSB 作為垂直互連

CCSB(銅芯焊球)是頂部和底部RDL基板之間垂直互連的代表性組件之一。CCSB由三種材料構(gòu)成:銅芯球、鎳(Ni)層和焊料包覆層。CCSB的尺寸應(yīng)根據(jù)封裝高度和CCSB著陸焊盤(pán)的間距/直徑來(lái)選擇,以避免在CCSB放置過(guò)程或頂部中介層鍵合過(guò)程中出現(xiàn)焊料橋接或不潤(rùn)濕問(wèn)題。圖10顯示了基于RDL的集成PoP測(cè)試樣品的橫截面圖像。

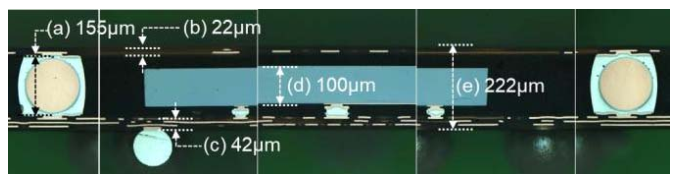

圖10. 橫截面圖像

a) CCSB(銅芯焊球)

b) 頂部RDL中介層

c) 底部RDL中介層

d) 硅片

e) 除BGA外的封裝厚度硅模

五、可靠性性能

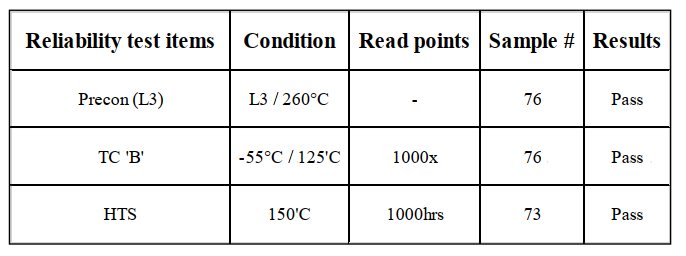

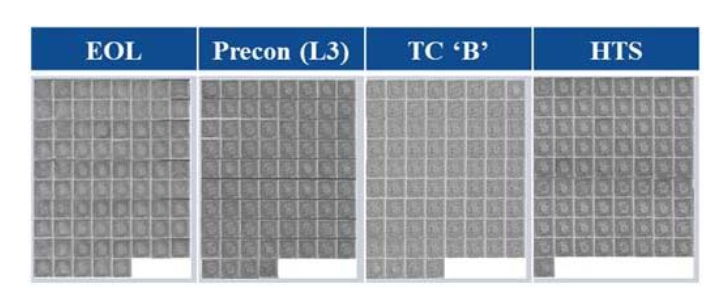

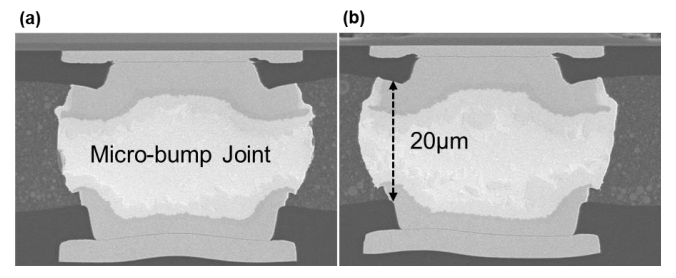

對(duì)基于RDL的集成PoP測(cè)試樣品進(jìn)行了組件級(jí)可靠性(CLR)測(cè)試。測(cè)試按照J(rèn)EDEC標(biāo)準(zhǔn)執(zhí)行,如表1所示。測(cè)試樣品通過(guò)了以下所有要求:(a) 在濕氣敏感性測(cè)試(Precon)L3/260°C條件下的1,000次熱循環(huán)(TC)條件B,(b) 不進(jìn)行預(yù)處理(Precon)的1,000小時(shí)高溫存儲(chǔ)(HTS)。表2顯示了可靠性測(cè)試項(xiàng)目、條件、樣本數(shù)量和結(jié)果。所有樣品通過(guò)了電氣開(kāi)路/短路(O/S)測(cè)試和掃描聲學(xué)斷層成像(SAT)測(cè)試(見(jiàn)圖11)。圖12和13展示了經(jīng)過(guò)熱循環(huán)‘B’和高溫存儲(chǔ)測(cè)試后的微凸點(diǎn)連接和CCSBs的橫截面圖像。所有連接在所有可靠性測(cè)試后均未顯示出任何異常。

表2. 可靠性試驗(yàn)條件和結(jié)果

所有樣品都通過(guò)電氣0/S測(cè)試和掃描聲學(xué)層析成像SAT)測(cè)試進(jìn)行了檢查(見(jiàn)圖11)。圖12和13顯示了TC'B'和HTS測(cè)試后微凸點(diǎn)接點(diǎn)和CCSB的橫截面圖像。在所有可靠性測(cè)試后,沒(méi)有異常。

圖11. 聲學(xué)掃描圖像

圖12. 硅片微凸點(diǎn)連接的橫截面圖像

a) TC ‘B’ 1000次循環(huán)(使用Precon L3)

b) HTS 1000小時(shí)后

圖13. CCSB連接的橫截面圖像

a) TC ‘B’ 1000次循環(huán)(帶Precon L3)

b) HTS 1000小時(shí)后

六、結(jié)論

開(kāi)發(fā)了一種基于RDL的新型集成POP工藝,并通過(guò)可靠性測(cè)試進(jìn)行了評(píng)估。由于僅連接到已知良好的位置因此頂部和底部RDL的單獨(dú)構(gòu)建可以最小化硅芯片損失,從而降低成本。此外,由于兩個(gè)RDL是并行制造的,因此縮短了組裝周期時(shí)間。與從一側(cè)RDL到另一側(cè)RDL的順序構(gòu)建過(guò)程相比,其優(yōu)點(diǎn)如下:

●提高產(chǎn)量管理能力:通過(guò)臨時(shí)測(cè)試?yán)L制已知良好位置,可進(jìn)行選擇性組裝,最大限度減少良好芯片的損失。

●縮短周期時(shí)間:分別并行制作頂部和底部RDL。

●減少形狀因數(shù):基于RDL的綜合PoP比目前大規(guī)模生產(chǎn)的基于層壓板的綜合Pop薄30%。

-

芯片

+關(guān)注

關(guān)注

456文章

51120瀏覽量

426009 -

晶圓

+關(guān)注

關(guān)注

52文章

4963瀏覽量

128189 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

553瀏覽量

68008 -

封裝工藝

+關(guān)注

關(guān)注

3文章

58瀏覽量

8001

原文標(biāo)題:一種新型RDL PoP扇出晶圓級(jí)封裝工藝芯片到晶圓鍵合技術(shù)

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

HRP晶圓級(jí)先進(jìn)封裝替代傳統(tǒng)封裝技術(shù)研究(HRP晶圓級(jí)先進(jìn)封裝芯片)

什么是晶圓級(jí)封裝?

晶圓凸起封裝工藝技術(shù)簡(jiǎn)介

用于扇出型晶圓級(jí)封裝的銅電沉積

激光解鍵合在扇出晶圓級(jí)封裝中的應(yīng)用

扇出型晶圓級(jí)封裝技術(shù)的優(yōu)勢(shì)分析

一種新型RDL PoP扇出晶圓級(jí)封裝工藝芯片到晶圓鍵合技術(shù)

一種新型RDL PoP扇出晶圓級(jí)封裝工藝芯片到晶圓鍵合技術(shù)

評(píng)論