0 引言

流水線模數(shù)轉(zhuǎn)換器(pipeline ADC)是中高精度(10~14 bit)高速(10~500 MS/s)ADC的主流實現(xiàn)結(jié)構(gòu),被廣泛應(yīng)用于通信系統(tǒng)、圖像設(shè)備、視頻處理等系統(tǒng)中。作為其前端最關(guān)鍵的模塊,采樣保持電路的性能直接決定了整個ADC的性能,在以上系統(tǒng)中對功耗的要求十分嚴(yán)格。本設(shè)計在實現(xiàn)高速高精度采樣保持功能的同時,還實現(xiàn)了MDAC功能,這樣既能降低ADC功耗又能減少芯片面積。

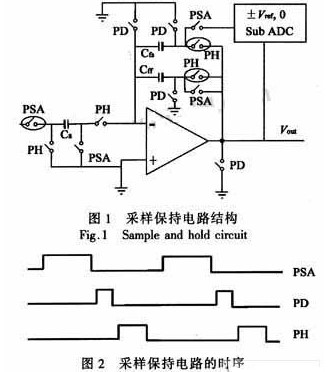

1 采樣保持電路結(jié)構(gòu)

傳統(tǒng)流水線ADC的最前面為一級采樣保持電路其后接MDAC級。采樣保持電路能夠較好地減小由于MDAC和子ADC之間的采樣信號失配造成的孔徑誤差。由于采保電路位于整個ADC的最前端,對其精度要求最高,故該模塊需要消耗較大的功耗通常為整個ADC功耗的20%~30%,并且會降低ADC的動態(tài)范圍和線性度。流水ADC是在雙向非交疊時鐘的控制下工作,相鄰的采樣保持電路和第一級MDAC總是工作在不同的狀態(tài),采樣或保持。每個模塊只是在保持狀態(tài)需要運放參與工作。這樣采樣保持和第一級MDAC可以分時復(fù)用同一個運放,達(dá)到降低功耗并減少面積的目的。

基于以下原因MDAC級選擇了1.5 bit/級。首先,每級有1 bit冗余位來進(jìn)行數(shù)字冗余修正,大大減小比較器失調(diào)造成的影響;其次,1.5 bit/級結(jié)構(gòu)的單級閉環(huán)增益為2,開關(guān)電容電路可以具有較小的負(fù)載電容和較大反饋因子,較小的單級分辨率可以獲得較高的速度。

圖1為本設(shè)計的采樣保持電路結(jié)構(gòu),圖2為其時序,加圈處為自舉開關(guān)。采樣保持電路在3相時鐘的控制下,工作于3種不同的狀態(tài),采樣/放大、復(fù)位、保持。

具體工作原理如下:當(dāng)PSA為高電平時電路工作于采樣/放大狀態(tài),輸入信號被采樣至電容Cs上

Ql=Vin·Cs (1)

運算放大器和電容Cff,Cfs及子ADC構(gòu)成MDAC結(jié)構(gòu),處于保持狀態(tài);當(dāng)PD為高電平時電路工作于復(fù)位狀態(tài),Cs完成對輸入信號的采樣,輸入電荷存于Cs上。運放及Cff,Cfs處于復(fù)位狀態(tài),運放輸入端短接,輸出端短接,電容兩端短接,消除電路的記憶效應(yīng),為下一狀態(tài)做準(zhǔn)備。當(dāng)PH為高電平時電路處于保持狀態(tài),運算放大器呈ChargeTransferring型采保連接形式,輸出電平與采樣電平值接近,輸人電荷轉(zhuǎn)移到Cff,Cfs上

Q2=Q1 (2)

取Cff=Cfs=0.5 Cs,運放的輸出進(jìn)入子ADC;當(dāng)PSA為高電平時,Cfr跨接在運放兩端,Cfs與DAC的輸出模擬電平相連,電路呈現(xiàn)減法放大功能

Q3=Vout·Cff+Vdac(D)·Cfs (3)

由于PH和PSA兩個相位運算放大器的輸入始終處于虛地狀態(tài),根據(jù)電荷守恒Q2=Q3,得到當(dāng)Cff=Cfs時,就實現(xiàn)了1.5 bit/級MDAC的減法、放大功能。

與傳統(tǒng)的采樣保持電路相比,新型結(jié)構(gòu)的優(yōu)勢在于:在一個時鐘周期內(nèi),單級模塊在實現(xiàn)采樣保持功能的同時,還實現(xiàn)了一級MDAC功能;電容Cff,Cfs在保持相和減法放大相實現(xiàn)了復(fù)用,降低了功耗和面積;同一運放分時復(fù)用于保持相和減法放大相,降低了功耗和面積;與無采保結(jié)構(gòu)的ADC相比,由于保持相的存在,消除了運放與比較器輸入端信號路徑延時不等的影響,在降低功耗的同時,動態(tài)性能沒有下降。

使用這種結(jié)構(gòu)需要注意的幾個問題:①精度問題。由于PD相的存在,在本設(shè)計中PH的時間由傳統(tǒng)的兩相非交疊11.2 ns縮短為8.4 ns,保持相時間內(nèi)運放是否能建立到要求的精度范圍。因為電容Cff,Cfs在PSA和PH相的復(fù)用減少了PH相時運放所帶的負(fù)載,在1.5 bit結(jié)構(gòu)中運放的負(fù)載為

Cload=(1-β)Cfn+Csn+1 (5)

式中:β為反饋系數(shù),縮減因子取為0.5;Cload=1.5Cfn。新結(jié)構(gòu)中

Cload=(1-β)Cfn=0.5 Cfn (6)

負(fù)載減少了60%,時間只縮短了25%,所以可建立到指定精度。因該階段把采樣的電荷轉(zhuǎn)移到了Cff,Cfs,發(fā)生了一次運算,故輸出需達(dá)到12 bit的精度,輸出端誤差應(yīng)滿足ε≤1/212。②功耗問題。由于負(fù)載減少的程度大于建立時間減少的程度,所以并不需要增加單個運放的功耗。③穩(wěn)定性問題。在PH和PSA相時,運放需要工作在兩個不同的反饋環(huán)路中,對于本設(shè)計選擇的1.5 bit/級結(jié)構(gòu),每個環(huán)路中運放的反饋系數(shù)都為0.5,所以兩個狀態(tài)電路電路都容易達(dá)到穩(wěn)定。當(dāng)把本結(jié)構(gòu)推廣到每級2.5 bit或以上結(jié)構(gòu)時,在PSA相的反饋系數(shù)將小于0.5,運放的帶寬和極點位置就需仔細(xì)考慮,以確保電路的每個狀態(tài)都是穩(wěn)定的。

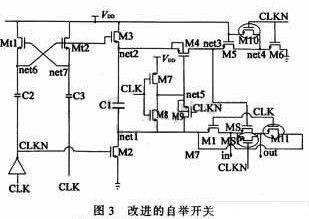

2 改進(jìn)的自舉開關(guān)設(shè)計

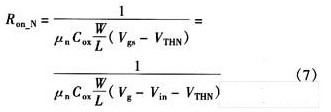

在模數(shù)轉(zhuǎn)換器的設(shè)計中,由于模擬信號是先通過采樣開關(guān),再進(jìn)人ADC轉(zhuǎn)換電路的,因此,采樣保持電路中接輸入模擬信號的采樣開關(guān)的設(shè)計也十分重要。NMOS管的導(dǎo)通電阻可用式(7)表示,其大小與柵源電壓成反比。在低電壓電路中利用電荷泵提高時鐘電壓,可以減小電阻,但卻不能消除由于輸入電壓變化而引起的非線性失真。當(dāng)柵源電壓超過電源電壓時,會導(dǎo)致器件可靠性不高。

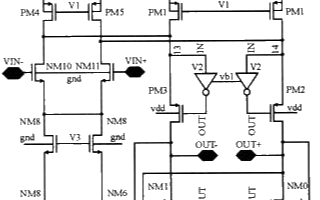

為了減少主要來自于開關(guān)的導(dǎo)通電阻、寄生電容和溝道注入電荷與輸入信號的相關(guān)性引起的非線性失真,設(shè)計的采樣保持電路采用了改進(jìn)的柵壓自舉開關(guān),如圖3所示,在傳統(tǒng)的自舉開關(guān)的基礎(chǔ)上增加了M10,M11,MSP三個MOS管。自舉開關(guān)用在圖1加圈的開關(guān)處。

電路第一個改進(jìn)是增加M11。MS左右兩邊并不對稱,當(dāng)開關(guān)閉合時in和out兩邊泄漏的電荷并不相等,會影響采樣電容上的電荷。通過增加M11令其尺寸和Ml相同,改為對稱結(jié)構(gòu)如圖所示可以解決這一問題。并且讓M1和M11的柵直接由CLK信號控制而不是像傳統(tǒng)結(jié)構(gòu)中那樣與MS的柵相連,這使得他們比MS稍微提前一點關(guān)斷,會減少MS釋放的電荷數(shù)量,提高采樣的精度。增加M11帶來的另一個好處是提高了MS的可靠性。若沒有M11,在MS導(dǎo)通瞬間必須確保其漏端電壓比源端電壓高,使柵漏之間的電壓不大于VDD。增加M11后,電路變?yōu)閷ΨQ結(jié)構(gòu),源漏電壓相等,電路在滿幅度工作時,柵源柵漏電壓都不會大于VDD提高了可靠性。

電路第二個改進(jìn)是增加M10。在傳統(tǒng)自舉開關(guān)中,M5和M6的作用是在CLKN為高時,給MS的柵電容提供一條放電的通路。M5是為了提高M(jìn)6的可靠性而增加的器件,CLKN為高時可以減少M6的Vds和Vgs。在CLK相M5管處于導(dǎo)通狀態(tài),M6管處于截止?fàn)顟B(tài),并且net3電壓很高為(VDD+Vin),因此沿M5和M6存在著電荷泄漏通路,影響MS的Vgs,導(dǎo)致噪聲。因此本設(shè)計對其做了改進(jìn),增加M10管,使得在CLK為高時,M5管處于可靠的關(guān)閉狀態(tài)。這樣帶來了兩點好處:第一是有效地減小了泄漏電流;第二是通過在CLK為高時關(guān)閉M7管,減小了M7的電容,從而減小了與C1相關(guān)的寄生電容,使MS能得到更高的Vgs,提高信噪比。

電路的第三個改進(jìn)是增加了MSP管。MS的導(dǎo)通電阻,會受到體效應(yīng)的影響而變化,影響采樣的精度。并聯(lián)尺寸很小的MSP管可以很明顯地減小導(dǎo)通電阻,減少輸入信號和體效應(yīng)對其的影響,同時可以提高整個電路的線性度。采用改進(jìn)結(jié)構(gòu)后自舉開關(guān)在線性方面與傳統(tǒng)結(jié)構(gòu)相比有8 dB的提高,后仿結(jié)果SFDR為86.83 dB,SNDR為75.229 dB,符合12 bit要求。

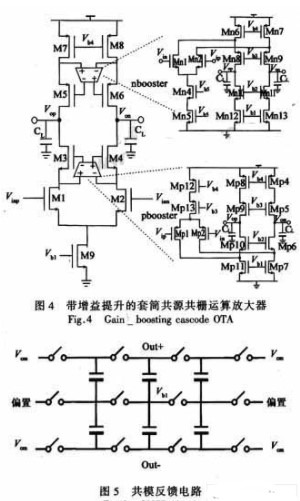

3 運算放大器的設(shè)計

運算放大器是本設(shè)計的最核心部分。運算放大器采用帶增益提升的套筒式共源共柵結(jié)構(gòu),這是由于所需增益比較大(大于80 dB),單級放大器達(dá)不到所需的增益,而采用兩級結(jié)構(gòu)會出現(xiàn)相位的補償問題,并且功耗也比較大,所以本設(shè)計選擇帶增益提升的套筒共源共柵運算放大器如圖4。由于本設(shè)計的運放在兩個時鐘狀態(tài)下都要工作,其開關(guān)共模反饋結(jié)構(gòu)如圖5所示。整個ADC的設(shè)計要求信號輸出擺幅為2 V,套筒共源共柵運放也完全可以滿足要求。

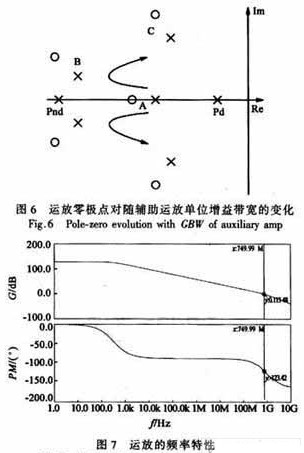

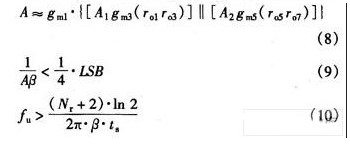

pbooster和nbooster分別為增益增強的輔助運放,采用折疊式共源共柵結(jié)構(gòu),增益增強技術(shù)引入輔助放大器極大地提高了主放大器的增益如公式(8)所示,但是它也在放大器的傳輸函數(shù)中引入了一對零極點對(pole zero doublet),它會影響放大器的時域響應(yīng),在跨導(dǎo)運算放大器的設(shè)計過程中,使用Matlab分析發(fā)現(xiàn)運放的極點隨輔助運放帶寬的增加,會由A到B到C變化如圖6所示,仔細(xì)優(yōu)化兩個輔助運算放大器的單位增益帶寬,把運放的極點推向較高的頻率如圖所示,可以減小增益自舉運算放大器中零極點對對大信號階躍響應(yīng)的影響,使電路達(dá)到較快的穩(wěn)定。對于12 bit 40 MS/s的要求,由公式(9)和(10)計算并留有一定的預(yù)度,運放需要84 dB增益、300 MHz的帶寬。公式(9)中A為放大倍數(shù),β為反饋系數(shù)。公式(10)中fu為單位增益帶寬;Nr為有效位數(shù);ts為半個時鐘周期。負(fù)載為2 pF時,運放的整個頻率響應(yīng)如圖7所示,直流增益為131 dB,單位增益帶寬為783 MHz,相位裕度為75°,符合12 bit 40 MS/s的要求。

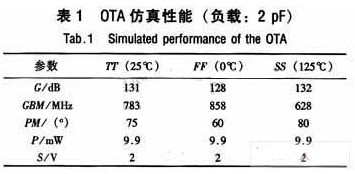

不同工藝轉(zhuǎn)角TT,F(xiàn)F,SS和溫度下,運放性能如表1所示。表中:G為增益;GBW為增益帶寬;PM為相位裕度;P為功耗;S為擺幅。

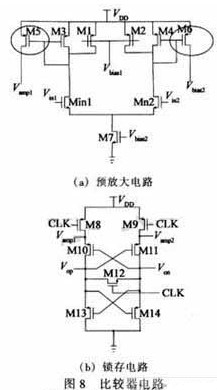

4 比較器

由于本設(shè)計要達(dá)到12 bit的精度要求,為了能夠抑制回程干擾,在鎖存器前面加了一級預(yù)放大器。為了消除預(yù)放大器自身的失調(diào)電壓,可在比較器的鎖存階段將預(yù)放大器接成單位增益負(fù)反饋的形式,達(dá)到失調(diào)消除的目的。蒙特卡羅分析表明,該比較器輸入失調(diào)電壓10 mV,滿足小于1/4 Vref,250 mV的失調(diào)范圍要求。比較器電路如圖8所示。

5 仿真結(jié)果

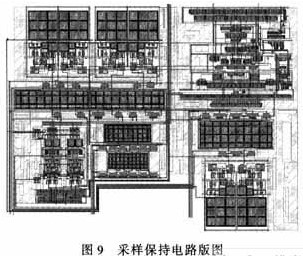

本設(shè)計的采樣保持電路采用TSMC 0.35μmCMOS標(biāo)準(zhǔn)工藝設(shè)計。使用Cadence和HSPICE進(jìn)行仿真驗證,電路在0~125℃內(nèi),在各種Comer下均能正常工作。電路在40 MHz采樣頻率工作時功耗僅為14 mW。電路的版圖如圖9所示。

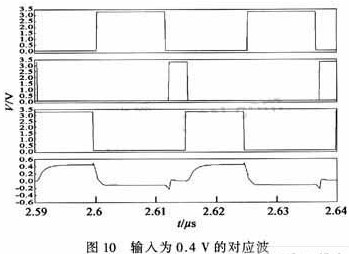

圖10為在輸入為直流0.4 V時,SMDAC模塊的輸出及所對應(yīng)的時序,在PH相時輸出應(yīng)為0.6 V,PD相時輸出應(yīng)為0 V,PSA相時輸出應(yīng)為

Vout=2×Vin-Vdac(D)=2×0.6-1=0.2 V,輸出值與計算值一致,驗證了電路功能的正確性。

在采樣頻率為40 MHz,輸入信號為19 MHz的滿幅度正弦信號(Vpp=2 V)對電路進(jìn)行后仿真。對所得的輸出信號進(jìn)行1024點快速傅里葉變換的頻譜如圖11所示,SNDR=73.22 dB,ENOB=11.87 bit,SFDR=89.34 dB。

6 結(jié)論

本文采用TSMC 0.35μm mix signal 3.3 V工藝沒計了一個高性能低功耗的采樣保持電路,可作為12 bit 40 MHz采樣頻率的流水線A/D轉(zhuǎn)換器的前端模塊。通過對運放的分時復(fù)用,一個電路模塊既實現(xiàn)了采樣保持功能,又實現(xiàn)了MDAC功能。而實現(xiàn)該指標(biāo)的MDAC所需功耗為9 mW,與普通結(jié)構(gòu)相比在達(dá)到同樣指標(biāo)的情況下,可減少了9 mW。通過對傳統(tǒng)柵壓自舉開關(guān)改進(jìn),減少電路的非線性失真。通過優(yōu)化輔助運放的寬帶,設(shè)計了高增益快速穩(wěn)定的OTA。在40 MHz采樣頻率下,以奈奎斯特采樣頻率滿幅(Vpp=2 V)信號輸入,其SFDR=85 dB,SNDR=72 dB,ENOB=11.6 bit。整個電路消耗的動態(tài)功耗為14 Mw。

-

運算放大器

+關(guān)注

關(guān)注

215文章

4966瀏覽量

173377 -

adc

+關(guān)注

關(guān)注

99文章

6533瀏覽量

545436 -

低功耗

+關(guān)注

關(guān)注

10文章

2418瀏覽量

103838

發(fā)布評論請先 登錄

相關(guān)推薦

汽車ECU的低功耗高性能實現(xiàn)

一種基于視頻處理系統(tǒng)的12位25MS/s低功耗采樣保持電路介紹

怎么實現(xiàn)低功耗單芯片高性能音頻CODEC的設(shè)計?

基于ZU3EG的低功耗高性能嵌入式AI高性能計算模組

適用于流水線ADC的高性能采樣保持電路

高性能中頻采樣系統(tǒng)的設(shè)計與實現(xiàn)

低功耗ADC實現(xiàn)高性能明智設(shè)計

在16位、100kSPS數(shù)據(jù)采集系統(tǒng)中實現(xiàn)低功耗和高性能

汽車中的各種ECU,如何實現(xiàn)低功耗、高性能

采用全差分結(jié)構(gòu)的高性能采樣/保持電路的設(shè)計

AD9251集成高性能采樣保持電路和片內(nèi)電壓基準(zhǔn)出

設(shè)計低功耗和高性能的工業(yè)應(yīng)用

高性能低功耗的采樣保持電路的設(shè)計與實現(xiàn)

高性能低功耗的采樣保持電路的設(shè)計與實現(xiàn)

評論