本周結(jié)合文獻(xiàn)進一步學(xué)習(xí)了pipeline ADC的實現(xiàn)原理及基本結(jié)構(gòu),主要參考了西電、成電和東南的幾篇pipelined ADC的碩士論文以及S.H.Lewis的”A pipelined 5-Msample/s Analog-to-Digital Convertor”,以下為個人筆記。

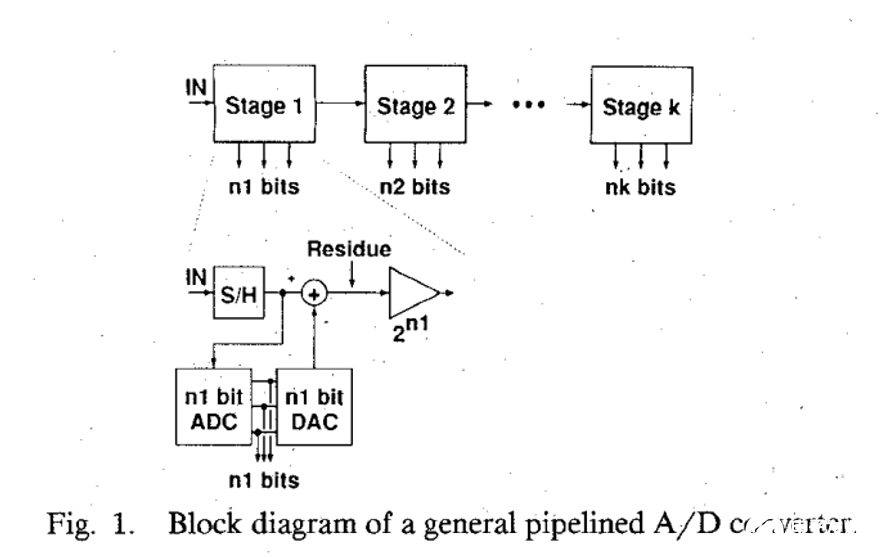

Pipeline ADC的結(jié)構(gòu)圖如上圖所示,它是由多級相同單元組成的一種ADC結(jié)構(gòu),每級都進行一次粗量化,輸出最終轉(zhuǎn)換出數(shù)字量中的幾位,第一級為高位,后級輸出低位,而總的分辨率,也就是位數(shù)就等于所有流水級減掉冗余位后的有效位數(shù)之和。

此結(jié)構(gòu)的優(yōu)越性主要有二:

1.與flash或subranging ADC相比,它的面積更小,功耗更低,這是由于此種結(jié)構(gòu)需要的器件數(shù)與分辨率是線性關(guān)系,需要更高的分辨率只需要再添加更多流水級,而另兩種類型若想要更高分辨率,比較器的數(shù)量呈指數(shù)上升。

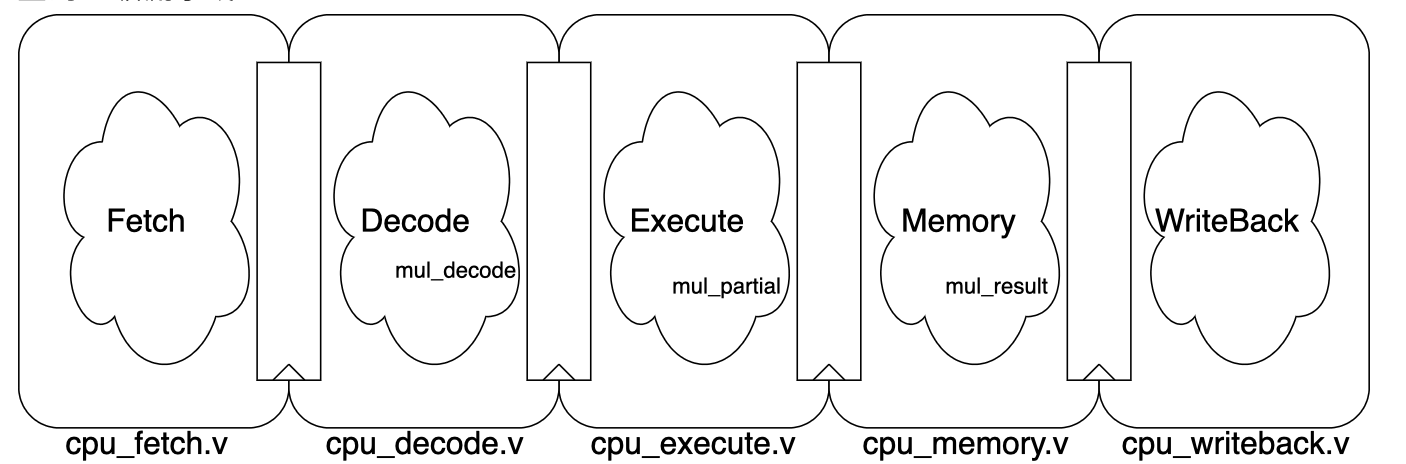

2.流水線結(jié)構(gòu)顧名思義,與流水線CPU相似,每個子級都是并發(fā)執(zhí)行的,當(dāng)?shù)谝患壴诹炕丝梯斎氲臄?shù)據(jù)時,第二級正在量化上個周期輸入的數(shù)據(jù),以此類推,這樣一來就將ADC轉(zhuǎn)換速度與分辨率獨立開來,無論有多少個子級多少位的分辨率,數(shù)據(jù)都是連續(xù)輸入連續(xù)輸出的,相鄰數(shù)據(jù)僅相差一個周期。

接下來簡述單個子級的結(jié)構(gòu)及原理。假設(shè)單級的分辨率為n,它由S/H電路、n位的子ADC、n位的子DAC、減法器以及乘法器構(gòu)成,一般也將n位的子DAC、減法器以及乘法器統(tǒng)稱為MDAC(multiplying DAC)。

首先,S/H電路采樣并保持輸入電壓,輸送給子ADC,子ADC進行n位的粗量化,輸出高n位的數(shù)字量,之后將量化出的n位數(shù)字量再經(jīng)過一個n位子DAC得到粗量化出的模擬量,將實際輸入的模擬量減去這個粗量化出的模擬量,得到的值為剩余的需要繼續(xù)進行量化的模擬量,稱為殘差或余差(residue),之后為了后級能夠繼續(xù)使用相同的子級進行量化,需要將這個殘差放大到滿量程上,放大倍數(shù)為2n。

這里使用數(shù)字量來代替模擬量進行理解會更加容易。需要注意,一般對于pipelined ADC來說,輸出的數(shù)字量0代表負(fù)的權(quán)重,1代表正的權(quán)重。舉個簡單的例子,假設(shè)整個ADC的分辨率為6位,輸入所對應(yīng)的數(shù)字量D正好為6’b101101,首級為2位,理想情況下,首級將轉(zhuǎn)換出10這個數(shù)碼,轉(zhuǎn)換之后剩下待轉(zhuǎn)換的量用數(shù)字量表示為6’bzz1101,這里用z表示權(quán)重為0,那么為了使用一致的子級結(jié)構(gòu)進行轉(zhuǎn)換,需要將這個值向左移兩位,對應(yīng)于算數(shù)運算就是乘以4,即乘以22,之后再送入下一級進行量化,得到11,求出殘差乘以4送至下一級,以此類推。

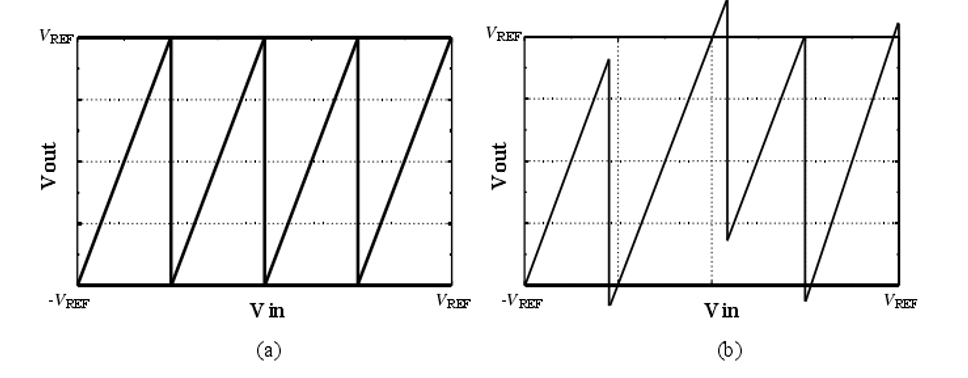

2-bit單級的輸入輸出特性如下圖所示,對應(yīng)于00、01、10、11四個范圍,當(dāng)輸入小于0時,說明最高位必須為0,輸入大于0時,最高位必須為1,而當(dāng)輸入小于-VREF/2時,次高位也必須為0(考慮0100000…這個量,它只能逼近-VREF/2而無法小于),其他區(qū)間類似可得。比較器判決電壓為-VREF/2、0、VREF/2。

那么就可以得到每一輸入?yún)^(qū)間對應(yīng)該級的子DAC轉(zhuǎn)換出的量,分別為-3/4 VREF、-VREF/4、VREF/4、3/4 VREF。

簡單分析動態(tài)過程,當(dāng)Vin = -VREF時,對應(yīng)Vout = 4 * (-VREF – (-3/4 VREF)) =-VREF。隨著Vin增加,轉(zhuǎn)換出的數(shù)碼為00不變,因此Vout隨Vin正比例增加,斜率為級間增益4,當(dāng)Vin越過第一個判決電壓-VREF/2,轉(zhuǎn)換出數(shù)碼跳變?yōu)?1,Vout也跳變到-VREF,注意這里也體現(xiàn)出了級間增益將殘差放大到滿量程的效果,Vin繼續(xù)增大,Vout依舊是以4為斜率正比例增加,之后的區(qū)間類似。

我們注意到,如果子ADC中比較器的判決電壓存在偏移,如(b)圖所示,就會引入誤差,導(dǎo)致誤碼甚至失碼的現(xiàn)象。然而,在MDAC是理想的的情況下,如果這個錯誤的殘差輸出沒有超過下一級的量程,實際上這個模擬量的信息還是完整地被保存下來了,因此,如果提高下一級的量程,就可以對這個溢出的殘差進行轉(zhuǎn)換了。

這里的解釋不夠準(zhǔn)確,感興趣的朋友可以去看我的筆記(二)

實際上,在pipelined ADC中通常采用數(shù)字校準(zhǔn)技術(shù),通過使用冗余位,來對易錯區(qū)間進行單獨劃分。其原理與提高量程有異曲同工之妙。以下對此技術(shù)進行簡要解釋。

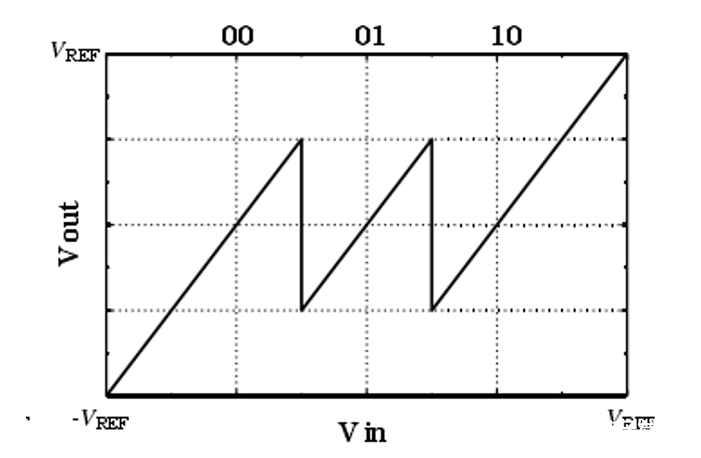

為簡單起見,考慮一個1位的流水級,采用了0.5位冗余的輸入輸出特性曲線如下圖所示。可以看到,對應(yīng)于未加入冗余位的結(jié)構(gòu),它多出了一個轉(zhuǎn)換區(qū)間,包含00、01、10三個區(qū)間,其中高位為有效位,而低位是冗余位,高位的權(quán)重為VREF/2,低位的權(quán)重為VREF/4,有意思的是,該級有效的權(quán)重就是VREF/2,多出來的VREF/4權(quán)重的位卻被保留下來輸送給下一位了。觀察原來的錯誤源頭,當(dāng)輸入接近判決電壓0時,若判決電壓存在偏移,輸入會被誤判到另一個數(shù)字輸出的區(qū)間,產(chǎn)生誤碼,同時輸出余差超出下級量程,那么如果將接近判決電壓的部分區(qū)域再分出一個區(qū)間,認(rèn)為此區(qū)間容易出錯因此不加以判斷,留到后面再進行判斷,就可以避免出現(xiàn)錯誤的現(xiàn)象了。若想要多劃分出區(qū)間,就需要增加該級的位數(shù),這也就是冗余碼的原理。

需要注意的是,冗余碼的權(quán)重實際上是下一級有效碼的權(quán)重,那么用該級冗余碼與下一級有效數(shù)碼相加,得到的進位就是該級的糾正碼,留下的和就是下一級的結(jié)果。實際上,所有流水級的結(jié)果將冗余碼錯位再相加就得到了正確的轉(zhuǎn)換結(jié)果,將比較器判決電壓偏移導(dǎo)致的錯誤消除了。

審核編輯:黃飛

-

adc

+關(guān)注

關(guān)注

99文章

6531瀏覽量

545393 -

比較器

+關(guān)注

關(guān)注

14文章

1658瀏覽量

107352 -

dac

+關(guān)注

關(guān)注

43文章

2308瀏覽量

191342 -

模擬量

+關(guān)注

關(guān)注

5文章

494瀏覽量

25606 -

輸入電壓

+關(guān)注

關(guān)注

1文章

506瀏覽量

16597

發(fā)布評論請先 登錄

相關(guān)推薦

pipeline ADC的實現(xiàn)原理及基本結(jié)構(gòu)(2)

STM32F1 ADC主要特性和結(jié)構(gòu)框圖

STM32F1 ADC主要特性和結(jié)構(gòu)框圖

pipeline ADC的實現(xiàn)原理及基本結(jié)構(gòu)筆記分享

Pipeline ADCs Come of Age

Pipeline ADCs Come of Age

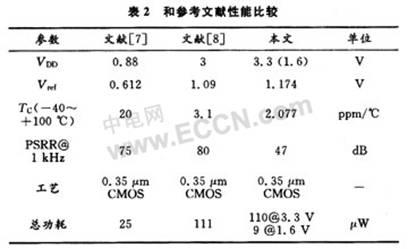

14位Pipeline ADC設(shè)計的帶隙電壓基準(zhǔn)源技術(shù)

STM32F1----ADC

SpinalHDL里pipeline的設(shè)計思路

核芯互聯(lián)最新推出一款 Pipeline結(jié)構(gòu)的模數(shù)轉(zhuǎn)換器(ADC)

pipeline ADC的實現(xiàn)原理及基本結(jié)構(gòu)(1)

pipeline ADC的實現(xiàn)原理及基本結(jié)構(gòu)(1)

評論