之前有系列文章介紹了SpinalHDL中Pipeline的使用,最近在一個(gè)功能模塊中真實(shí)的使用了這個(gè)lib。雖然在使用上基于Flow/Stream的抽象已基本滿足大多數(shù)使用場(chǎng)景,但在FPGA端有時(shí)為了優(yōu)化時(shí)序往往不得不做一些邏輯打散,此時(shí)發(fā)現(xiàn)Pipeline中的標(biāo)準(zhǔn)化組件就有點(diǎn)難以滿足需求了。

》舉個(gè)例子

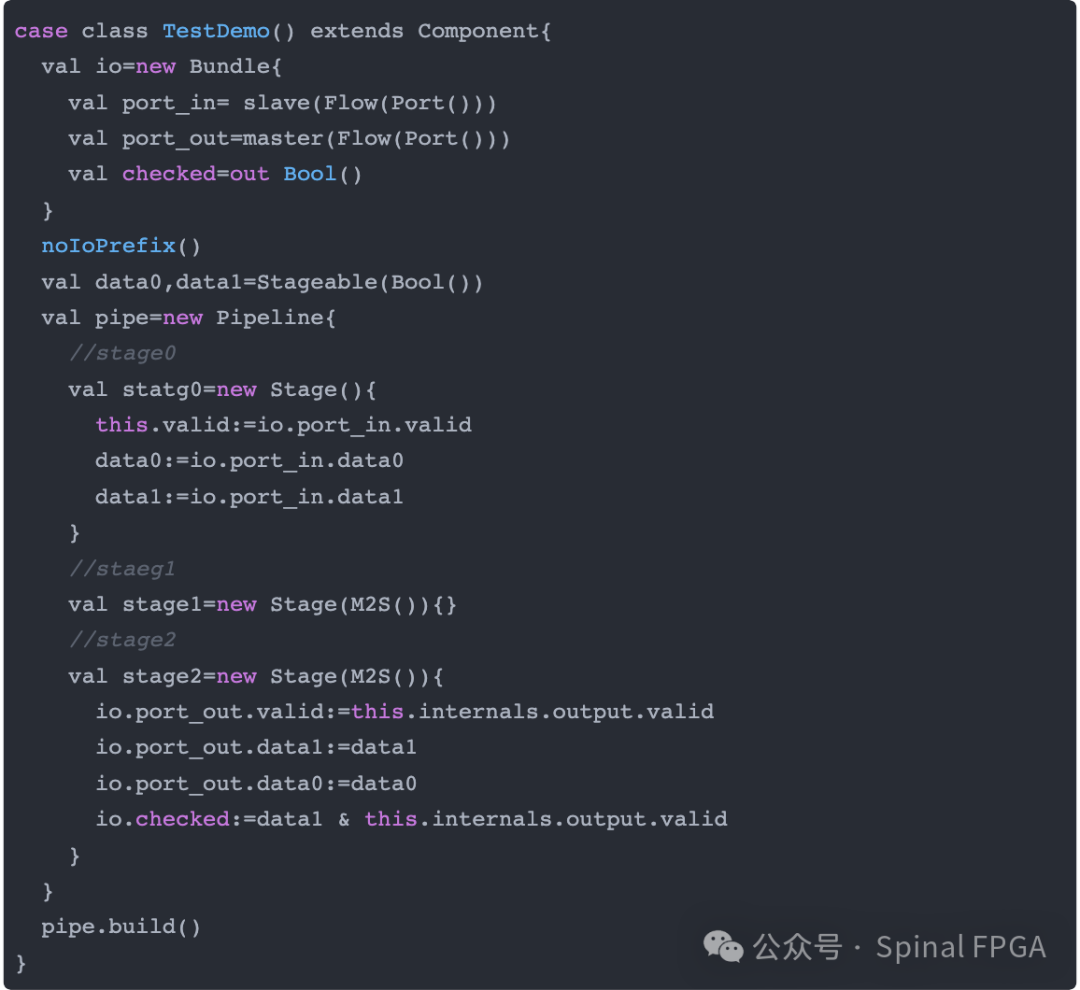

考慮下面的一個(gè)使用pipeline簡(jiǎn)單的邏輯代碼:

這是一個(gè)很簡(jiǎn)單的邏輯,port_in打兩拍輸出至port_out。邏輯里有這樣一個(gè)動(dòng)作需求:

當(dāng)port_out.valid為高且port_out.data1為true時(shí),checked為真

這里checked輸出為一個(gè)組合邏輯,如果外部在使用時(shí)還需要其他許多類(lèi)似的條件那么就有可能會(huì)對(duì)時(shí)序收斂帶來(lái)困難了(這里僅用來(lái)舉個(gè)例子闡述這種類(lèi)似的需求)。

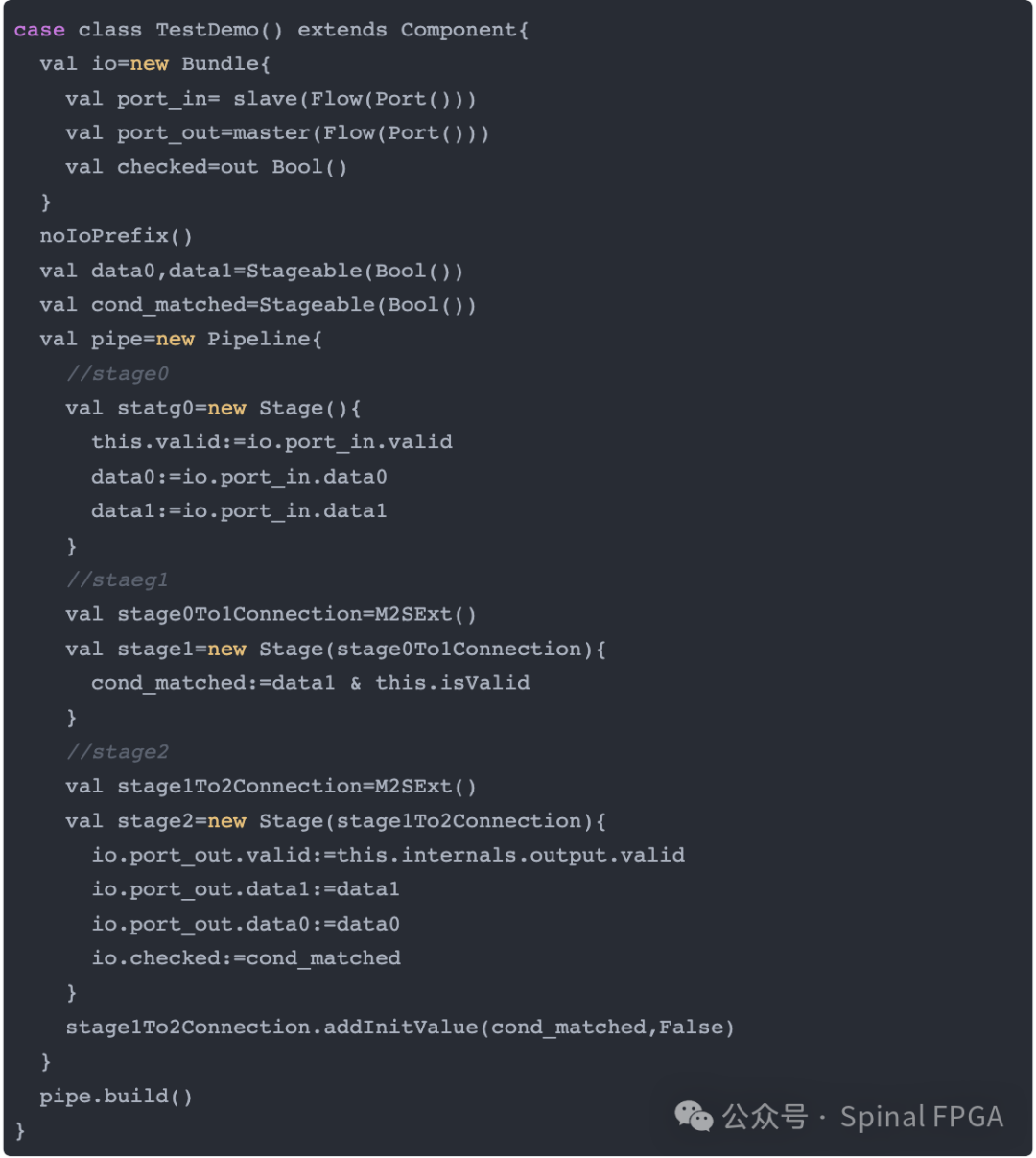

那么也許想當(dāng)然的將checked的判斷條件聲明一個(gè)Stageable變量在stage1中完成判斷,stage2中直接使用,就像這么來(lái)做:

如此,我們將組合邏輯前移,checked輸出為時(shí)序邏輯。看似完美是吧~

然而,如果你在VCS仿真器里仿真你會(huì)發(fā)現(xiàn),checked可能剛一上電就是高電平導(dǎo)致后續(xù)邏輯異常。其原因就是cond_matched沒(méi)有賦初值。

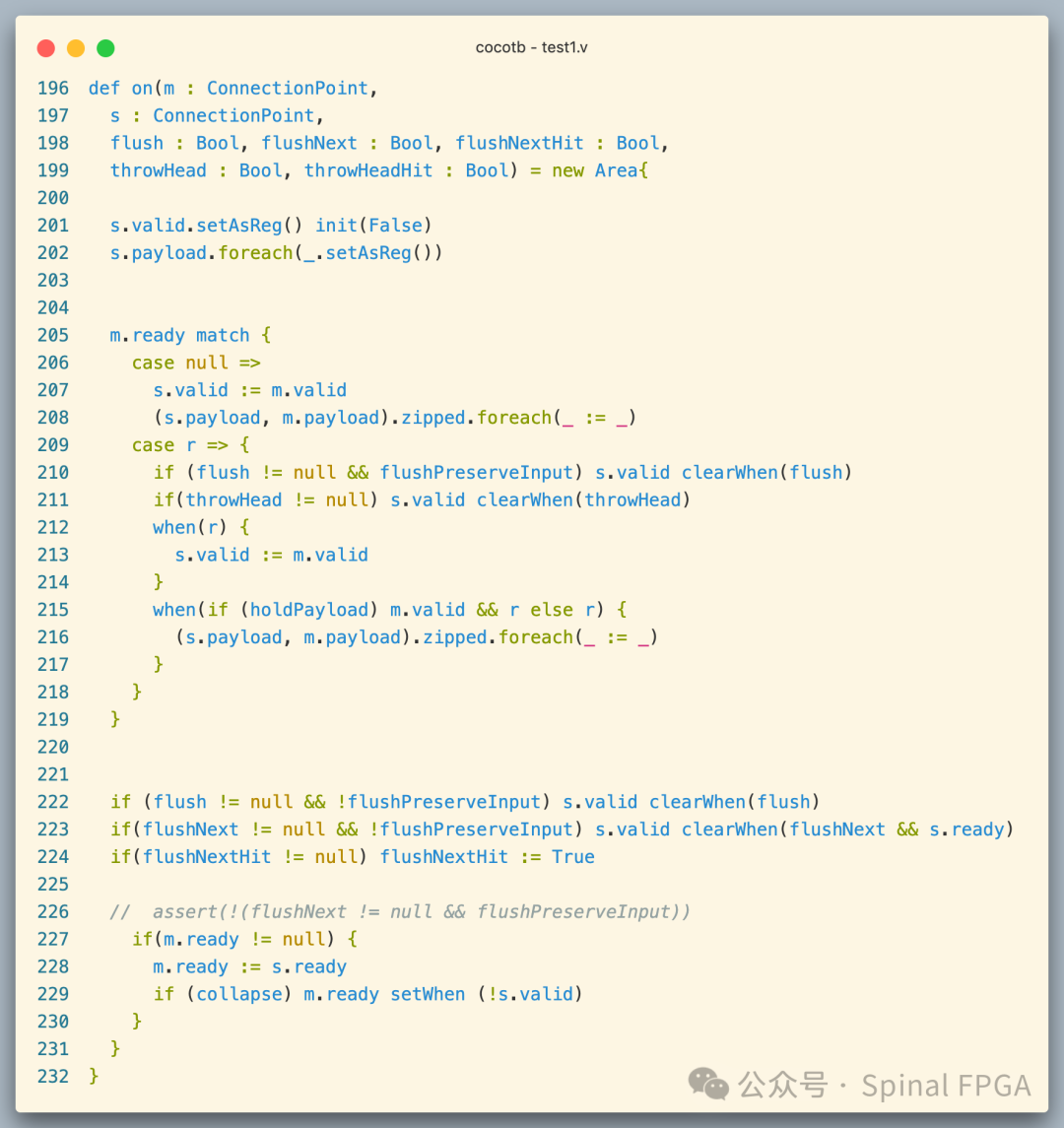

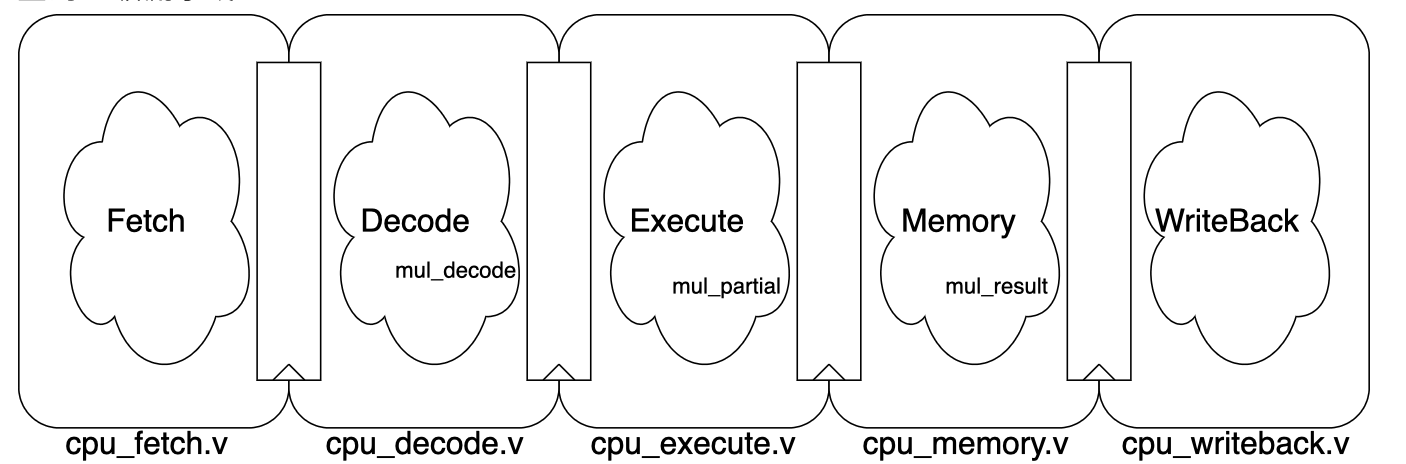

在pipeline的架構(gòu)里,在Connection中實(shí)現(xiàn)了不同Stage之間的連接,其中也包含了時(shí)序協(xié)議的實(shí)現(xiàn)。以這里我們調(diào)用的M2S為例:

其將valid聲明為Reg并賦給初始值False,然而對(duì)于payload僅聲明為寄存器并未賦初值。

由于有valid信號(hào)指示,paylaod不賦初值無(wú)可厚非,奔著控制路徑添加復(fù)位,數(shù)據(jù)路徑不添加復(fù)位的原則,這里并沒(méi)有問(wèn)題。然而我們?cè)卺槍?duì)一些時(shí)序優(yōu)化的場(chǎng)景需要將部分paylaod賦初值,這里就不太符合我們的需求了。

》M2SExt

既然滿足不了需求,那就擴(kuò)展。這里的實(shí)現(xiàn)可能略顯丑陋,但能解決問(wèn)題。Stageable類(lèi)型在Pipeline中例化為對(duì)象時(shí)會(huì)以我們聲明的Stageable變量名作為結(jié)尾,我們只需在M2S的on實(shí)現(xiàn)基礎(chǔ)上添加匹配規(guī)則即可。由于M2S是Class不可繼承,這里重新定義了一個(gè)M2SExt來(lái)實(shí)現(xiàn):

caseclassM2SExt(collapse: Boolean= true, holdPayload: Boolean= false, flushPreserveInput: Boolean= false) extendsConnectionLogic { val initMap = LinkedHashMap[String, Data]() def addInitValue[T <: Data](target: Stageable[T], initValue: T) = { ????initMap.update(target.getName(), initValue) ??} ??def on(m: ConnectionPoint, ?????????s: ConnectionPoint, ?????????flush: Bool, flushNext: Bool, flushNextHit: Bool, ?????????throwHead: Bool, throwHeadHit: Bool) = new?Area { ????s.valid.setAsReg() init (False) ????s.payload.foreach(_.setAsReg()) ????m.ready match { ??????case?null?=> s.valid := m.valid (s.payload, m.payload).zipped.foreach(_ := _) caser=>{ if(flush != null&& flushPreserveInput) s.valid clearWhen (flush) if(throwHead != null) s.valid clearWhen (throwHead) when(r) { s.valid := m.valid } when(if(holdPayload) m.valid && r elser) { (s.payload, m.payload).zipped.foreach(_ := _) } } } if(flush != null&& !flushPreserveInput) s.valid clearWhen (flush) if(flushNext != null&& !flushPreserveInput) s.valid clearWhen (flushNext && s.ready) if(flushNextHit != null) flushNextHit := True // assert(!(flushNext != null && flushPreserveInput)) if(m.ready != null) { m.ready := s.ready if(collapse) m.ready setWhen (!s.valid) } Component.current.addPrePopTask(()=>{ s.payload.foreach(paylaod=>{ initMap.foreach { case(signalEndName, initValue) =>{ if(paylaod.getName().endsWith(signalEndName)) { paylaod.init(initValue) } } } }) }) }

這里為M2S定義了一個(gè)addInitValue方法,從而能使得我們能夠?yàn)槟硞€(gè)ConnectionLogic中制定的Stageable映射電路對(duì)象添加復(fù)位值。在on實(shí)現(xiàn)函數(shù)最后通過(guò)添加PrePopTask來(lái)遍歷搜索當(dāng)前ConnectionLogic中對(duì)應(yīng)的payload并賦初始值。

最終我們可以在實(shí)現(xiàn)里如此:

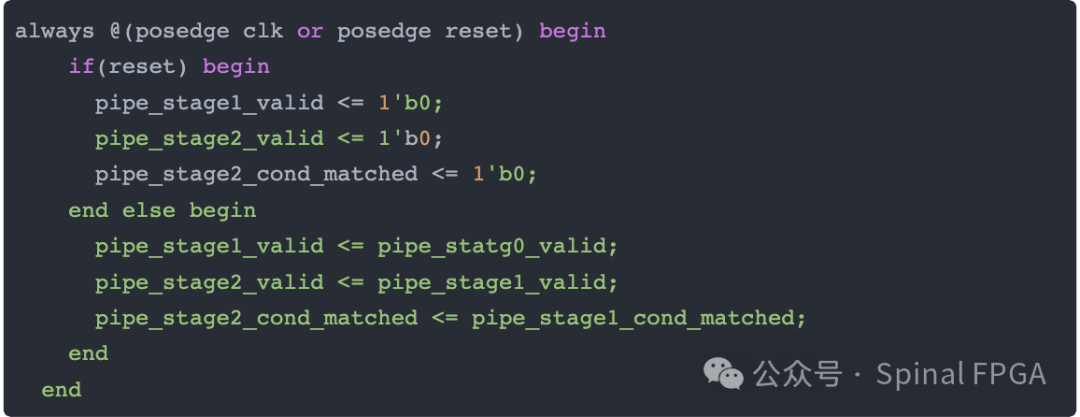

stage1To2Connection通過(guò)調(diào)用addInitValue來(lái)為cond_matched添加復(fù)位值,以此滿足需求:

pipe_stage2_cond_matched添加復(fù)位控制。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1630文章

21790瀏覽量

605089 -

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

120921 -

仿真器

+關(guān)注

關(guān)注

14文章

1019瀏覽量

83878 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9628 -

Pipeline

+關(guān)注

關(guān)注

0文章

28瀏覽量

9379

原文標(biāo)題:審視下Pipeline中的復(fù)位定制

文章出處:【微信號(hào):Spinal FPGA,微信公眾號(hào):Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在SpinalHDL中如何快速地實(shí)現(xiàn)總線連接

關(guān)于SpinalHDL中的驗(yàn)證覆蓋率收集簡(jiǎn)單說(shuō)明

談?wù)?b class='flag-5'>SpinalHDL中StreamCCByToggle組件設(shè)計(jì)不足的地方

聊聊SpinalHDL中的FIFO

在SpinalHDL中關(guān)于casez的使用

SpinalHDL中仿真信號(hào)的驅(qū)動(dòng)實(shí)現(xiàn)

定制板中的STMF446RE MCU復(fù)位問(wèn)題求解

SpinalHDL里時(shí)鐘域中的定制與命名

SpinalHDL中的SpiMasterCtrl模塊做使用說(shuō)明詳解

在SpinalHDL中的對(duì)應(yīng)關(guān)系及聲明形式

SpinalHDL中Bundle數(shù)據(jù)類(lèi)型的轉(zhuǎn)換

SpinalHDL BlackBox時(shí)鐘與復(fù)位

SpinalHDL里pipeline的設(shè)計(jì)思路

淺析SpinalHDL中Pipeline中的復(fù)位定制

淺析SpinalHDL中Pipeline中的復(fù)位定制

評(píng)論