前面一節(jié)我們學(xué)會了創(chuàng)建基于AXI總線的IP,但是對于AXI協(xié)議各信號的時序還不太了解。這個實驗就是通過SDK和Vivado聯(lián)合調(diào)試觀察AXI總線的信號。由于我們創(chuàng)建的接口是基于AXI_Lite協(xié)議的,所以我們實際觀察到是AXI_Lite協(xié)議的信號時序。

具體做法是創(chuàng)建一個基于AXI總線的加法器模塊,在Vivado里將AXI總線添加到debug信號里,實際上是用邏輯分析儀探測信號,在SDK端通過debug方式依次寫入兩個加數(shù),由PL計算出和,我們讀出這個和打印到串口,這樣AXI總線的讀和寫就都能觀察到了。

板子使用的是zc702。

在觀察信號之前我們有必要簡單了解AXI是個什么:

AXI總線是一種高性能、高帶寬、低延遲的片內(nèi)總線,AXI協(xié)議描述了主從設(shè)備數(shù)據(jù)傳輸?shù)姆绞健V髟O(shè)備和從設(shè)備通過握手信號建立連接,握手信號包括主機發(fā)送的VALID信號,表示數(shù)據(jù)有效,從機發(fā)送的READY信號,表示從機準(zhǔn)備好了接收數(shù)據(jù)。當(dāng)VALID和READY都有效的時候傳輸開始。

Zynq使用的是AXI協(xié)議的4.0版本,由AMBA3.0協(xié)議發(fā)展而來:

AXI的三種總線各有各的用途:

AXI4支持突發(fā)數(shù)據(jù)傳輸,主要用于CPU訪問存儲等需要高速數(shù)據(jù)交互的場合,相當(dāng)于原來的AHB協(xié)議;

AXI_Lite一次傳輸單個數(shù)據(jù),主要用于訪問一些低速外設(shè),相當(dāng)于原來的APB;

AXI_Stream數(shù)據(jù)傳輸不需要地址,主設(shè)備直接連續(xù)讀寫數(shù)據(jù),主要用于高速流數(shù)據(jù)的傳輸,使用起來類似FIFO。

AXI4總線和AXI4-Lite總線具有相同的組成部分:

(1) 讀地址通道, 包含ARVALID, ARADDR, ARREADY信號;

(2) 讀數(shù)據(jù)通道, 包含RVALID, RDATA, RREADY, RRESP信號;

(3) 寫地址通道, 包含AWVALID, AWADDR, AWREADY信號;

(4) 寫數(shù)據(jù)通道, 包含WVALID, WDATA, WSTRB, WREADY信號;

(5) 寫應(yīng)答通道, 包含BVALID, BRESP, BREADY信號;

(6) 系統(tǒng)通道, 包含: ACLK, ARESETN信號。

幫助記憶:

讀地址信號都是以AR開頭(A: address; R: read)

寫地址信號都是以AW開頭(A: address; W: write)

讀數(shù)據(jù)信號都是以R開頭(R: read)

寫數(shù)據(jù)信號都是以W開頭(W: write)

應(yīng)答信號都是以B開頭(B: back(answer back))

讀時序:

寫時序:

5個通道都有自己獨立的握手機制,同時又相互協(xié)作,地址線分離后,讀/寫可以并行交互數(shù)據(jù)。而且AXI支持地址pipeline、錯位傳輸?shù)饶J剑蟠筇岣吡藬?shù)據(jù)通路的利用率。

關(guān)于AXI Interconnect模塊:

AXI協(xié)議可以描述為主/從設(shè)備之間的點對點傳輸,可以有多個主機,也可以有多個從機,這是進行數(shù)據(jù)交互時,需要一個管理中心確保信號發(fā)到對應(yīng)的設(shè)備,AXI Interconnect模塊就是這樣一個管理中心,也叫做AXI互聯(lián)矩陣。它類似于一個交換機,保證每個外設(shè)獨享帶寬,完成數(shù)據(jù)傳輸。Xilinx公司為我們提供了AXI Interconnect的IP核。

介紹到此,理論部分已經(jīng)掌握i一二了,下面就開始實際觀察AXI的信號。

創(chuàng)建一個基于AXI_Lite總線的加法器IP

新建Vivado工程,依然,選擇這個:

修改名字和地址,我命名為AXI_Add,地址最好選擇工程路徑下新建一個文件夾,這樣就會自動把你創(chuàng)建的IP更新到IP庫里,其他默認(rèn),最后選擇Edit IP,在Vivado給出的代碼里添加上我們的加法器功能:

注意這些代碼就是定義AXI協(xié)議的工作方式的,里面有注釋,可以去研究一下!

添加用戶端口:

這里我們沒有要輸出的信號

封裝好后回到我們之前建的工程,

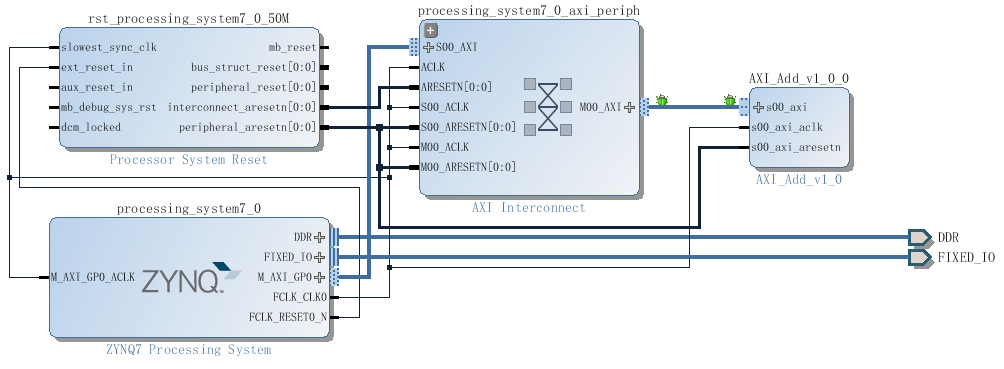

然后在工程里添加zynq核,添加剛才創(chuàng)建的IP,點擊自動連接,然后選中AXI總線,右擊選擇Make Debug,出現(xiàn)兩個綠色的小瓢蟲,將總線加入Debug模式下。

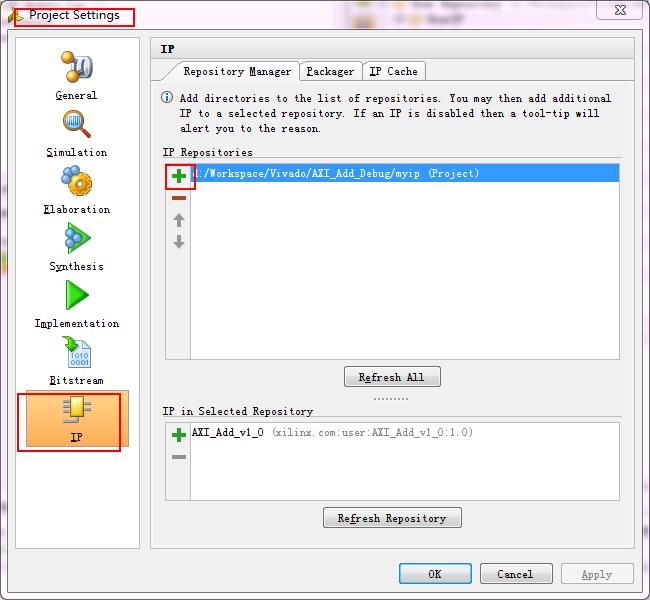

如果你沒有把剛才新建的IP放在該工程目錄下,先要把IP添加進庫里,選擇 Project Settings-->IP。點擊綠色的加號,選擇到你的用戶IP地址 :

整個系統(tǒng)搭建完成是這樣的:

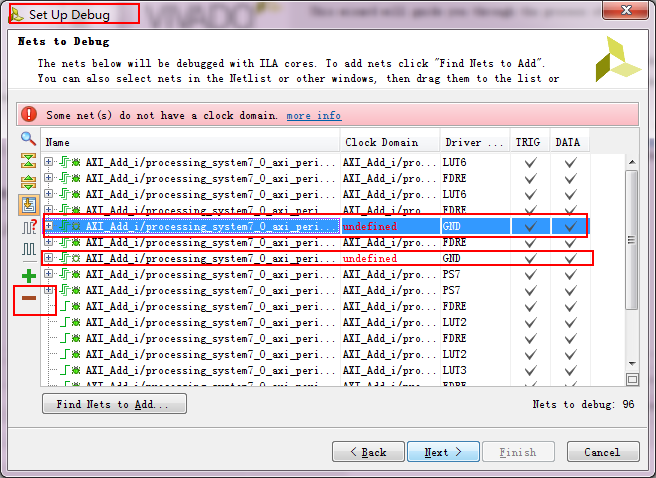

下面就是例行操作,自動排版,檢查,保存,復(fù)位,generate,產(chǎn)生頂層文件。然后先綜合(Synthesis)一下,綜合好后,打開Synthesis Design下的Set Up Debug,將顯示為紅色的無用信號刪除(選中,點擊紅色的減號),

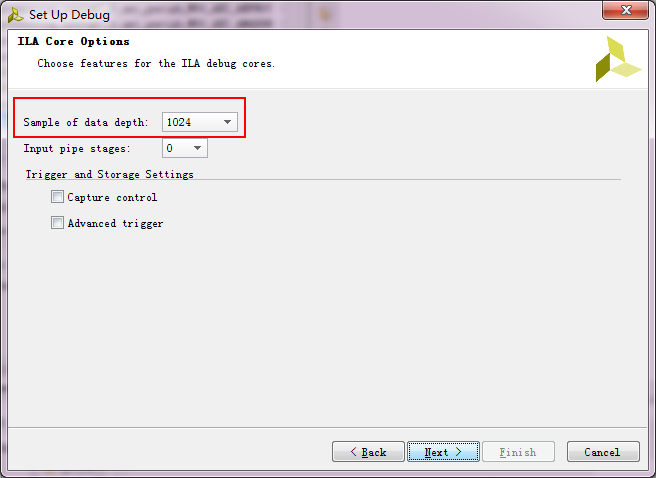

設(shè)置采樣深度為1024,

其他默認(rèn),然后生成比特流文件。

軟件端的設(shè)計

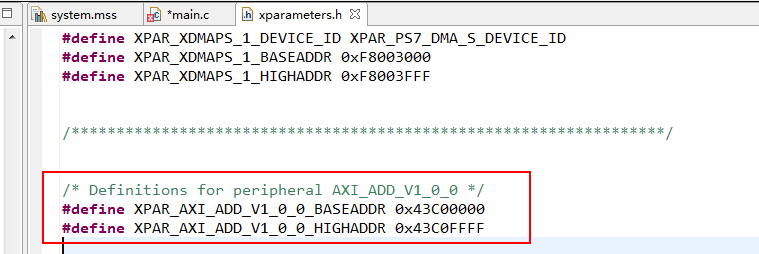

Lanch到SDK,新建一個空的applicaton工程,添加一個c源文件,我們在xparameters.h文件中找到我們添加的加法器AXI_ADD的寄存器首地址,待會我們就是要通過地址對寄存器進行讀、寫:

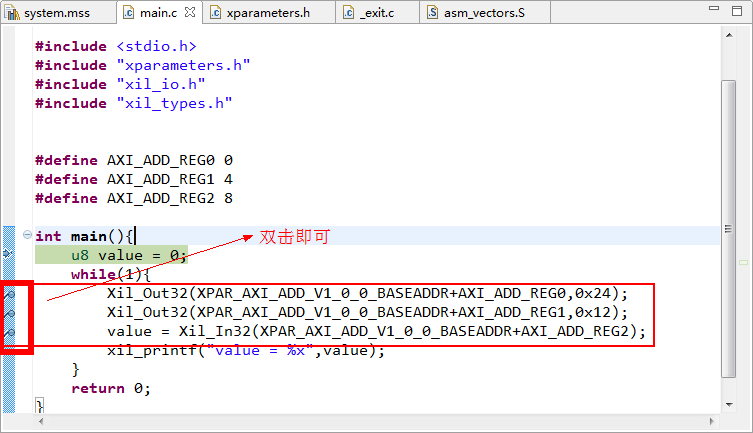

這個案例里我們計算16進制下的24+12=36,為了方便SDK端的斷點調(diào)試,加了while循環(huán),注釋我寫在后面了:

#include

#include "xparameters.h"

#include "xil_io.h"

#include "xil_types.h"

#define AXI_ADD_REG0 0 //寄存器0的偏移地址為0

#define AXI_ADD_REG1 4 //寄存器1的偏移地址為4

#define AXI_ADD_REG2 8 //寄存器2的偏移地址為8

int main(){

while(1){

u8 value = 0;

Xil_Out32(XPAR_AXI_ADD_V1_0_0_BASEADDR+AXI_ADD_REG0,0x24); //向寄存器0寫入第一個加數(shù)

Xil_Out32(XPAR_AXI_ADD_V1_0_0_BASEADDR+AXI_ADD_REG1,0x12); //向寄存器1寫入第二個加數(shù)

value = Xil_In32(XPAR_AXI_ADD_V1_0_0_BASEADDR+AXI_ADD_REG2); //從寄存器3中讀出和

xil_printf("value = %x",value);

}

return 0;

}

軟硬件聯(lián)合調(diào)試

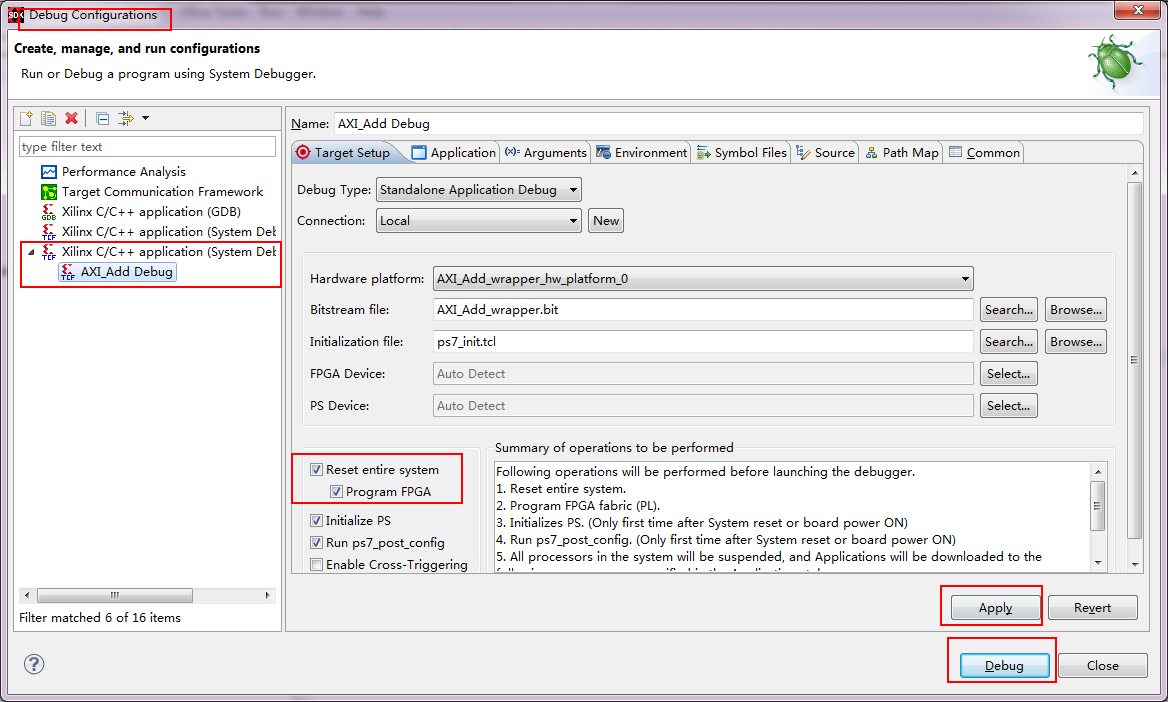

右鍵工程 Debug as-->Debug Configrations:

進入Debug界面后,在AXI總線讀、寫的地方添加斷點:

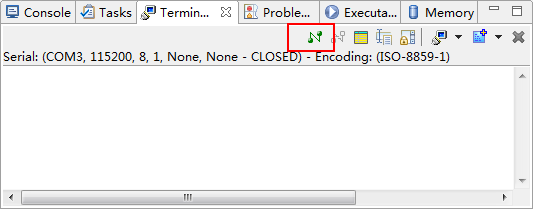

打開串口:

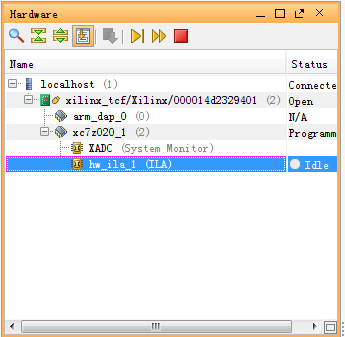

然后回到Vivado界面,連接到Device,就會自動打開調(diào)試界面:

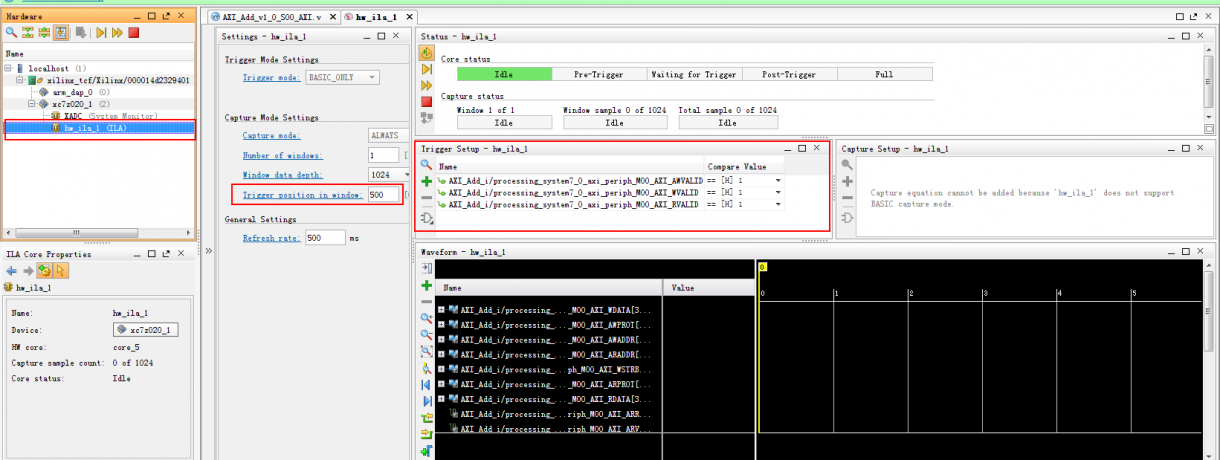

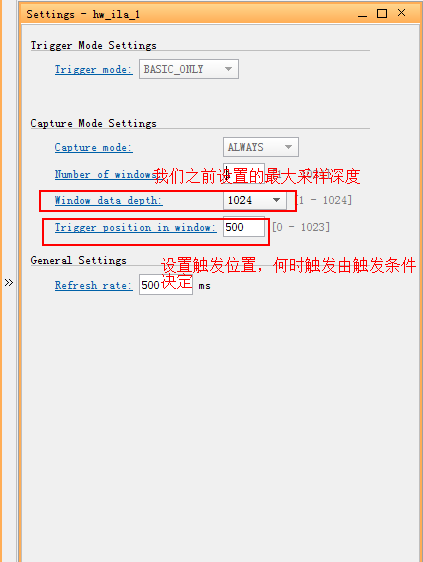

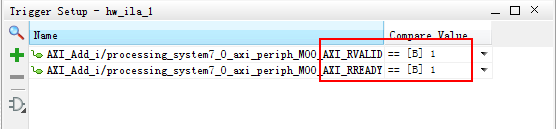

接下來是設(shè)置觸發(fā)位置,添加觸發(fā)條件:

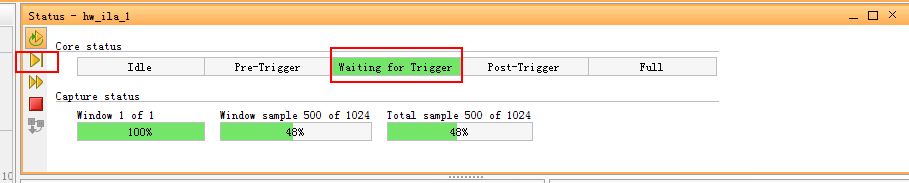

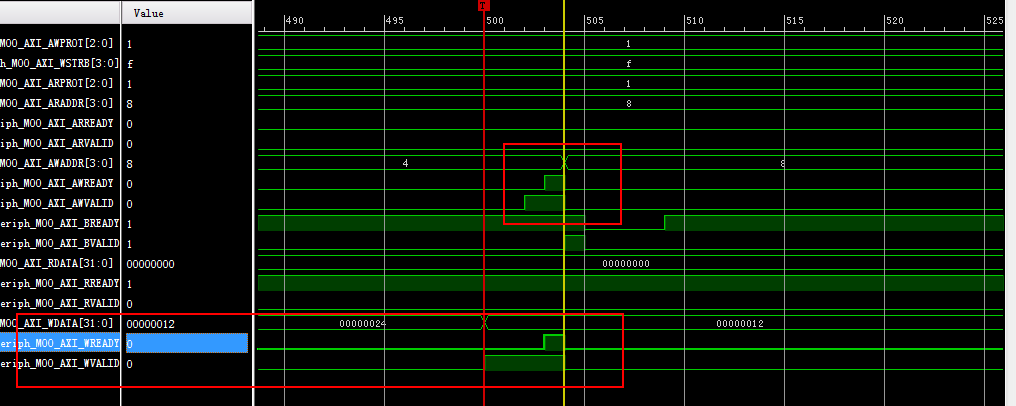

我們的采樣深度是默認(rèn)的1024,在500的位置觸發(fā),

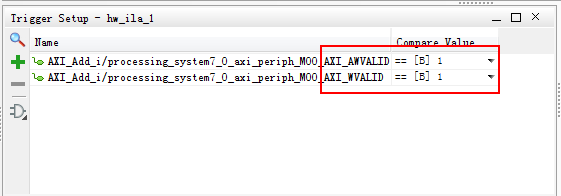

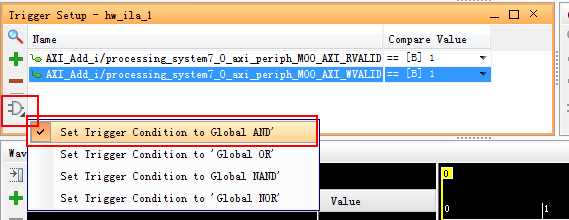

觸發(fā)條件設(shè)置成WVALID信號為高時,AWVALID信號為高時:

右鍵邏輯分析儀,選中Enable Auto Re-trigger,設(shè)置成自動進入下一次觸發(fā):

點擊運行觸發(fā),點擊完之后ila進入等待觸發(fā)狀態(tài):

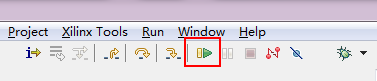

在SDK點擊運行:

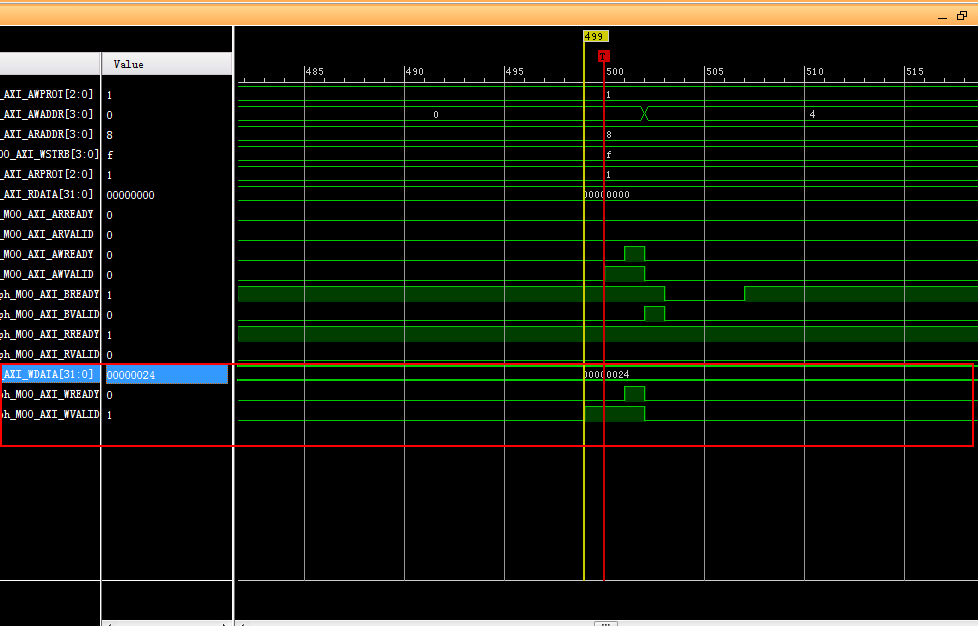

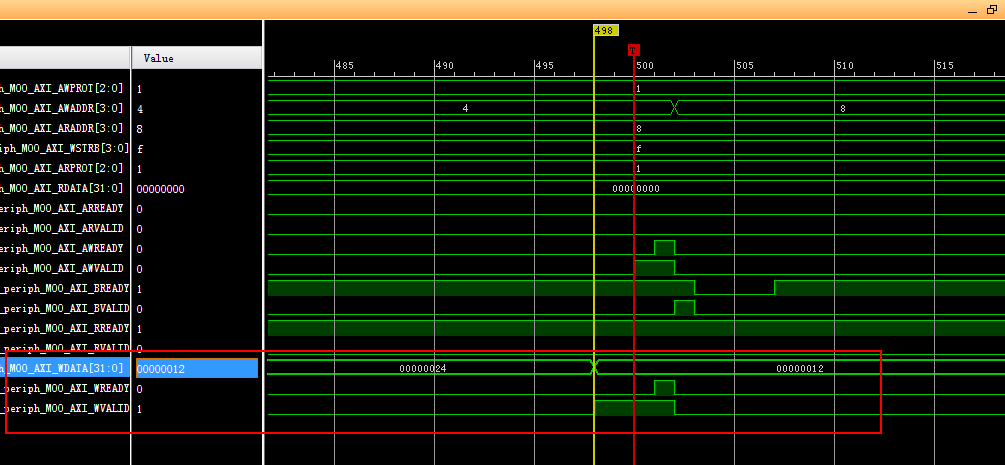

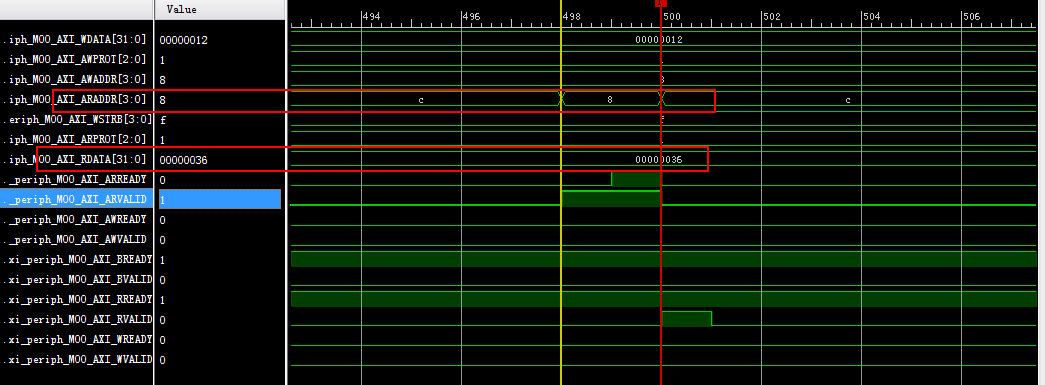

首先寫入24:

有一點要注意,這里的寫地址VALID和READY信號是下一個地址的,這里就是對應(yīng)WDATA的4,而對應(yīng)地址0,也就是我們觀察的數(shù)據(jù)24地址的VALID和READY信號在前面已經(jīng)有效過了,我們設(shè)置寫數(shù)據(jù)有效時觸發(fā),而地址有效在前面就沒有捕捉到了。

然后寫入12:

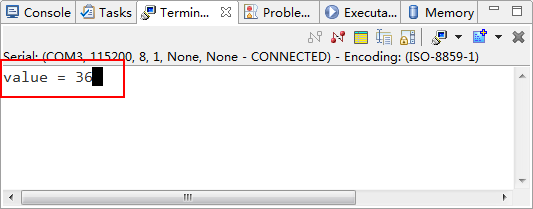

然后串口打印出36:

等到第二輪寫入的時候,我們看到讀數(shù)據(jù)通道上出現(xiàn)36:

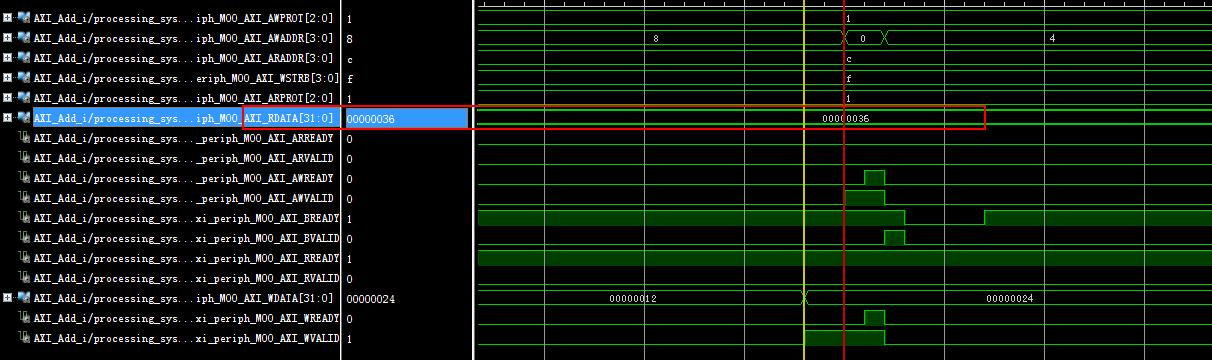

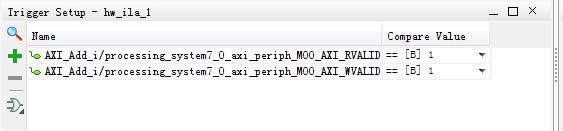

我們可以換一下觸發(fā)信號,換成讀VALID,讀READY拉高時觸發(fā):

就可以看到,讀VALID和READY信號都高時,讀出36,讀地址線上是8:

這里可以看到讀READY信號一直為高,讀VALID信號拉高時36讀入。但是由于ILA捕捉的是觸發(fā)時刻信號,所以它將讀有效之前的讀數(shù)據(jù)都顯示為36了。

大家要注意,觸發(fā)設(shè)置里,添加的信號默認(rèn)是AND的,如果你一開始就把讀有效為高,寫有效為高都添加到觸發(fā)列表里,會觀察不到信號,因為這兩個信號在本例子;里不會同時出現(xiàn):

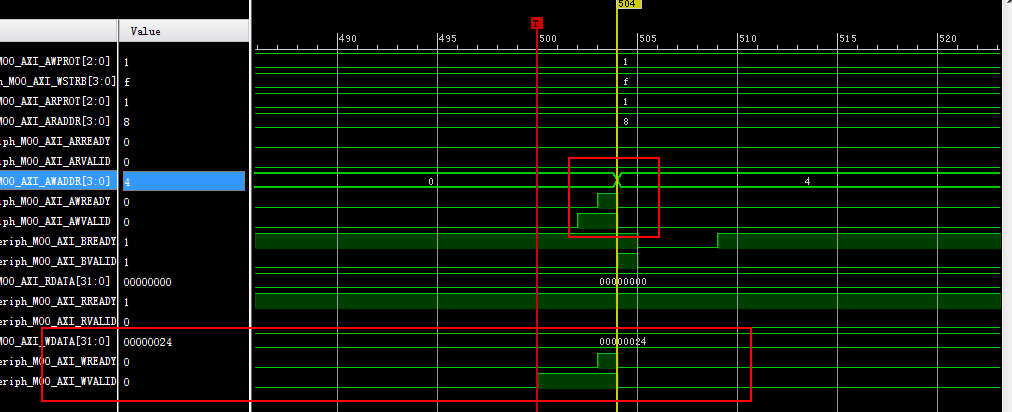

SDK那邊一步步Debug,先是寫入24:

然后寫入12:

然后讀到36:

這里也是由于RREADY先于RVALID信號拉高,ILA捕捉不到READY是什么高的,就把之前都顯示為高。

如果沒有按你設(shè)置的運行,可以在SDK重新Debug as或者在Vivado重新連接一下Target,或者多點幾次Run Trigger,這軟件有時候不靈敏,比如說你雖然設(shè)置了自動進入下一次觸發(fā),但是它不一定就進入,這是手動點一下觸發(fā),進入等待模式,再點擊下一次Debug。

小結(jié)

到這里,AXI信號讀寫時序就全部觀察完了,這時候可以再去看一看AXI協(xié)議的理論部分,把封裝基于AX總線的IP時生成的例化代碼捋一遍,就能更好的理解AXI總線的工作原理了。提一句,我們目前觀察的都是簡化版的AXI_Lite協(xié)議的時序。

編輯:hfy

-

加法器

+關(guān)注

關(guān)注

6文章

183瀏覽量

30155 -

AXI

+關(guān)注

關(guān)注

1文章

128瀏覽量

16647 -

Vivado

+關(guān)注

關(guān)注

19文章

813瀏覽量

66648

發(fā)布評論請先 登錄

相關(guān)推薦

加法器

加法器,加法器是什么意思

十進制加法器,十進制加法器工作原理是什么?

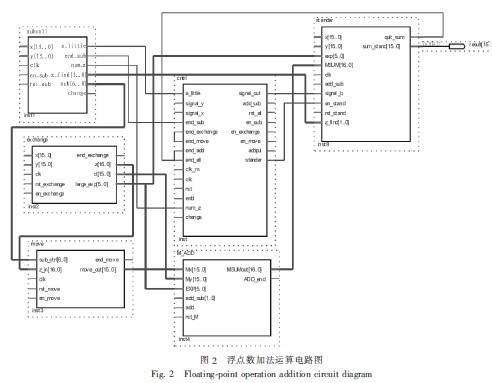

FPU加法器的設(shè)計與實現(xiàn)

同相加法器電路原理與同相加法器計算

基于AXI總線的加法器模塊解決方案

基于AXI總線的加法器模塊解決方案

評論