由于篇幅有限,本文僅選取部分內容進行分享。

Vitis 簡介

AMD Vitis 工具套件包含多種設計技術,用于開發以 AMD 器件(例如,AMD Versal 自適應 SoC 器件、AMD Zynq MPSoC 和 AMD Alveo 數據中心加速器卡)為目標的異構嵌入式應用。

Vitis 工具包括:

C++ 編譯器、庫和本征函數,適用于 AI 引擎和可編程邏輯( PL )

適用于 Arm 和 MicroBlaze CPU 的傳統工具鏈和庫

圖形化集成設計環境( IDE )

系統連接器,用于配置復雜的器件子系統,如 AI 引擎、NoC 和 Control & Integrated Processing system( CIPS ),并將其與高性能多速率系統中的 PL 模塊與內核相集成

調試器和硬件/軟件檢測自動化,有助于定位和解決嵌入式系統中的性能瓶頸和問題

跨 PL( HDL )、AI 引擎( System-C ) 和 CPU( QEMU )無縫編譯、鏈接和運行異構仿真

程序分析器,用于剖析和可視化仿真中和目標上的硬件/軟件性能

Xilinx Runtime( XRT )提供 Linux 用戶空間 API,用于運行時鏡像加載、存儲器管理與內核控制

開發平臺,提供開箱即用的沙箱,用于 AI 引擎 開發、PL+AI 引擎子系統開發以及嵌入式系統應用引導

硬件優化的庫,用于 DSP、視覺和圖像處理、線性代數和諸多其他應用域

Vitis 工具套件是基于 AMD Vivado Design Suite 構建的,支持硬件和軟件的 C/C++ 編程、靈活且可縮放的系統連接規格用于促進自上而下、中間向外和自下而上的設計迭代、RTL 模塊集成、清晰的底層 Vivado 硬件工具流程自動化和交接。

Vitis 關鍵概念

本主題介紹的關鍵概念有助于您了解和使用 AMD Vitis 工具來開展嵌入式系統設計。這些工具支持通過以下方式完成各種開發流程:使用腳本編制執行開發或者通過 Vitis IDE 進行交互式設計輸入來執行開發。所有開發流程均以相同結果為目標,但設計師的技能等級和工程要求可能會影響特定流程類型的傾向性。下表描述了這些步驟。

表 1:概念性設計步驟

| 步驟 | 注釋 |

| 選擇器件 | 聲明為部件或開發板 |

|

設置基本的硬件 基礎架構 |

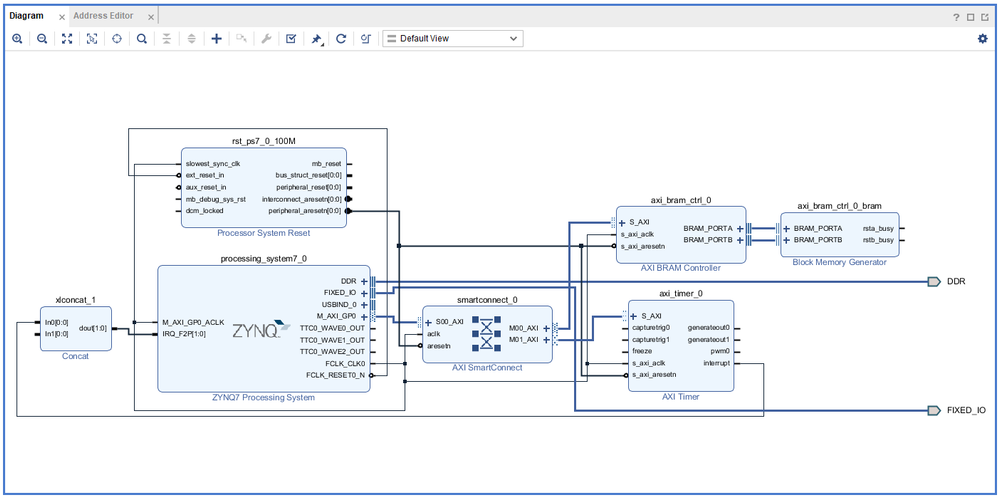

這即所謂通過 AMD Vivado 創建的硬件平臺。有效的硬件平臺由 Vivado IP integrator 組件(例如,CIPS、NoC )和至少一個時鐘(含關聯復位)組成。(可選)除了時鐘域、復位和定制 RTL IP 外,還可添加 AI 引擎、NoC DDRMC、AXI SmartConnect 和 AXI Interrupt Controller。在塊設計內的單元和端口上將包含 PFM 屬性,這些單元和端口用于為內核控制定義潛在的連接點、訪問 DDR 和其他存儲器、串流輸入/輸出、時鐘、復位及中斷。此初始設計會作為可擴展硬件平臺導出到 Vitis。 |

| 添加處理元件 |

這即所謂的 Vitis 組件,包括 PL 內核與 AI 引擎計算圖。 注釋:這些組件先獨立完成開發和驗證,然后再添加。組件開發不在本文檔的探討范圍內。 |

| 實現硬件 | 在 Vitis 術語中,這是指編譯和鏈接硬件系統的進程。Vitis 實現步驟會利用 Vivado 來進行 PL 綜合與布局布線。 |

| 添加軟件應用 | 在處理器(如,APU、RPU 和 MicroBlaze )上運行的控制應用和/或處理應用。 |

| 封裝軟件和硬件 | 將可加載的對象與可執行應用組合為二進制可交付物(如,SD 卡、QSPI 閃存等)的進程。 |

|

在目標上部署 并運行 |

此步驟包括加載二進制可交付物并在硬件上運行或者在硬件仿真中運行。Vitis 實現步驟會利用 Vivado 來進行 PL 綜合與布局布線。 |

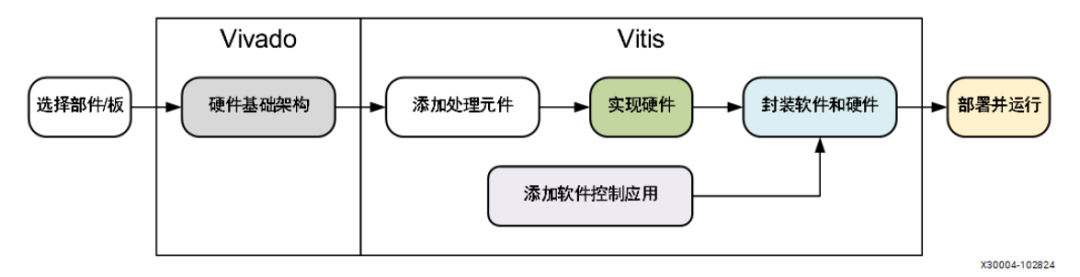

下圖演示了設計嵌入式系統并將其與 AMD 工具集成的概念性流程。

圖 1:Vitis 概念性設計流程

Vitis 工具支持多種不同的設計流程,如第 3 章:Vitis 流程和構建環境所述。以下章節著重講解了用于創建和集成這些不同組件的各種工具和技巧。

-

amd

+關注

關注

25文章

5475瀏覽量

134282 -

嵌入式設計

+關注

關注

0文章

392瀏覽量

21301 -

Vitis

+關注

關注

0文章

147瀏覽量

7456

原文標題:使用 Vitis 進行嵌入式設計開發用戶指南(附下載)

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Vitis里如何創建嵌入式軟件工程

Vitis2023.2使用之—— classic Vitis IDE

Compact系列CPLD嵌入式Flash(EFlash)用戶指南

使用AMD Vitis進行嵌入式設計開發用戶指南

使用AMD Vitis進行嵌入式設計開發用戶指南

評論