完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > fpga設(shè)計(jì)

FPGA(Field-Programmable Gate Array),即現(xiàn)場(chǎng)可編程門(mén)陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。

文章:348個(gè) 瀏覽:26570次 帖子:90個(gè)

使用Xilinx口袋實(shí)驗(yàn)平臺(tái),動(dòng)手FPGA設(shè)計(jì)!

以Xilinx公司最新的Vivado FPGA集成開(kāi)發(fā)環(huán)境為基礎(chǔ),將數(shù)字邏輯設(shè)計(jì)與硬件描述語(yǔ)言Verilog HDL相結(jié)合,循序漸進(jìn)地介紹了基于Xili...

2017-12-27 標(biāo)簽:fpgaFPGA設(shè)計(jì)xilinx 1.5萬(wàn) 0

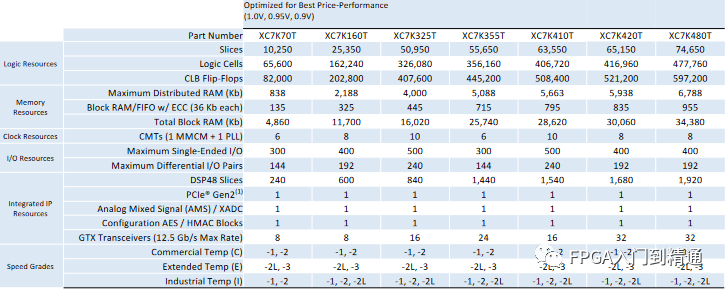

FPGA的用處比我們平時(shí)想象的用處更廣泛,原因在于其中集成的模塊種類(lèi)更多,而不僅僅是原來(lái)的簡(jiǎn)單邏輯單元(LE)。 早期的FPGA相對(duì)比較簡(jiǎn)單,所有的功能...

2018-09-07 標(biāo)簽:fpgaFPGA設(shè)計(jì) 1.3萬(wàn) 0

FPGA設(shè)計(jì)思想,速度和面積互換原則不可忽視

流水線設(shè)計(jì)可以從某種程度上提高系統(tǒng)頻率。。前提是:設(shè)計(jì)可以分為若干步驟進(jìn)行處理,而且整個(gè)數(shù)據(jù)處理的過(guò)程是單向的,即沒(méi)有反饋或者逆運(yùn)算、前一個(gè)步驟的輸出是...

2017-12-18 標(biāo)簽:fpgaFPGA設(shè)計(jì)可編程邏輯 1.1萬(wàn) 0

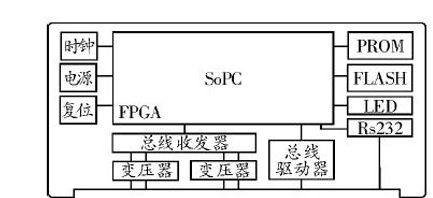

探討基于sopc技術(shù)的fpga集成嵌入式系統(tǒng)設(shè)計(jì)

可編程片上系統(tǒng)( SoPC)是在可編程邏輯器件的基礎(chǔ)上發(fā)展起來(lái)的一種靈活、高效的嵌入式系統(tǒng)設(shè)計(jì)解決方案,系統(tǒng)設(shè)計(jì)者可以從傳統(tǒng)的板級(jí)系統(tǒng)設(shè)計(jì)轉(zhuǎn)換到芯片級(jí)系...

2017-12-02 標(biāo)簽:FPGA設(shè)計(jì)SOPC技術(shù) 7697 0

之前的文章介紹了FPGA在線調(diào)試的方法,包括選定抓取信號(hào),防止信號(hào)被優(yōu)化的方法等等。

2023-06-20 標(biāo)簽:FPGA設(shè)計(jì)DDS觸發(fā)器 7284 0

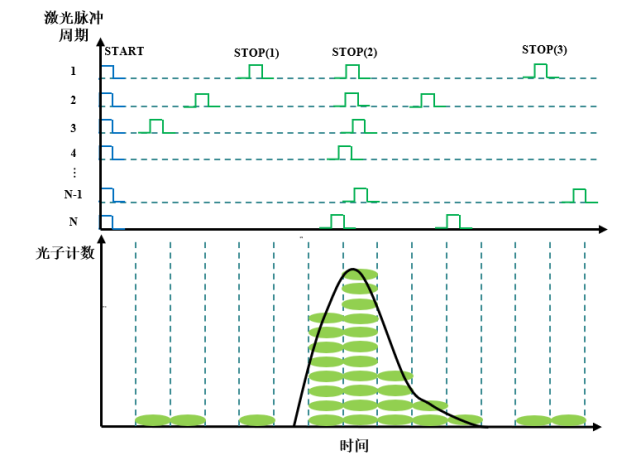

基于單光子探測(cè)的時(shí)間相關(guān)計(jì)數(shù)TCSPC設(shè)計(jì)實(shí)現(xiàn)

TCSPC時(shí)間相關(guān)單光子計(jì)數(shù)技術(shù)是一種成熟且通用的單光子計(jì)數(shù)技術(shù),是一種功能強(qiáng)大的分析方法,目前廣泛應(yīng)用于熒光壽命測(cè)量、時(shí)間分辨光譜、熒光壽命成像、飛行...

2023-09-22 標(biāo)簽:FPGA設(shè)計(jì)存儲(chǔ)器數(shù)字轉(zhuǎn)換器 6962 3

作者:張澤小腳丫STEP 導(dǎo)讀:FPGA(Field Programmable Gate Array)譯作中文為:現(xiàn)場(chǎng)可編程門(mén)陣列,也就是設(shè)計(jì)者可以在現(xiàn)...

2018-06-14 標(biāo)簽:fpgaFPGA設(shè)計(jì)Altera 6944 0

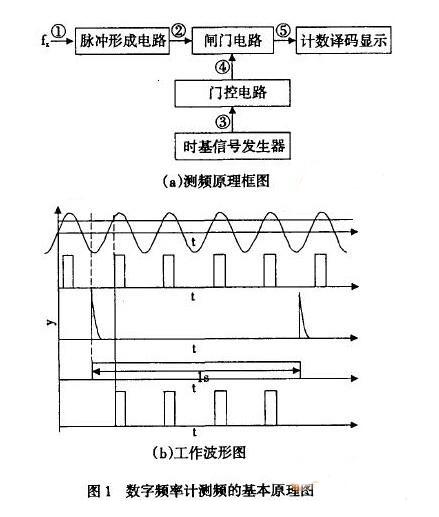

基于FPGA自適應(yīng)數(shù)字頻率計(jì)的設(shè)計(jì)

在電子工程,資源勘探,儀器儀表等相關(guān)應(yīng)用中,頻率計(jì)是工程技術(shù)人員必不可少的測(cè)量工具。頻率測(cè)量也是電子測(cè)量技術(shù)中最基本最常見(jiàn)的測(cè)量之一。不少物理量的測(cè)量,...

2019-01-01 標(biāo)簽:FPGA設(shè)計(jì) 6749 0

ChipScope是Xilinx提供的一個(gè)校驗(yàn)FPGA設(shè)計(jì)的工具。它的本質(zhì)是一個(gè)虛擬的邏輯分析儀,能調(diào)用FPGA內(nèi)部的邏輯資源對(duì)代碼中的各個(gè)變量進(jìn)行抓取分析。

2023-05-08 標(biāo)簽:FPGA設(shè)計(jì)led燈ROM 6613 0

1、硬件設(shè)計(jì)基本原則 (1)速度與面積平衡和互換原則:一個(gè)設(shè)計(jì)如果時(shí)序余量較大,所能跑的頻率遠(yuǎn)高于設(shè)計(jì)要求,能可以通過(guò)模塊復(fù)用來(lái)減少整個(gè)設(shè)計(jì)消耗的...

2017-12-19 標(biāo)簽:fpgaFPGA設(shè)計(jì) 6465 0

使用SoM來(lái)開(kāi)發(fā)嵌入式系統(tǒng)的優(yōu)勢(shì)

作者:Steve Leibson 很多嵌入式設(shè)計(jì)使用基于微處理器和微控制器的單板計(jì)算機(jī) (SBC) 和系統(tǒng)級(jí)模塊 (SoM)(例如,請(qǐng)參閱使用 Rasp...

2018-08-31 標(biāo)簽:嵌入式FPGA設(shè)計(jì)soc 5888 0

FPGA設(shè)計(jì)中BRAM的知識(shí)科普

FPGA設(shè)計(jì)中,BRAM是一項(xiàng)非常關(guān)鍵的內(nèi)置存儲(chǔ)資源,F(xiàn)PGA開(kāi)發(fā)需要熟練使用BRAM,今天再?gòu)?fù)習(xí)一下BRAM的知識(shí),包括BRAM的定義、組成、應(yīng)用等等。

2023-08-15 標(biāo)簽:fpgaDRAMFPGA設(shè)計(jì) 5743 0

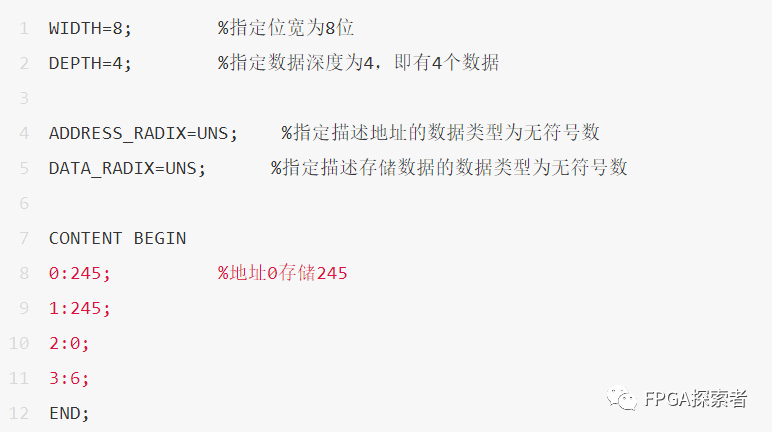

FPGA仿真必備—Matlab生成.mif/.txt/.coe文件

.mif 和 .coe 是 FPGA 設(shè)計(jì)中常用的存儲(chǔ)文件,用于 ROM、RAM 等存儲(chǔ)器數(shù)據(jù)的加載,常見(jiàn)的還用在 DDS 信號(hào)發(fā)生器和 FIR 濾波器...

2023-06-21 標(biāo)簽:FPGA設(shè)計(jì)存儲(chǔ)器DDS 5657 0

什么是ECO?ECO的應(yīng)用場(chǎng)景和實(shí)現(xiàn)流程

ECO指的是 Engineering Change Order ,即工程變更指令。目的是為了在設(shè)計(jì)的后期,快速靈活地做小范圍修改,從而盡可能的保持已經(jīng)驗(yàn)...

2023-04-23 標(biāo)簽:dspFPGA設(shè)計(jì)IC設(shè)計(jì) 5479 0

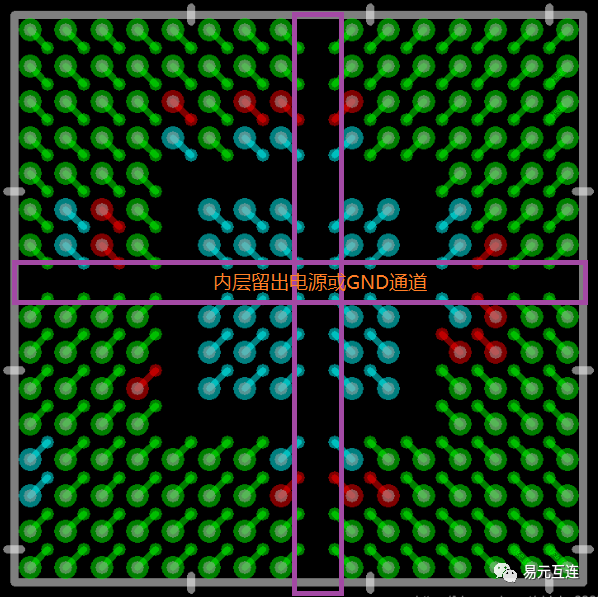

BGA扇出是EDA工程師的一項(xiàng)基本功,在布局完成后,先將BGA的Ball進(jìn)行打孔扇出,然后分層和4個(gè)方向?qū)GA內(nèi)部信號(hào)線引出到外部空間

2023-09-22 標(biāo)簽:PCB板FPGA設(shè)計(jì)BGA封裝 5352 0

在FPGA設(shè)計(jì)中可以用LUT組建分布式的RAM

舉一個(gè)簡(jiǎn)單的例子,如果要實(shí)現(xiàn)一個(gè)6*1的mux可以用一個(gè)6輸入的LUT或者是2個(gè)4輸入的LUT來(lái)實(shí)現(xiàn),6輸入的LUT相當(dāng)于是6位地址線一位數(shù)據(jù)位,能夠存...

2022-05-13 標(biāo)簽:FPGA設(shè)計(jì)RAM分布式 5236 0

本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。在FPGA和ASIC設(shè)計(jì)中,對(duì)于復(fù)位這個(gè)問(wèn)題可以算是老生常談了,但是也是最容易...

2023-05-12 標(biāo)簽:fpgaFPGA設(shè)計(jì)觸發(fā)器 4978 0

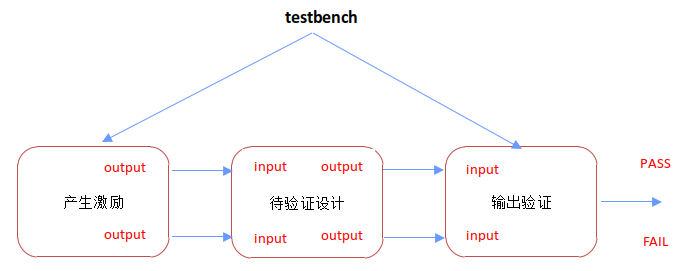

testbench是什么? testbench測(cè)試的機(jī)制是什么?

廢話(huà)不多說(shuō)直接上干貨,testbench就是對(duì)寫(xiě)的FPGA文件進(jìn)行測(cè)試的文件,可以是verilog也可以是VHDL。

2023-06-28 標(biāo)簽:FPGA設(shè)計(jì)交換機(jī)VHDL語(yǔ)言 4956 0

采用FPGA進(jìn)行的數(shù)字電路設(shè)計(jì)具有更大的靈活性和通用性,已成為目前數(shù)字電路設(shè)計(jì)的主流方法之一。

2019-07-24 標(biāo)簽:FPGA設(shè)計(jì)數(shù)字電路 4914 0

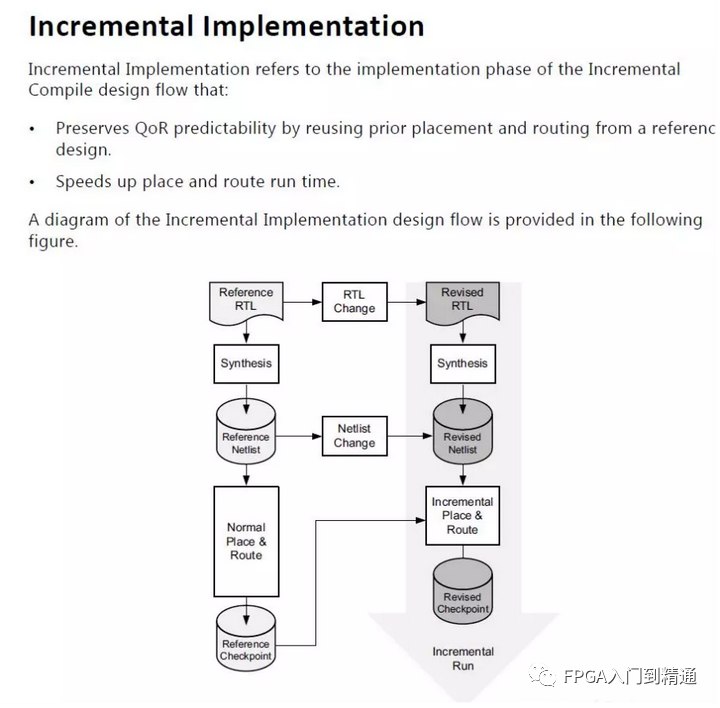

Vivado增量編譯的基本概念、優(yōu)點(diǎn)、使用方法以及注意事項(xiàng)

隨著FPGA設(shè)計(jì)的復(fù)雜度不斷提高,設(shè)計(jì)人員需要選擇更為高效的設(shè)計(jì)流程來(lái)保證開(kāi)發(fā)效率和減少開(kāi)發(fā)成本。其中,Vivado增量編譯是一種非常重要的設(shè)計(jì)流程。本...

2023-05-25 標(biāo)簽:fpgaFPGA設(shè)計(jì)時(shí)序 4859 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專(zhuān)題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |