完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > fpga設(shè)計(jì)

FPGA(Field-Programmable Gate Array),即現(xiàn)場(chǎng)可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。

文章:348個(gè) 瀏覽:26572次 帖子:90個(gè)

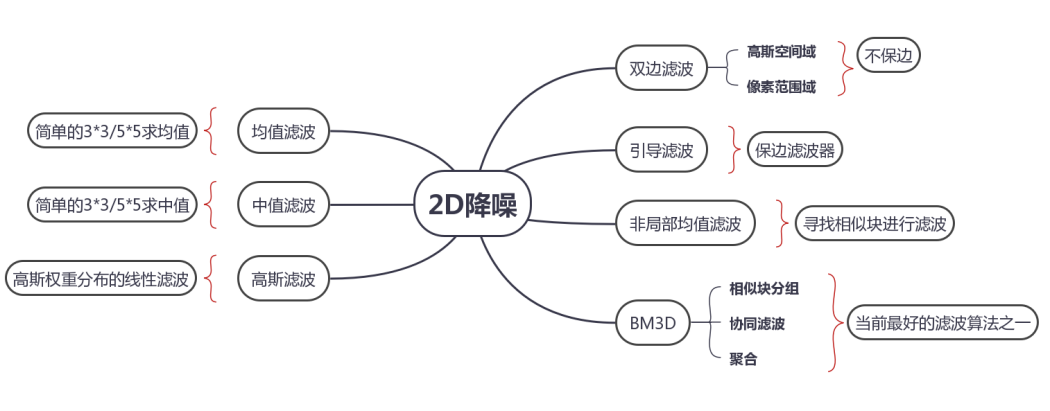

詳解從均值濾波到非局部均值濾波算法的原理及實(shí)現(xiàn)方式

圖像降噪處理主要分為2D(空域)與3D降噪(時(shí)域/多幀),而2D降噪由于相關(guān)的實(shí)現(xiàn)算法豐富,效果各異,初學(xué)入門有著豐富的研究?jī)r(jià)值。

2023-07-03 標(biāo)簽:濾波器FPGA設(shè)計(jì)比較器 2090 0

FPGA設(shè)計(jì)的D觸發(fā)器與亞穩(wěn)態(tài)

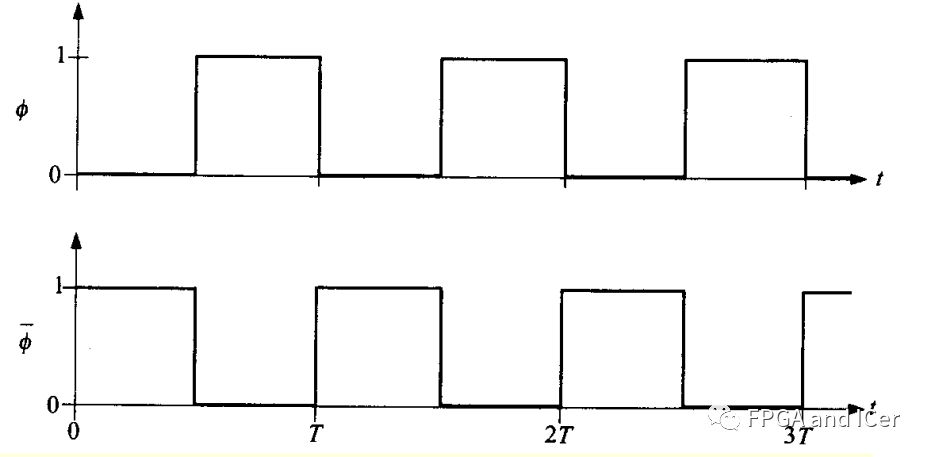

本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。對(duì)于FPGA和ASIC設(shè)計(jì)中,D觸發(fā)器是最常用的器件,也可以說(shuō)是時(shí)序邏輯的核心...

2023-05-12 標(biāo)簽:fpgaFPGA設(shè)計(jì)反相器 2082 0

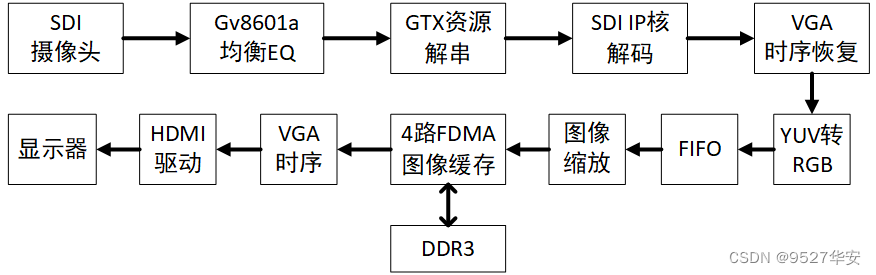

FPGA純verilog編解碼SDI實(shí)現(xiàn)流程

一是使用專用編解碼芯片,比如典型的接收器GS2971,發(fā)送器GS2972,優(yōu)點(diǎn)是簡(jiǎn)單,比如GS2971接收器直接將SDI解碼為并行的YCRCB,GS29...

2023-06-19 標(biāo)簽:FPGA設(shè)計(jì)DDR3接收器 2073 0

請(qǐng)問(wèn)如何將C語(yǔ)言算法移植到FPGA上?

確定算法:首先,你需要確保要移植的C語(yǔ)言算法是合適的。FPGA適合并行計(jì)算和高度可定制的應(yīng)用。因此,你需要選擇一個(gè)適合FPGA實(shí)現(xiàn)的算法。

2023-09-12 標(biāo)簽:FPGA設(shè)計(jì)VHDL語(yǔ)言C語(yǔ)言 2065 0

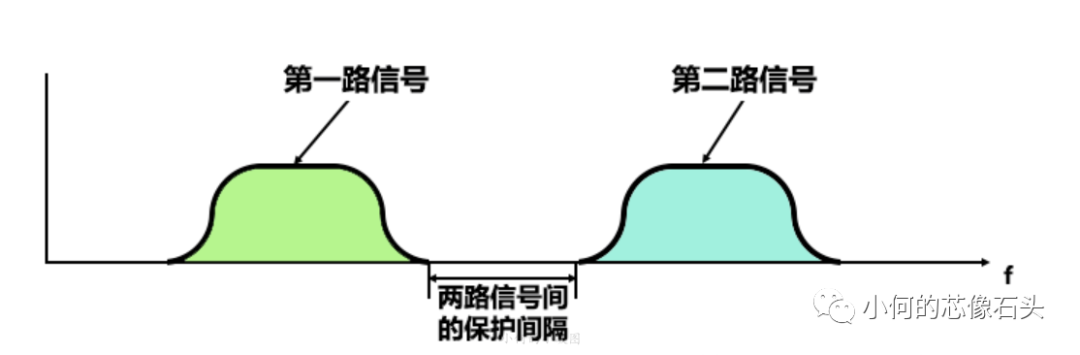

FPGA實(shí)現(xiàn)OFDM(1)-OFDM的原理是什么?

fromwiki:調(diào)制是將傳送資料對(duì)應(yīng)于載波變化的動(dòng)作,可以是載波的相位、頻率、幅度、或是其組合。

2023-06-27 標(biāo)簽:FPGA設(shè)計(jì)編碼器DFT 2061 0

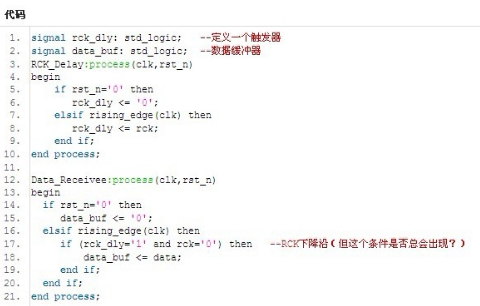

跨時(shí)鐘域是FPGA設(shè)計(jì)中最容易出錯(cuò)的設(shè)計(jì)模塊,而且一旦跨時(shí)鐘域出現(xiàn)問(wèn)題,定位排查會(huì)非常困難,因?yàn)榭鐣r(shí)鐘域問(wèn)題一般是偶現(xiàn)的,而且除非是構(gòu)造特殊用例一般的仿...

2023-05-25 標(biāo)簽:fpgaFPGA設(shè)計(jì)信號(hào) 2050 0

本系列整理數(shù)字系統(tǒng)設(shè)計(jì)的相關(guān)知識(shí)體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。在FPGA和ASIC設(shè)計(jì)中,時(shí)鐘信號(hào)的好壞很大程度上影響了整個(gè)系統(tǒng)的穩(wěn)定性,本...

2023-06-02 標(biāo)簽:驅(qū)動(dòng)器FPGA設(shè)計(jì)ASIC設(shè)計(jì) 2016 0

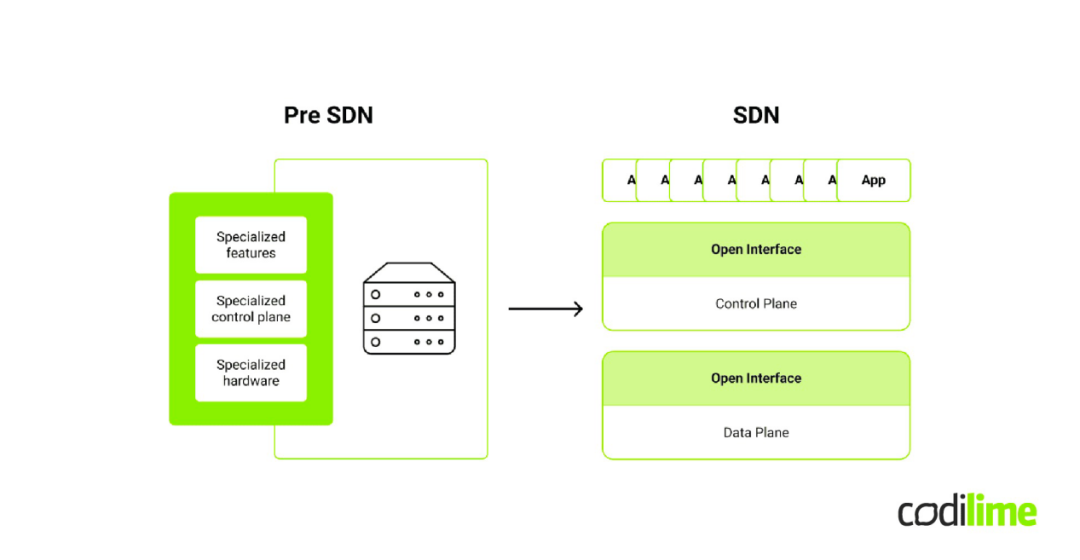

什么是硬件卸載?什么是軟件定義網(wǎng)絡(luò)?硬件卸載如何提供幫助?

CPU作為計(jì)算機(jī)的“大腦”扮演著重要的作用,網(wǎng)絡(luò)、存儲(chǔ)、計(jì)算……各種處理都需要CPU“親歷親為”,導(dǎo)致其負(fù)荷過(guò)重,極大地影響了效率。為了解決這個(gè)問(wèn)題,人...

2023-07-17 標(biāo)簽:處理器FPGA設(shè)計(jì)路由器 2005 0

怎樣使用Verilator進(jìn)行Verilog Lint呢?

FPGA設(shè)計(jì)是無(wú)情的,所以我們需要利用能獲得的任何軟件進(jìn)行檢查

2023-09-20 標(biāo)簽:FPGA設(shè)計(jì)仿真器SDL 1992 0

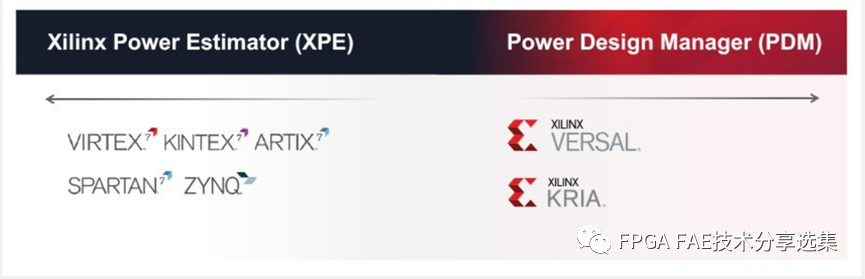

如何使用Power Design Manager(PDM)進(jìn)行功耗評(píng)估?

在基于FPGA和 SoC器件的產(chǎn)品設(shè)計(jì)過(guò)程中,從器件選擇到系統(tǒng)級(jí)電源設(shè)計(jì)、散熱設(shè)計(jì),電源功率估算對(duì)于設(shè)計(jì)方案確定至關(guān)重要;早

2023-10-08 標(biāo)簽:電源設(shè)計(jì)FPGA設(shè)計(jì)PDM 1985 0

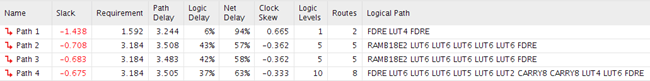

介紹FPGA設(shè)計(jì)中時(shí)序分析的一些基本概念

時(shí)鐘的時(shí)序特性主要分為抖動(dòng)(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Distortion)3點(diǎn)。

2023-03-16 標(biāo)簽:FPGA設(shè)計(jì)RAM時(shí)序分析 1972 0

FPGA設(shè)計(jì)中的亞穩(wěn)態(tài)解析

說(shuō)起亞穩(wěn)態(tài),首先我們先來(lái)了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號(hào)在無(wú)關(guān)信號(hào)或者異步時(shí)鐘域之間傳輸時(shí)導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。

2023-09-19 標(biāo)簽:fpgaFPGA設(shè)計(jì)信號(hào) 1948 0

FPGA設(shè)計(jì)經(jīng)驗(yàn):邊沿檢測(cè)

在同步電路設(shè)計(jì)中,邊沿檢測(cè)是必不可少的!

2017-08-16 標(biāo)簽:FPGAFPGA設(shè)計(jì)邊沿檢測(cè) 1931 0

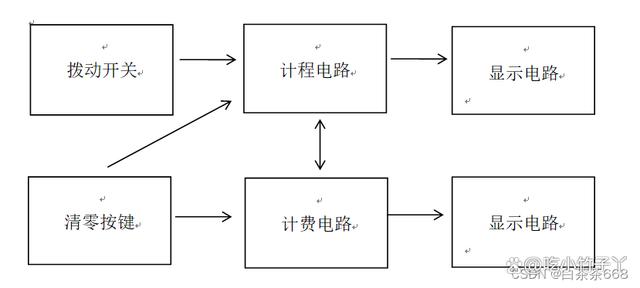

EDA程序設(shè)計(jì)—出租車計(jì)費(fèi)器

用EDA實(shí)訓(xùn)儀的I/O設(shè)備和FPGA實(shí)現(xiàn)出租車計(jì)費(fèi)器的設(shè)計(jì)。

2023-08-25 標(biāo)簽:FPGA設(shè)計(jì)led數(shù)碼管分頻器 1928 0

CDC跨時(shí)鐘域處理及相應(yīng)的時(shí)序約束

CDC(Clock Domain Conversion)跨時(shí)鐘域分單bit和多bit傳輸

2023-06-21 標(biāo)簽:FPGA設(shè)計(jì)RAMCDC 1896 0

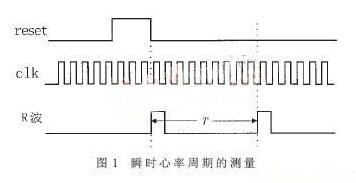

FPGA在數(shù)字式心率計(jì)中的電路組成及工作原理

心率計(jì)是常用的醫(yī)學(xué)檢查設(shè)備,實(shí)時(shí)準(zhǔn)確的心率測(cè)量在病人監(jiān)控、臨床治療及體育競(jìng)賽等方面都有著廣泛的應(yīng)用。心率測(cè)量包括瞬時(shí)心率測(cè)量和平均心率測(cè)量。瞬時(shí)心率不僅...

2019-01-01 標(biāo)簽:FPGA設(shè)計(jì)FPGA技術(shù) 1892 0

利用Artix-7 FPGA設(shè)計(jì)高性能USB器件

憑借在市場(chǎng)中數(shù)十億的端口數(shù)量,通用串行總線 (USB) 成為實(shí)現(xiàn)主機(jī)與外設(shè)之間千兆位以下連接的首選接口。不過(guò),由于 USB 規(guī)范有著嚴(yán)格的浪涌電流和穩(wěn)態(tài)...

2016-08-16 標(biāo)簽:FPGAFPGA設(shè)計(jì)USB 1892 0

在FPGA邏輯電路設(shè)計(jì)中,F(xiàn)PGA設(shè)計(jì)能達(dá)到的最高性能往往由以下因素決定。

2023-09-26 標(biāo)簽:fpga邏輯電路FPGA設(shè)計(jì) 1850 0

怎么使用MATLAB進(jìn)行O-RAN小基站建模和仿真?

開放式無(wú)線接入網(wǎng)(Open Radio Access Network,簡(jiǎn)稱 O-RAN)是一種無(wú)線接入網(wǎng) (RAN)。

2023-06-14 標(biāo)簽:matlabFPGA設(shè)計(jì)PHY 1838 0

基于FPGA的AES256光纖加密設(shè)計(jì)案例實(shí)現(xiàn)

近年來(lái),信息安全應(yīng)用于生活中的各個(gè)領(lǐng)域.在光通信系統(tǒng)中,往往對(duì)速率有著較高的追求。其中對(duì)光模塊,光纖通信中的傳輸算法,傳輸?shù)哪J揭约肮獠ǘ芜x取有密切關(guān)聯(lián)。

2024-05-10 標(biāo)簽:FPGA收發(fā)器FPGA設(shè)計(jì) 1828 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |