完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > FPGA設計

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。

fpga你可以理解成把一堆邏輯器件比如與門,或門,選擇器等放在一個盒子里,盒子周圍就是片子的引腳。通過邏輯編寫,把許多的門和許多選擇器等器件串聯或并聯引腳上。就等于把數電實驗在fpga里面做。

arm的編程指的是c語言或者匯編的編程,arm一條條的讀取語句,順序實現其功能。

fpga的編程則完全不同。fpga編程本身指的就是編輯其內部的電路結構。fpga運行代碼也不是一條條執行的,而是讀入代碼之后就生成了邏輯門結構。這些邏輯門結構是并行運作的。給輸入就同時產生輸出。所以fpga的編程語言叫做hdl(硬件描述語言)。hdl中的語句執行是不分先后的。

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

開發

FPGA的開發相對于傳統PC、單片機的開發有很大不同。FPGA以并行運算為主,以硬件描述語言來實現;相比于PC或單片機(無論是馮諾依曼結構還是哈佛結構)的順序操作有很大區別,也造成了FPGA開發入門較難。目前國內有專業的FPGA外協開發廠家,如[北京中科鼎橋ZKDQ-TECH]等。FPGA開發需要從頂層設計、模塊分層、邏輯實現、軟硬件調試等多方面著手。

FPGA怎么理解

fpga你可以理解成把一堆邏輯器件比如與門,或門,選擇器等放在一個盒子里,盒子周圍就是片子的引腳。通過邏輯編寫,把許多的門和許多選擇器等器件串聯或并聯引腳上。就等于把數電實驗在fpga里面做。

arm的編程指的是c語言或者匯編的編程,arm一條條的讀取語句,順序實現其功能。

fpga的編程則完全不同。fpga編程本身指的就是編輯其內部的電路結構。fpga運行代碼也不是一條條執行的,而是讀入代碼之后就生成了邏輯門結構。這些邏輯門結構是并行運作的。給輸入就同時產生輸出。所以fpga的編程語言叫做hdl(硬件描述語言)。hdl中的語句執行是不分先后的。

工程師談:FPGA設計之硬件

做FPGA也有兩年了,從剛開始的Verilog開始學起,到后來的最小系統,再到颶風II代開發板設計,到現在的XILINX XC2C系列CPLD開發,覆蓋了硬件設計底層的一些經驗。其實自己很想玩下FPGA的嵌入式,覺得很有前途的,但是后來自己也只是在學校開發板上過了下癮。談談如何玩FPGA吧

要了解FPGA首先弄懂它的結構,FPGA是基于LUT結構,在器件選型的時候一般是參考它的邏輯單元的大小,然后是功耗和匹配電平的關系,IO口供電電平;內部PLL供電電平;所有的FPGA工作電壓都是在3.3V,2.5V,1.2V三者之間選擇,當然一定要弄清楚IO口是基于CMOS還是TTL工藝的,兩者不能混淆。

選好器件后,接下來是原理圖設計。在原理圖設計中一般要注意去耦電容的容值大小,時鐘電路,內部鎖相環電路,下載電路。一般AS下載電路還要注意匹配的配置芯片的大小,在器件手冊上都能查到,所以在設計前一定要通讀對應的器件手冊,一般的配置電路手冊上都有參考,少走很多彎路。設計好原理圖后一般要考慮下面IO口的接法:GCLK/GRST;這些復用的管腳一般不用作普通的IO口。而用作對應的第二功能。

原理圖設計好后重點是PCB的設計,在設計前一定要反復檢查原理圖,是否有原理上的錯誤,一定注意電源電路的設計完整性。對于一般的TQFP封裝的芯片要注意采用雙面板我習慣把電源放在底層,濾波電容也通過過孔置于底層,在設計中當然是先布電源,時鐘,最后布信號線了,其中的一些小的細節不用我啰嗦了,想必各位比我還厲害了。

完成整個硬件電路板的設計后,接下來就是程序的設計了,這里面靈活性很大,在設計中一定要注意語法的嚴謹性,一個小小的“《=“都會帶來無盡的麻煩,在完成程序設計后,一定要進行時序仿真,我一般是先把模塊分塊利用工具內部波形仿真來查看時序,接著采用SIGNAL TAP II進行內部邏輯分析,這個花了太多時間了,一個仿真就要幾個小時。所以還是用TESTBENCH比較實際,注意是測試信號建立時間保持時間是否滿足時序要求。

以Xilinx公司最新的Vivado FPGA集成開發環境為基礎,將數字邏輯設計與硬件描述語言Verilog HDL相結合,循序漸進地介紹了基于Xili...

FPGA的用處比我們平時想象的用處更廣泛,原因在于其中集成的模塊種類更多,而不僅僅是原來的簡單邏輯單元(LE)。 早期的FPGA相對比較簡單,所有的功能...

流水線設計可以從某種程度上提高系統頻率。。前提是:設計可以分為若干步驟進行處理,而且整個數據處理的過程是單向的,即沒有反饋或者逆運算、前一個步驟的輸出是...

作者:張澤小腳丫STEP 導讀:FPGA(Field Programmable Gate Array)譯作中文為:現場可編程門陣列,也就是設計者可以在現...

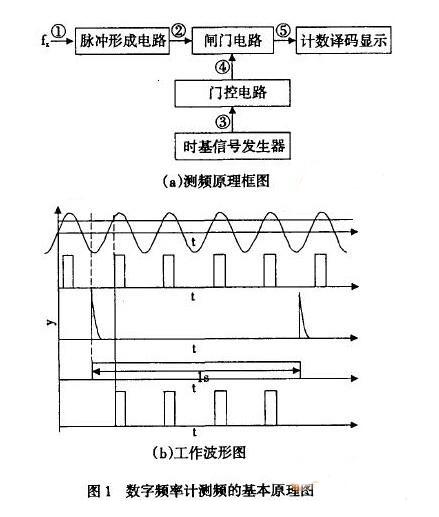

在電子工程,資源勘探,儀器儀表等相關應用中,頻率計是工程技術人員必不可少的測量工具。頻率測量也是電子測量技術中最基本最常見的測量之一。不少物理量的測量,...

2019-01-01 標簽:FPGA設計 6749 0

1、硬件設計基本原則 (1)速度與面積平衡和互換原則:一個設計如果時序余量較大,所能跑的頻率遠高于設計要求,能可以通過模塊復用來減少整個設計消耗的...

FPGA因為具備接口,控制,功能IP,內嵌CPU等特點有條件實現一個構造簡單,固化程度高,功能全面的系統產品設計將是FPGA技術應用最廣大的市場,具有極...

全硬件TCP/IP協議棧學習筆記 (第八天:W5500+FPGA實現tcp連接)

經歷了一個多月的調試,最終終于使用basys2將tcp模式配置成功了。 首先說一下思路吧,首先W5500的發送與接收與開發板的通信使用的是SPI協議,下...

全硬件TCP/IP協議棧學習筆記(第七天:FPGA+W5500 PING通)

在一周多的時間,從軟件的協議到芯片接口最后到硬件描述,我覺得是時候試一試芯片了,看一看能不能ping通。兩天時間終于完成第一次ping,也挺不容易的。 ...

把相對成熟的技術應用到某些特定領域如通訊,視頻,信息處理等等開發出滿足行業需要并能被行業客戶接受的產品這方面主要是FPGA技術和專業技術的結合問題,另外...

本文從硬件加速的視角考察深度學習與FPGA,指出有哪些趨勢和創新使得這些技術相互匹配,并激發對FPGA如何幫助深度學習領域發展的探討。

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |