對于FPGA調試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環境下進行仿真和調試,開發板類型EP4CE15F17。主要包括一下幾個部分:

- FPGA的調試-虛擬JTAG(Virtual JTAG)

- FPGA的調試-在線存儲器內容編輯工具(In-system Memory Content Editor)

- FPGA的調試-內嵌邏輯分析儀(SignalTap)

- FPGA的調試-LogicLock

- FPGA的調試-調試設計的指導原則

1、相關理論知識

1.1內嵌邏輯分析儀

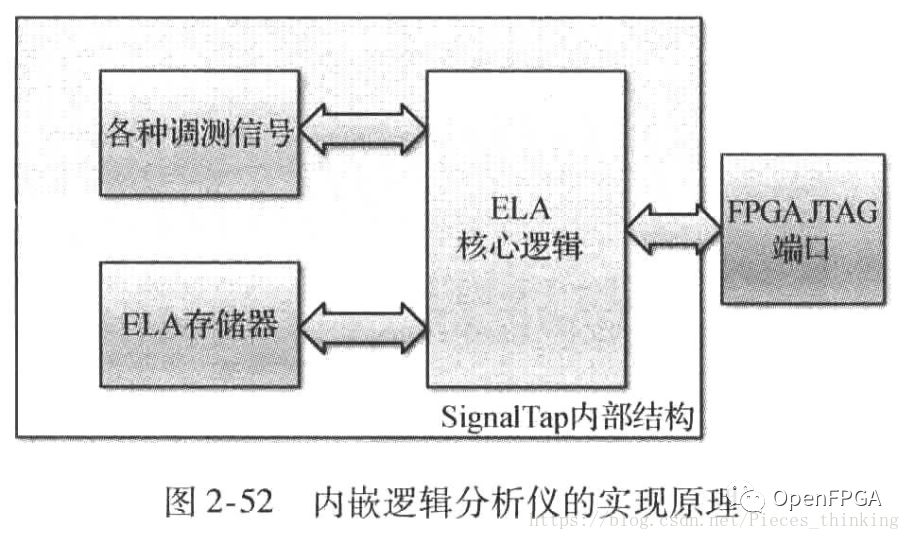

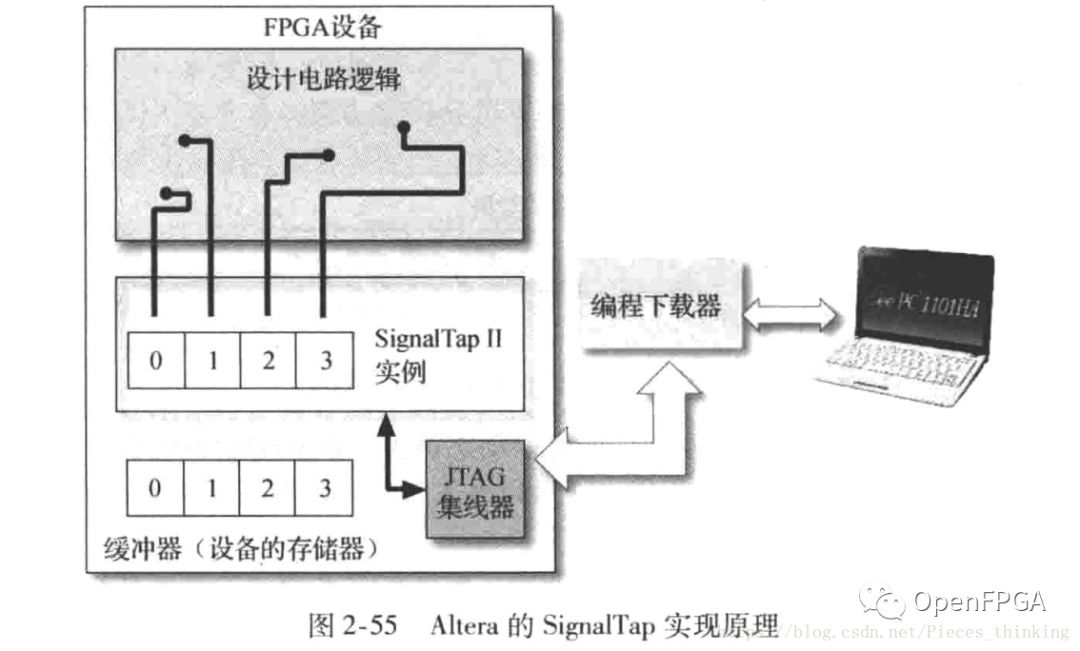

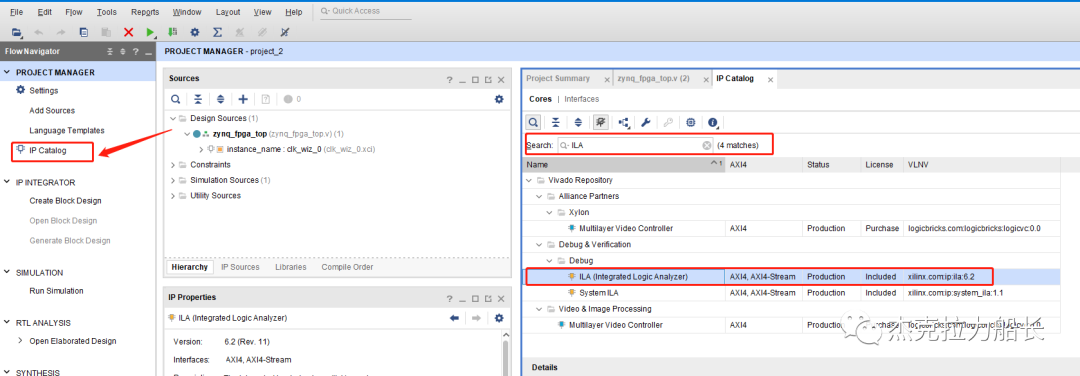

為方便用戶進行調試,FPGA通常會內置信號觀察邏輯,Altera提供的是SignalTap,而xilinx提供的則是ChipScope。此外還有第三方調試工具,如Synopsys的Identify。這類工具的核心原理為:以預先設定的時鐘速率實時采樣FPGA的內部信號或者引腳狀態,并存儲于FPGA的內部RAM中,然后通過統一的ELA(Embedded Logic Analyzer)進行數據分析和管理。當預設的觸發條件滿足后,ELA通過JTAG將存儲在片內RAM中的數據緩存數據傳輸至PC上。當PC獲得JTAG回傳數據后,通過本地計算將對應的邏輯分析結果展現出來。

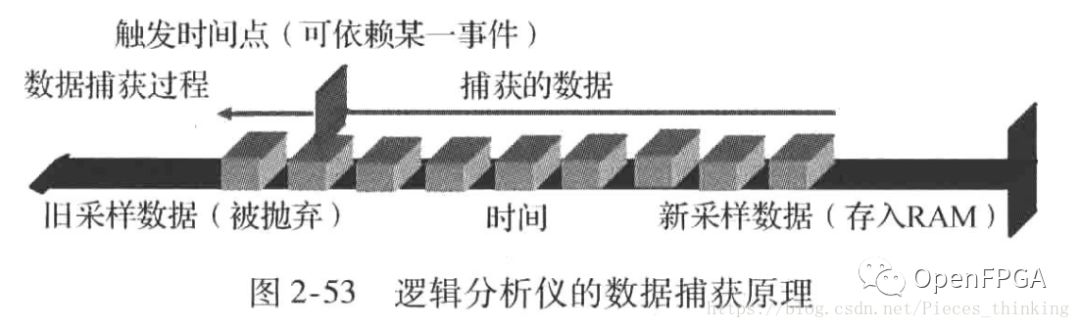

因此,無論是GignalTap還是ChipScope,其實都是在工程中額外加一些特殊模塊實現信號的采集,所付出的代價包括:邏輯單元、內部RAM以及ELA資源。邏輯分析儀的數據捕獲原理如圖2-53所示,所有存儲單元都是與當前邏輯設計的RAM共享的。如果當前邏輯占用RAM較大,內嵌的邏輯分析儀功能將會有非常大的存儲深度限制。

從圖2-53很容易發現,邏輯觸發的時刻可以動態調整,而且存儲的數據長度與時間也很容易調整。此外由于FPGA內置可編程能力,所以觸發條件可以依賴于其他的事件觸發,這樣可以多級觸發,形成基于狀態的數據捕獲。

例如當A信號為高電平,且持續32周期后,如果此時B信號為低電平且C信號有一個低脈沖,則觸發一個等待事件;當等待事件發生65536個時鐘周期后,再捕獲數據,并通過邏輯分析儀發送出來。這就是基于狀態機觸發的邏輯分析功能,類似于Verilog中的Assertion斷言和FSM狀態機的有機結合體,是傳統邏輯分析儀無法完成的。由于現在的邏輯通常都比較復雜,基于傳統的條件觸發模式,往往耗時耗力,很難快速找到BUG;而狀態觸發往往能夠幫助設計者快速定位錯誤并調試。

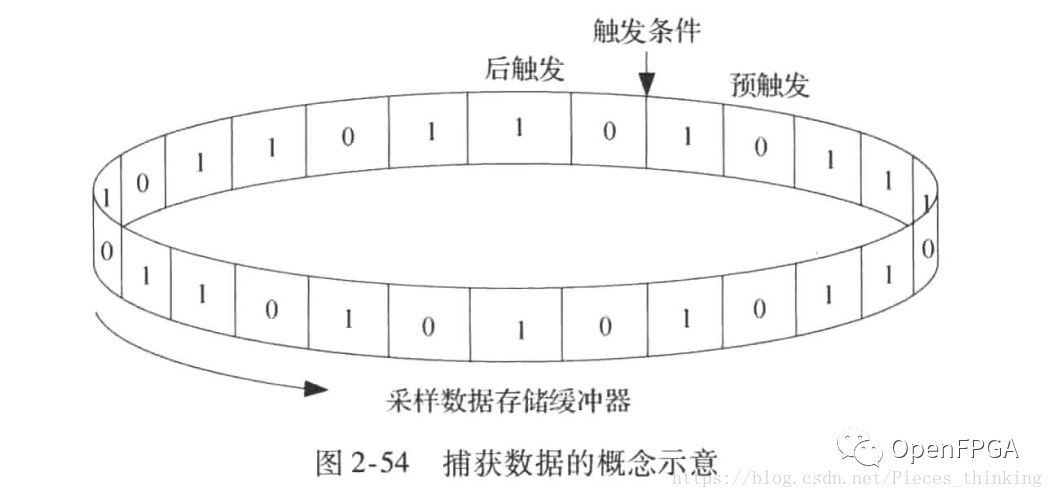

對于邏輯分析儀而言,除了觸發條件外,還有一個存儲位置的概念。正常情況下,FPGA會對需要CIA楊的數據一直采樣,當數據放滿后,將采用循環覆蓋的方式存儲,這類似于FIFO中的卷繞(WRAP)概念。當觸發器觸發后,通常緩沖器都是滿的;如果采用預觸發,將繼續記錄當前存儲容量12%的數據后停止(有些廠商是不再記錄,直接用當前記錄數據);如果采用后觸發,將繼續記錄當前存儲容量的88%的數據后,停止記錄(有些廠商是記錄全部容量);如果是中間觸發,將繼續記錄當前存儲容量的1/2的數據。實際上什么時候開始記錄,什么時候停止都可以通過狀態觸發實現。捕獲數據的概念示意圖如圖2-54所示。

下面通過SignalTAP為例,簡單講述內嵌邏輯分析儀的調試技巧。

1.2 SignalTap

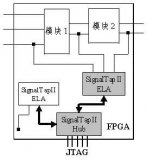

SignalTAP是Altera內置的邏輯信號觀測工具,內部實現結構如圖所示。

根據前面的邏輯分析儀原理,很容易得知FPGA可以實現多個并行的ELA。通過FSM和條件判斷支持多級觸發,FPGA也能夠支持復雜的狀態機數據捕獲。令觸發條件加上一個計數器,就很容易使FPGA能在不同的起始時刻捕獲數據。而Altera所設計的SignalTAP正好是按照上訴方式設計的,其特點如下:

最大支持1024個數據捕獲通道

單個器件支持多個并發的邏輯分析模塊,包括跨多個時鐘域的信號

每個數據捕獲通道能夠支持10級觸發

支持在不同的位置進行捕獲,包括信號前段、中段和后段。

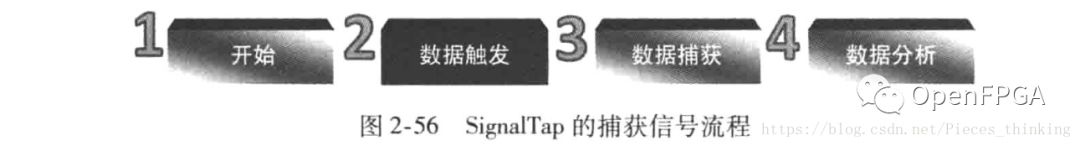

SignalTAP的捕獲流程如圖所示。 1.2.1 SignalTap的界面

1.2.1 SignalTap的界面

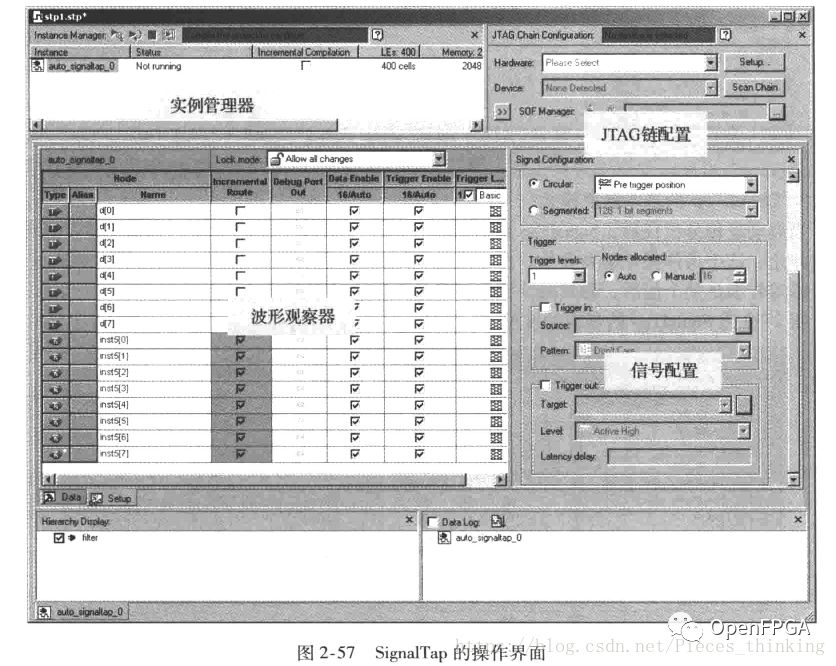

操作界面如圖所示。

1.2.2 SignalTap的演示

演示放在實例里

1.2.3 SignalTap的基本觸發模式

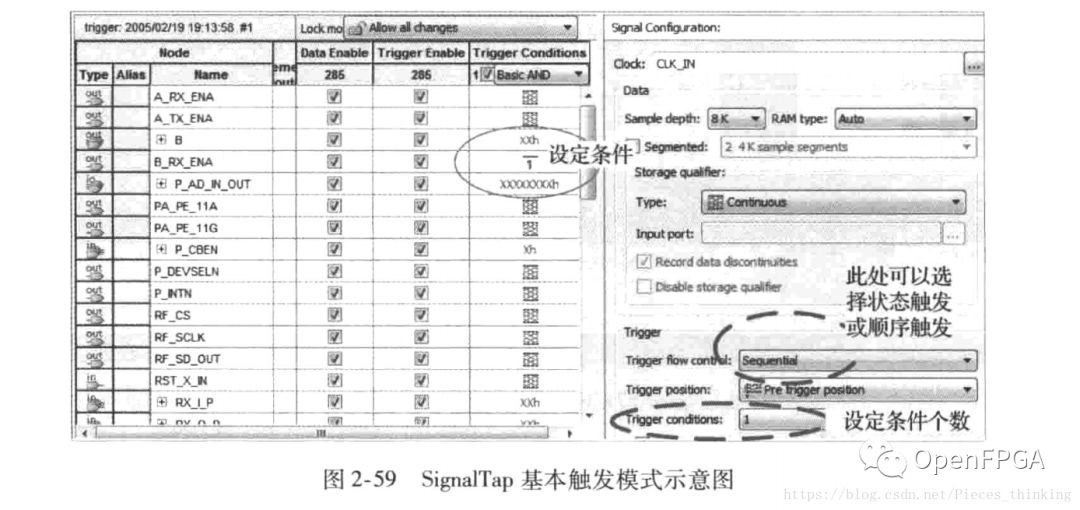

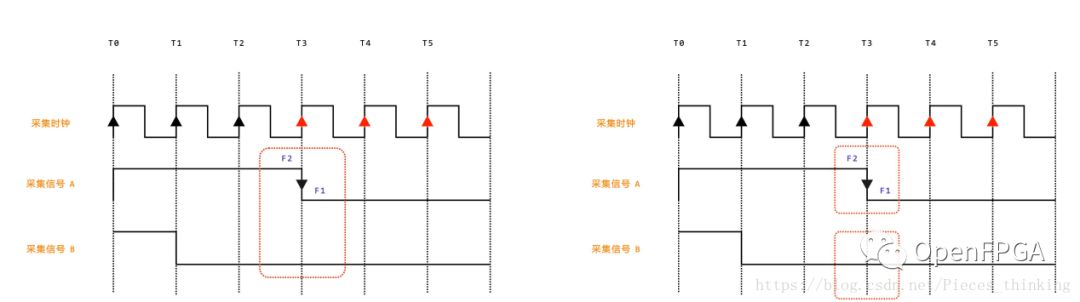

當啟動邏輯分析儀后,SignalTAP會對被監視的信號進行不斷的采樣,一直到某個條件滿足后停止,這個條件就是觸發條件。在基本模式下,觸發條件被設定為當前信號的邏輯組合。當邏輯組合滿足某個值后,觸發條件將被滿足,數據將被采樣保存并上傳到PC。

下圖是SignalTAP的基本觸發模式示意圖。

1.2.4 SignalTap的Advanced Trigger模式

在信號列表Trigger Conditions欄的頂端選擇Advanced,Advanced會彈出邏輯編輯器,在這里可以設計一個復雜的觸發表達式。

1.2.5 SignalTap基于狀態觸發的觸發模式

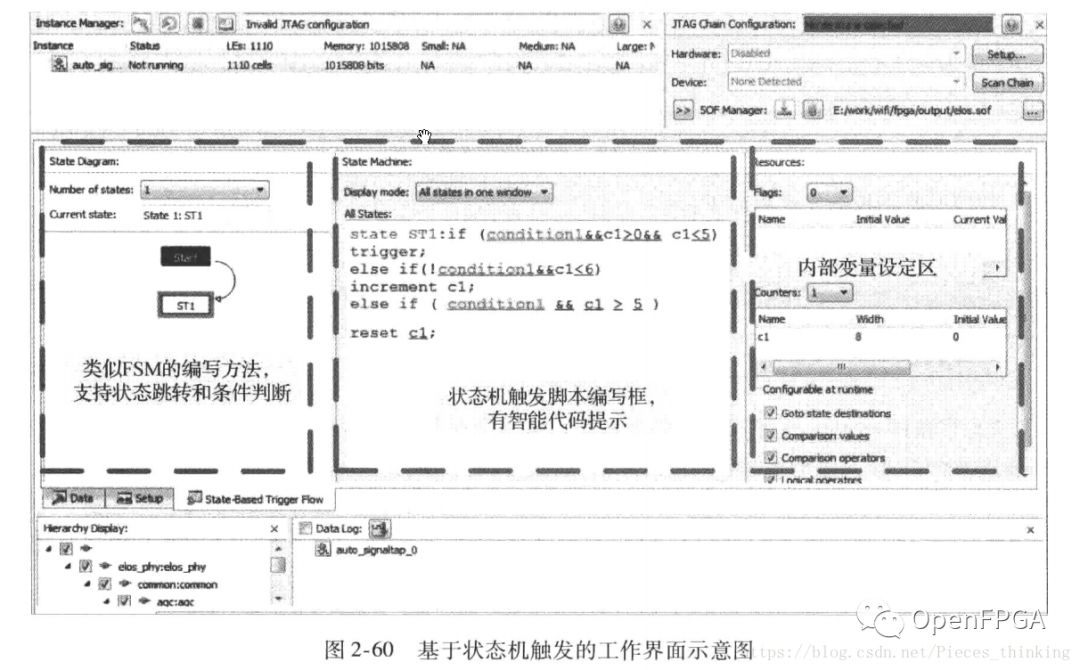

基于狀態觸發的邏輯分析儀模式是FPGA內嵌分析儀的而核心技術,主要技巧在于任何通過狀態觸發語句實現狀態機的觸發。下圖是狀態機觸發的工作界面。

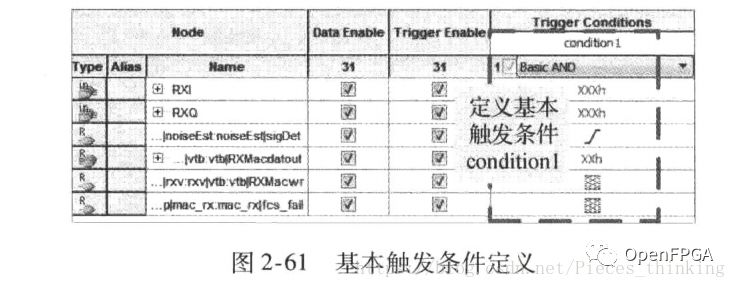

在設定觸發條件前,先需要確定基本的觸發條件,具體如圖所示。

在設定基本觸發條件后,就可以啟動狀態機的腳本設計,下面通過幾個例子來說明狀態機觸發的實現方法:

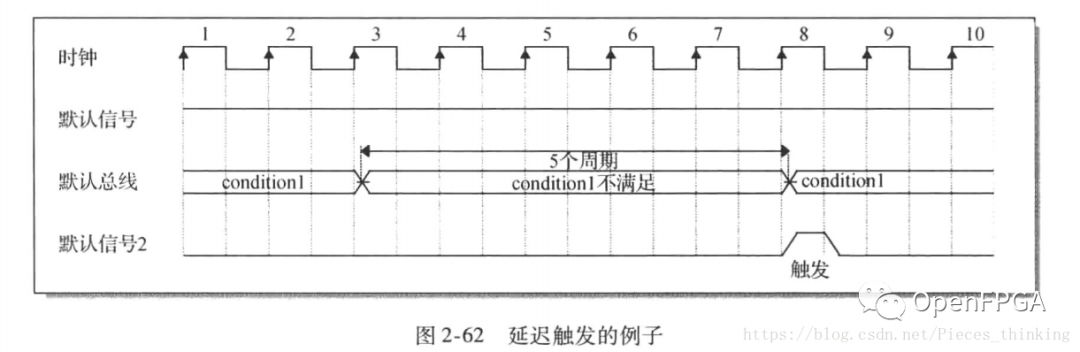

1)當條件condition1不滿足,且持續時間超過5個時鐘周期后,觸發觸發器,相關理想波形如圖所示:

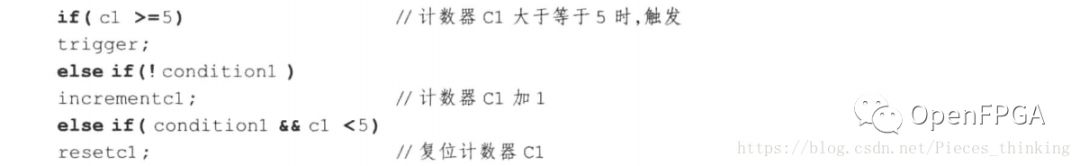

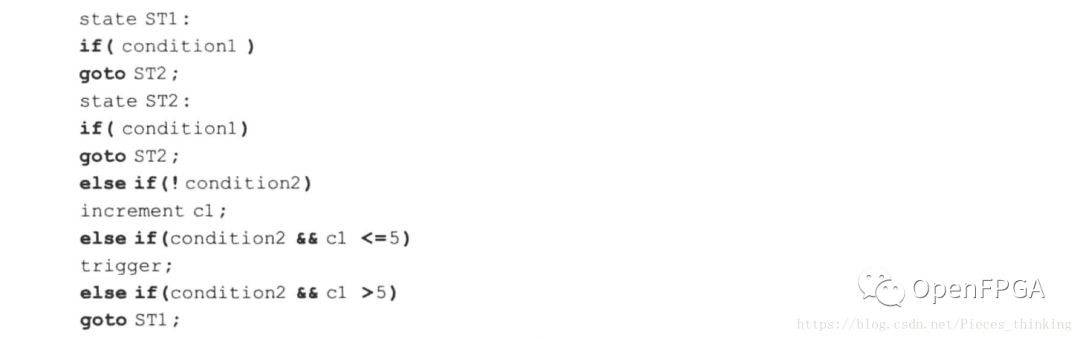

對應的狀態機觸發代碼如下:

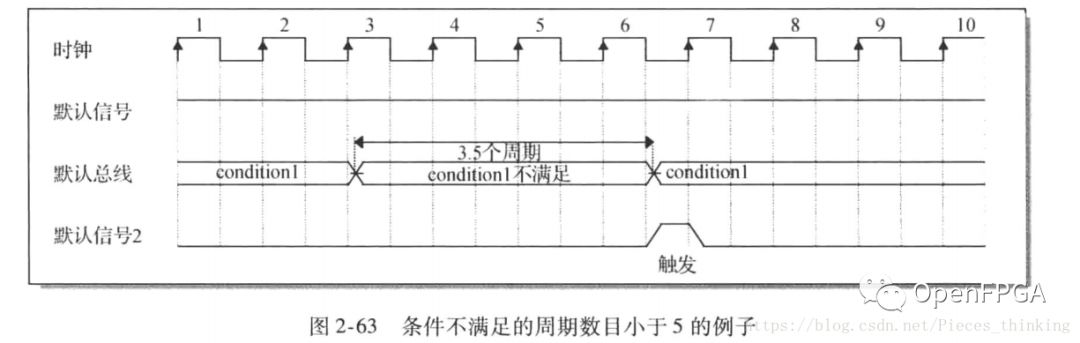

2)當條件condition1不滿足情況發生,且不滿足情況在不超過5個時鐘周期內,又發生條件condition1滿足的情況,則觸發觸發器,否則停止觸發。一個典型的例子圖下圖所示。

上訴觸發觸發器的腳本如下:

3)當condition條件滿足5次后,觸發觸發器,否則停止觸發。該例子的腳本如下:

4)當condition1條件滿足后,如果condition2能夠滿足,則立即觸發觸發器,否則停止觸發。該例子的腳本如下:

5)當condition1條件滿足后,如果5個采樣時鐘周期內,condition2能夠滿足,則立即觸發觸發器,否則停止觸發。該例子的腳本如下:

由于任何復雜的條件都可以簡化為順序、分支和循環3種情況,通過計數器能夠實現循環,通過條件判斷可實現分支,而通過狀態機可實現流程控制。因此任意復雜的條件觸發,都能夠通過上訴條件組合捕獲。

前面所舉的5個例子,就是上訴不同場景的組合,因此讀者只需要將上訴5個例子進行組合就能基本掌握觸發條件的實現,熟練進行FPGA調試。

2、簡單實例

2.1 新建工程

首先新建一個工程,然后添加文件,文件內容如下:

module test ( input CLOCK, RESET, output [7:0]oData ); reg [7:0]C1; always @ ( posedge CLOCK or negedge RESET ) if( !RESET ) C1 <= 8'd0; else if( C1 == 32 -1 ) C1 <= 8'd0; else C1 <= C1 + 1'b1; assign oData = C1; endmodule

邏輯非常簡單,其中,CLOCK是時鐘引腳,RESET是復位引腳,這只模塊的功能就是不斷重復計數,然后將計數

內容經由 Data 輸出。接下來綜合,分配引腳后就可以設置SigalTAP了。

1.2 配置SignalTapII Logic Analyzer

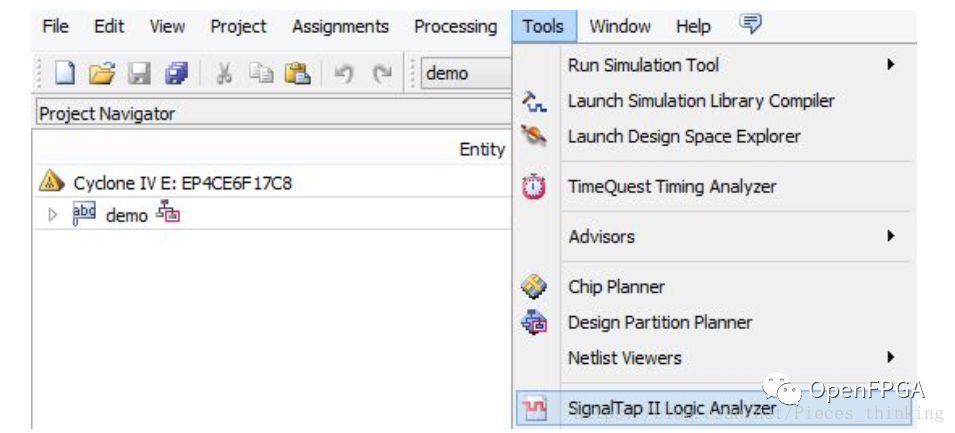

如圖所示,點擊 Tool 菜單,然后選擇 SignalTapII Logic Analyzer 便可啟動該工具。

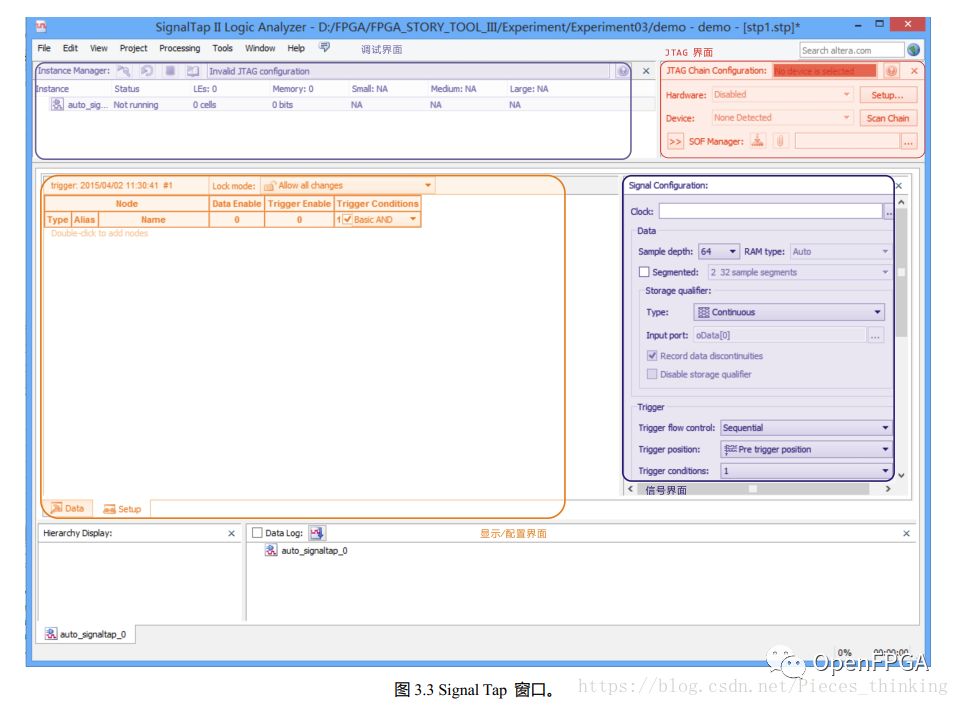

下圖是 Signal Tap 的窗口,其中 4 處高亮的地方是比較重要的界面。

(一)JTAG Chain Configuration,JTAG 界面,主要是設置 USB Blaster。

(二)Instance Manager,調試界面,主要是啟動,連續,結束等調試的活動。

(三)Signal Configuration,信號界面,主要是儲存,觸發等設置。

(四)Data,顯示界面,主要是顯示采集結果,時序活動。

(五)Setup,設置界面,主要是添加節點,設置觸發事件/條件等。

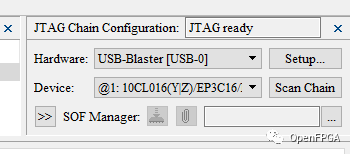

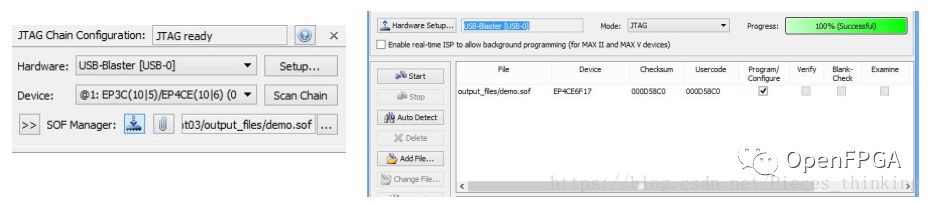

① JTAG 界面 - 配置 JTAG 以及下載對象

如圖所以,設備一旦上電,并且 USB Blaster 鏈接成功,那么 JTAG 界面就會進入緒狀態。

如圖 所示,SOF Manager 是小型下載管理器,讀者也可以經由一般的下載管理器完成下載工作,不過一切下載活動必須在配置結束以后才執行(綜合成功并且下載)。

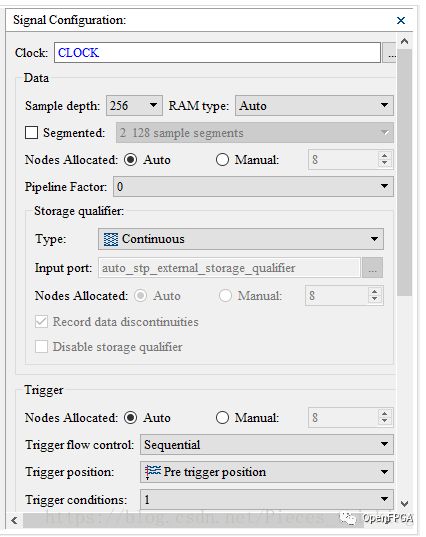

② 信號界面 - 配置采集時鐘,儲存,觸發:

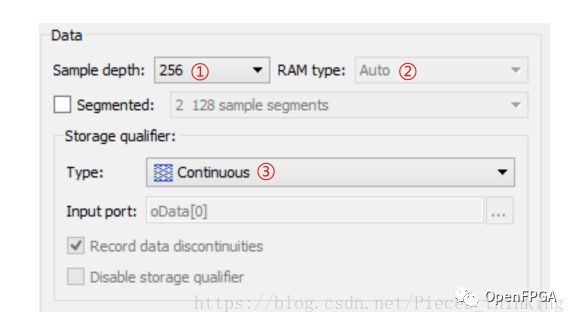

一旦 JTAG 就緒以后,我們就可以開始執行信號相關的配置。如圖 3.6 所示,默認下的信號界面都是這個樣子,其中:

? Clock 是采集時鐘

? Sample depth 是儲存/采集深度

? RAM Type 是儲存資源

? Storage Qualifier - type 是儲存方式

首先,讓我們設置采集時鐘,所以請點擊 Clock 選項右邊的 < … >,完后會彈出節點界面。

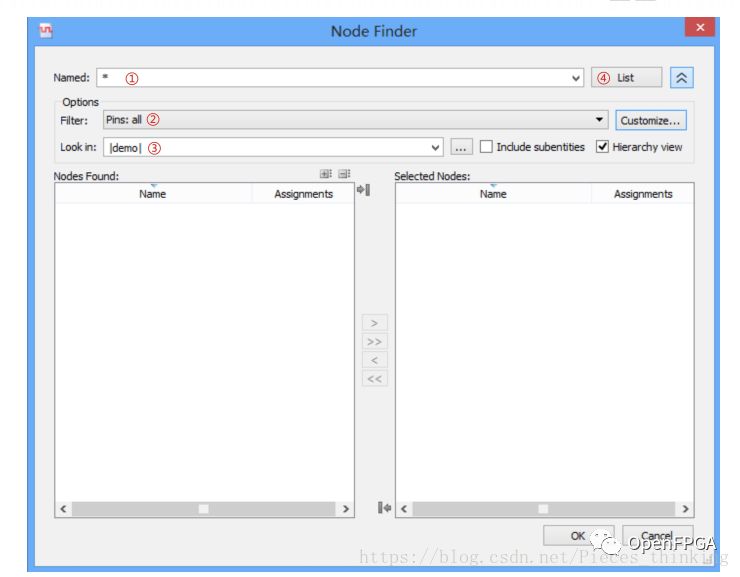

圖中 是節點界面,這點它和 Time Quest 非常相似:

① 請讀者保持 Named:* 不變的情況下,

② Filter 選擇為

③ 注意 Look in 指向頂層模塊 ,

④ 然后點擊右上角的 < List >。

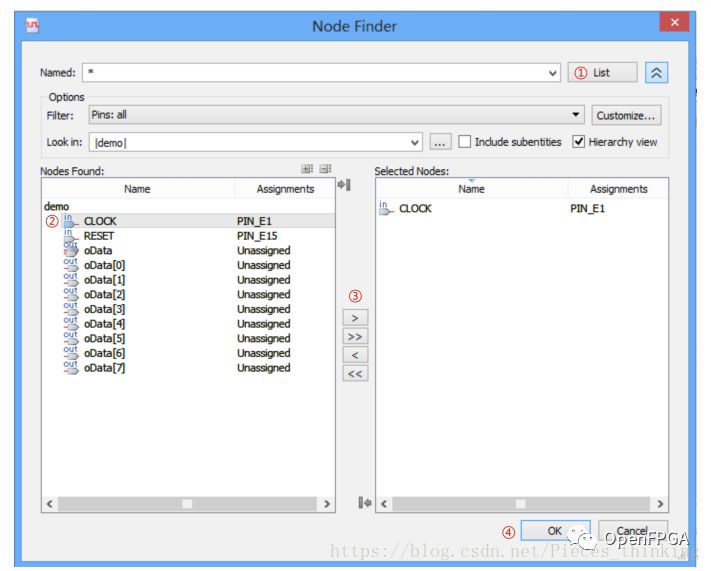

如下圖 所示,這是添加節點(采集時鐘)的步驟:

① 點擊 列出所有 demo 模塊相關的端口。

② 諸多端口之中,節點 CLOCK 將成為采集時鐘,然后點擊它。

③ 點擊 > 將該節點添加到右邊。

④ 點擊 < OK > 生效設置。

如下圖所示,采集時鐘設置完畢以后,Clock 右邊的文本框就會出現 CLOCK 的字眼。

如下圖 所示,一般上儲存相關的配置都會這樣設定:

① Sample depth 儲存深度按照感覺設置,這里是 256。

② RAM type 儲存資源,有 Auto 就設置,非常省事,不然就是 M4K/M9K,還是 Logic。

③ Storage qualifier - type 儲存方式選擇 Continuous 連續性即可。

讀者可能無法相信,高達 8 成的調試工作都是按照這樣的設定與配置。

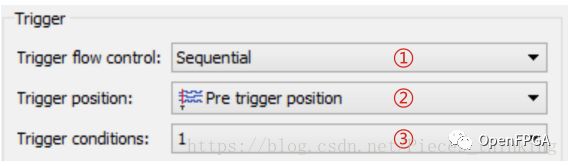

如圖 3.11 所示,一般上觸發相關的配置都是這樣設定:

① Trigger flow control,觸發條件流程,這里選擇 Sequential 順序性即可。

② Trigger position,觸發位置,這里選擇 Pre trigger position 即可。

③ Trigger conditions,觸發條件數,這里選擇一個即可。

同樣,讀者可能也無法相信,高達 8 成的調式工作也是按照這樣的觸發配置。到目前為止,信號界面的配置工作總算告一段落。

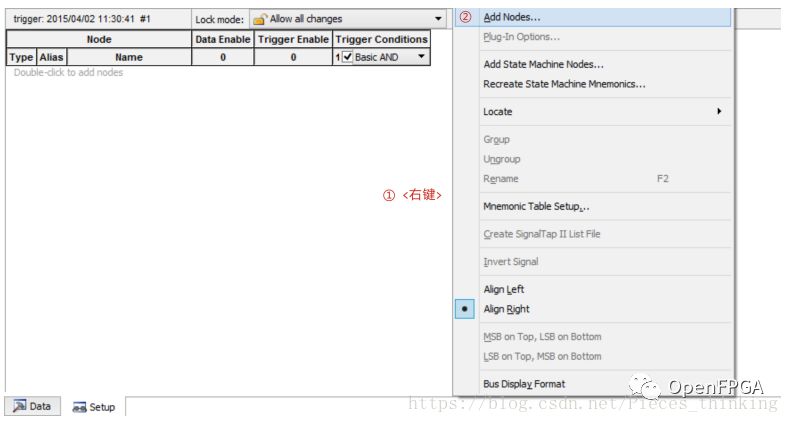

③ 配置界面 - 添加采集對象:

如圖 3.12 所示,配置界面就是添加節點(采集對象)的地方,默認下它是空空如也,我們必須自行添加對象才行。

① < 右鍵 > 調出菜單,

② 點擊 < Add Nodes … > 添加節點。

完成上面兩個步驟以后,它就會跳出節點界面。

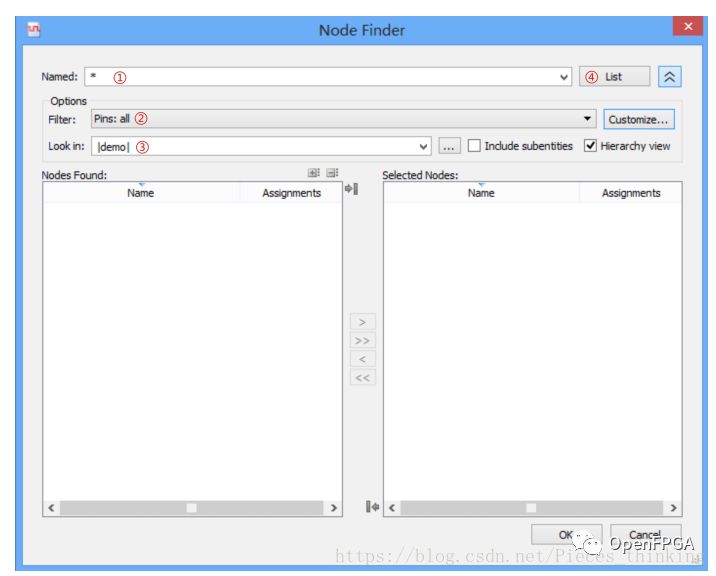

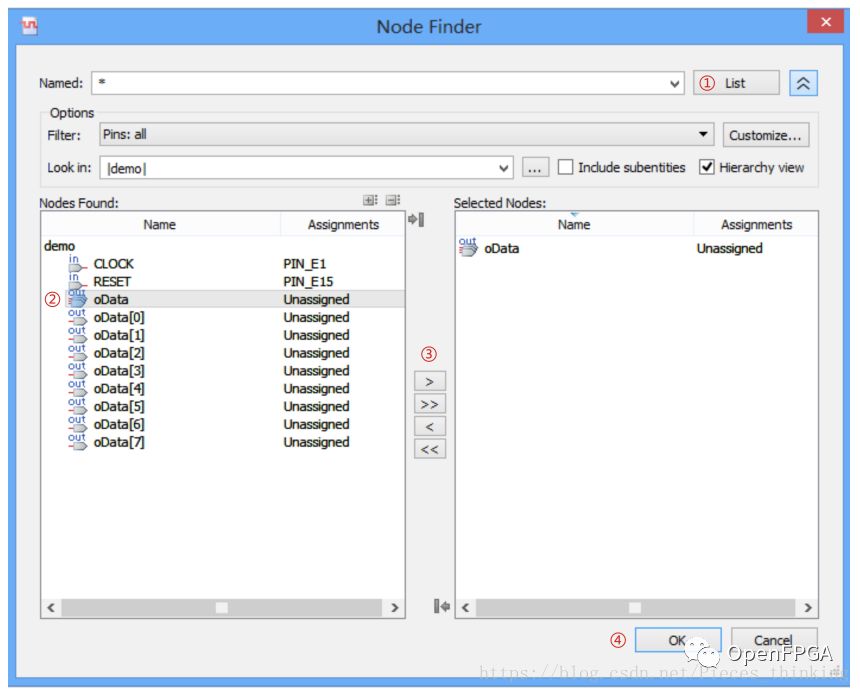

如上圖所示,同樣的節點界面再次出現:

① 請保持 Named:* 不變,

② Filter 設為 < Pins: all >,

③ Look in 設為 頂層模塊,

④ 點擊 列出,demo 模塊所有相關的端口。

如上圖 所示,假設 oData 是采集對象:

① 點擊 列出頂層模塊 demo 的所有端口,

② 選擇 oData,

③ 點擊 > 將節點添加到右邊去,

④ 點擊 生效配置。

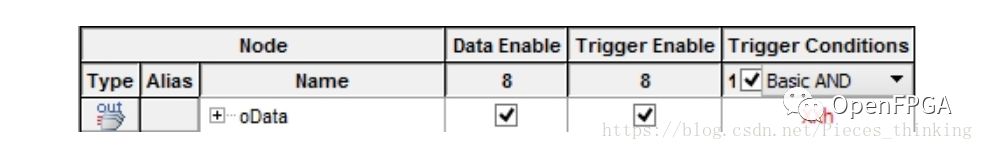

如下圖所示,如果一切無誤的話,那么節點(采集對象)oData 就會出現在配置界面之中。完后,我們可以開始配置觸發事件。

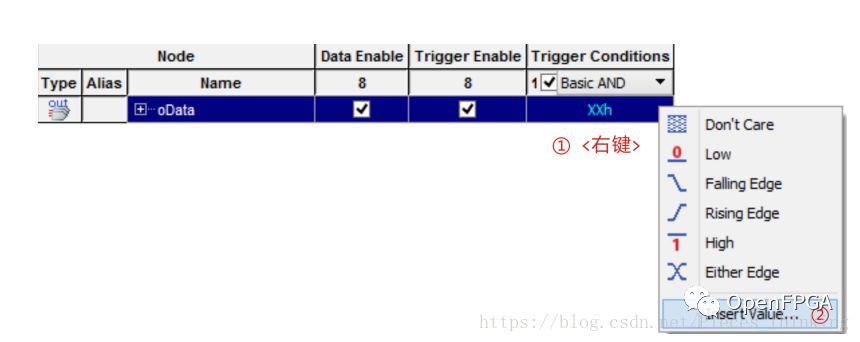

④ 觸發事件:

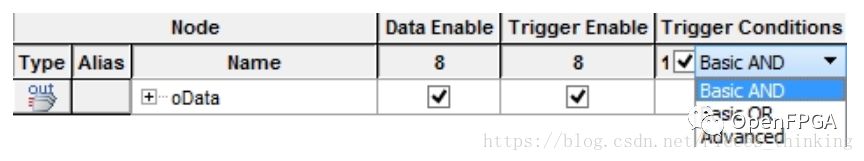

如上圖所示,筆者曾在前面說過觸發事件可以是單一或者復數,其中 Basic AND 與Basic OR 就是用來表達復數觸發事件的關系。我們以同樣的例子作為解釋 …

如上圖所示,假設信號 A 的下降沿是事件 1,信號 B 的低電平是事件 2,那么 Baisc AND的邏輯關系造成兩者在成立的情況下才執行采集。反之,Basic OR 的邏輯關系造成,任一事件成立都會執行采集。在此,筆者選擇 Basic AND 就好了 …

言歸正題。筆者也說過,Signal Tap 有預設觸發事件以及高級觸發事件,后者必須將觸發事件設為 Advance 才行,反之預設觸發事件可以:

① 觸發事件表框之處 <右鍵>,

② 選擇

默認下,Signal Tap 自帶 7 個預設觸發事件,在此筆者選擇數值的觸發事件,隨后會彈出相關的窗口。

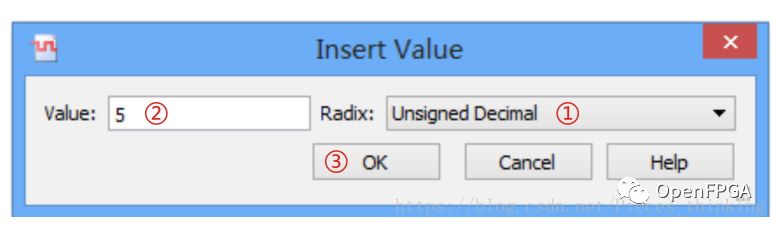

如上圖所示,這是配置數值觸發事件的窗口:

① 選擇格式,這里是 < Unsigned Decimal >,無符號位的十進制,

② 輸入數值,這里是 5,

③ 點擊 生效配置。

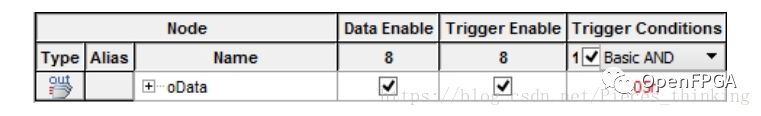

上圖 是觸發事件配置完畢的情況,其中 oData 為 5 執行采集。到目前為止,配置工作已經是完成八九十,余下再綜合一起便可下載至設備,期間系統可能要求保存一切配置,例如 stp1.stp 什么的,讀者可以保存在任一的地方。

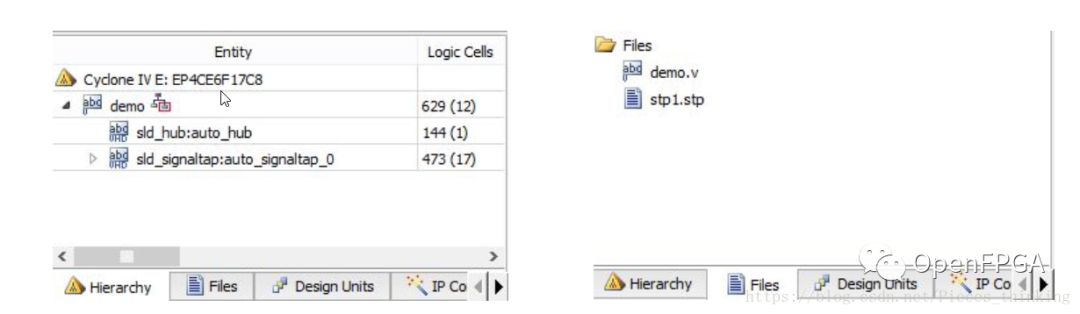

如圖一切無誤的話,那么實驗三層次關系與文件關系的結果如上圖 所示,其中 sld_×× 就是 Signal Tap 模塊的實例化,讀者也可以認為那是調試模塊(環境)。

⑤ 采集界面:

如圖 3.22 所示,程序下載以后,如果環境創建失敗的話,那么它會呈現紅色(左圖)。反之,如果環境創建成功,那么它會打印 Ready to acquire 的字眼。一般上,調試環境創建失敗有幾個原因:

JTAG 未就緒

程序下載失敗

綜合結果過期

設備未上電

以上 4 個原因排除以后,調試工作就處于就緒狀態。

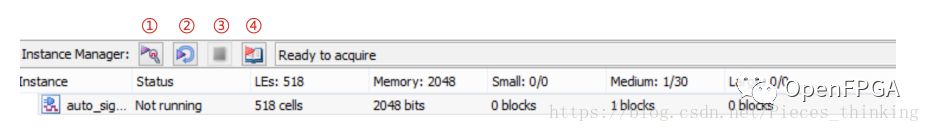

如圖 3.23 所示,采集界面主要有 4 個選項控制整個采集過程。

① Run Analysis 手動執行,觸發事件誘發采集,達到采集次數自動停止。

② Auto Analysis 自動執行,無視觸發事件,采集次數,采集一切。

③ Stop,停止執行,停止采集。

④ Read Data,讀取數據,讀取緩沖空間的內容。

一般上,如果觸發事件配置無誤的話,我們只要按下手動執行,那么觸發事件會誘發采集,當采集達到某個次數以后(根據儲存深度),采集過程就會結束。讀者沒有看錯,采集界面只有 4 個選項而已,其中手動執行最為有用,因為其它選項只有在采集失敗的情況下(觸發事件未達成)才會派上用場,真是諷刺。例如,停止執行要么強制停止失控的采集現場,要么配合自動執行一起使用。換之,讀取數據也是在采集失控的情況下,強制從設備中(緩沖空間)讀取數據。好了,我們稍微點擊一下手動執行,然后悄悄采集結果。

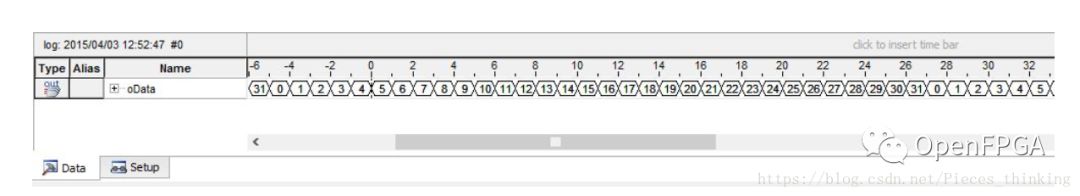

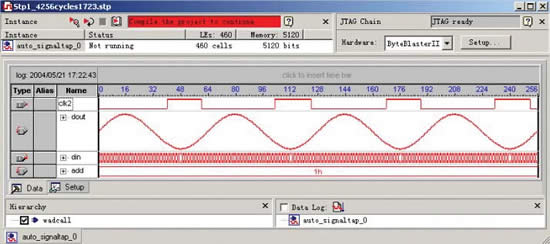

根據 demo 模塊,我們知道它重復計數 0~31。如圖 3.24 所示,T0 表示觸發事件的達成之際也是采集工作的開始,其中未來值 5 就是觸發事件的達成條件 … 簡單的調試工作也到此結束。

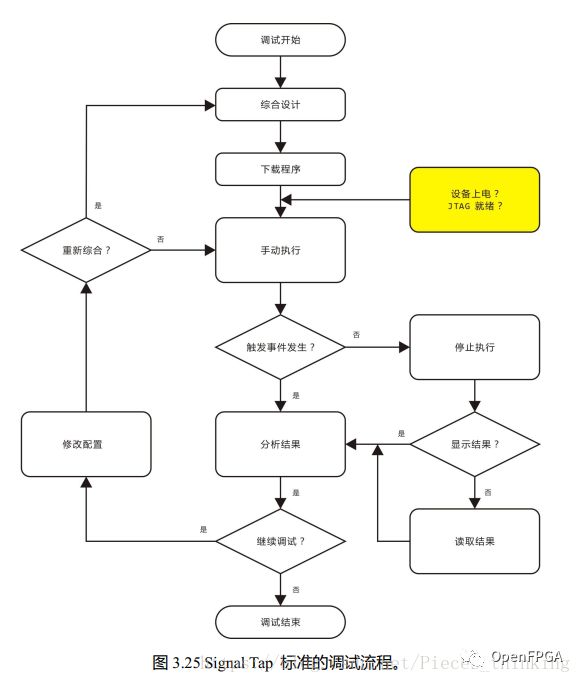

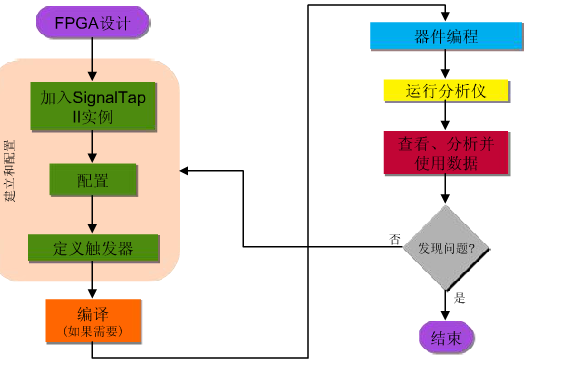

3 (補充)Signal Tap 標準調試流程

如圖 3.25 所示,雖說這是是官方指定的標準流程,不過筆者還是建議看看就好,千萬不要太認真,迷信“標準”這種東西很容易害死人。圖 3.25 有一處值得說明的地方是,觸發事件發生失敗的時候,如果跟著流程游蕩,它會要求手動停止分析,如果 Signal Tap顯示結果就進行分析,反之就是從設備哪里強制讀取結果。

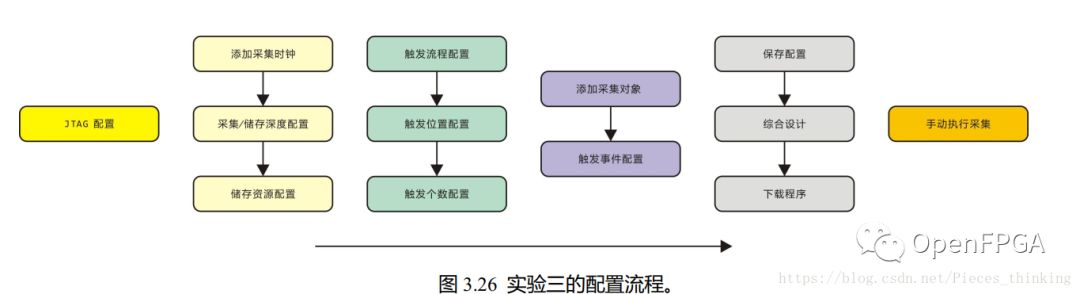

最后,好事的筆者也為實驗三的配置過程繪出一副流程圖,結果如圖 3.26 所示,讀者自己看著辦。

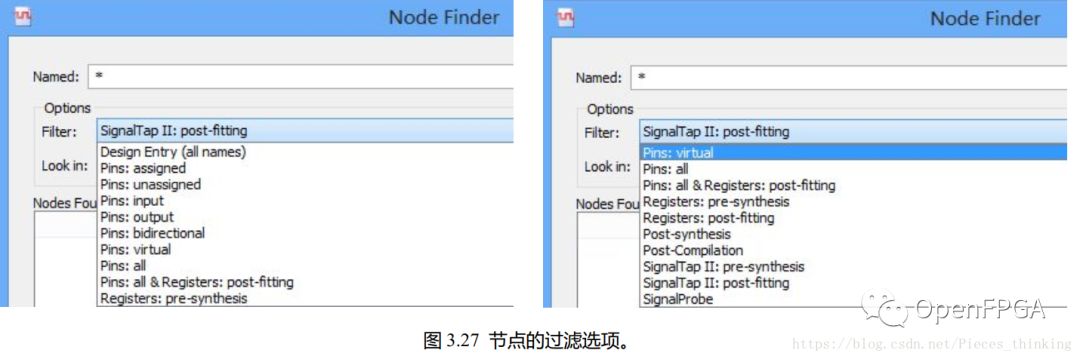

4 (補充)添加節點

筆者相信許多第一次接觸的同學都會畏懼節點的過濾選項。如圖 3.27 所示,不甘寂寞的官方為我們準備那么多選項,多少有些弄巧成拙的感覺,有關過濾選項基本上可以分為兩大類以致縮小范圍。其一是 Pin 端口類,其二就是 Reg 寄存器類,筆者喜歡的選項卻只有 Pins:all 以及 Register : pre-synthesis 兩個而已。

顧名思義 Pins:all 就是所有端口的意思,如果 Look in 指向模塊 A,那么模塊 A 的端口就會顯示出來(不管有沒有賦值驅動)。反之,Register:pre-synthesis 就是綜合以后的寄存器,如果 Look in 指向模塊 B,那么模塊 B 的所有寄存器都會暴露出來。除此之外,發狂的筆者偶爾不顧其它直接選擇 Design Entry,即不管什么鬼東西統統都給老子舉例出來 …

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26584 -

寄存器

+關注

關注

31文章

5363瀏覽量

120951 -

狀態機

+關注

關注

2文章

492瀏覽量

27618 -

邏輯分析儀

+關注

關注

3文章

214瀏覽量

23235 -

jtag接口

+關注

關注

0文章

34瀏覽量

13675

原文標題:FPGA的調試-內嵌邏輯分析儀(SignalTap)原理及實例

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

勇敢的芯伴你玩轉Altera FPGA連載74:基于SignalTap II的超聲波測距調試之功能簡介

勇敢的芯伴你玩轉Altera FPGA連載75:基于SignalTap II的超聲波測距調試之SignalTap II源文件創建

【夢翼師兄今日分享】 SignalTapII在線調試邏輯分析儀使用

如何使用SignalTap II邏輯分析儀調試FPGA?

使用SignalTap II邏輯分析儀調試FPGA

使用SignalTap II邏輯分析儀調試FPGA

【從零開始走進FPGA】 SignalTap II Logic Analyzer

FPGA視頻教程之SignalTap II邏輯分析儀使用指南資料免費下載

SignalTap II的特點、設置流程及邏輯分析儀的設計

淺析FPGA的調試-內嵌邏輯分析儀(SignalTap)原理及實例

淺析FPGA的調試-內嵌邏輯分析儀(SignalTap)原理及實例

評論