使用 C 語(yǔ)言的OpenCL 2a并行編程擴(kuò)展來(lái)補(bǔ)充基于 FPGA 的 CNN 加速應(yīng)用程序的開(kāi)發(fā)。適用于卷積神經(jīng)網(wǎng)絡(luò)的 FPGA 器件的一個(gè)示例是英特爾可編程解決方案集團(tuán) (PSG)的Arria 10系列器件,其正式名稱(chēng)為Altera。

2022-08-02 15:13:16 2622

2622

現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)具有低功耗、高性能和靈活性的特點(diǎn)。FPGA神經(jīng)網(wǎng)絡(luò)加速的研究正在興起,但大多數(shù)研究都基于國(guó)外的FPGA器件。為了改善國(guó)內(nèi)FPGA的現(xiàn)狀,提出了一種新型的卷積神經(jīng)網(wǎng)絡(luò)加速

2023-08-21 10:30:01 1859

1859

該卡可以使用脈沖神經(jīng)網(wǎng)絡(luò)而不是卷積神經(jīng)網(wǎng)絡(luò)(CNN)同時(shí)處理多種視頻格式的16路視頻。 BrainChip加速卡采用 Xilinx Kintex UltraScale FPGA實(shí)現(xiàn)了6核處理單元的BrainChip的Spiking神經(jīng)網(wǎng)絡(luò)(SNN)處理器。

2017-12-27 09:04:58 8017

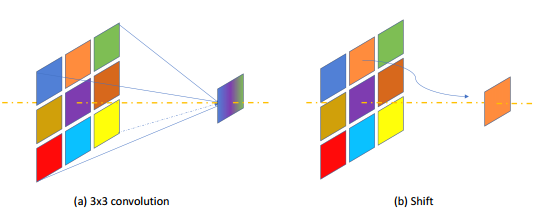

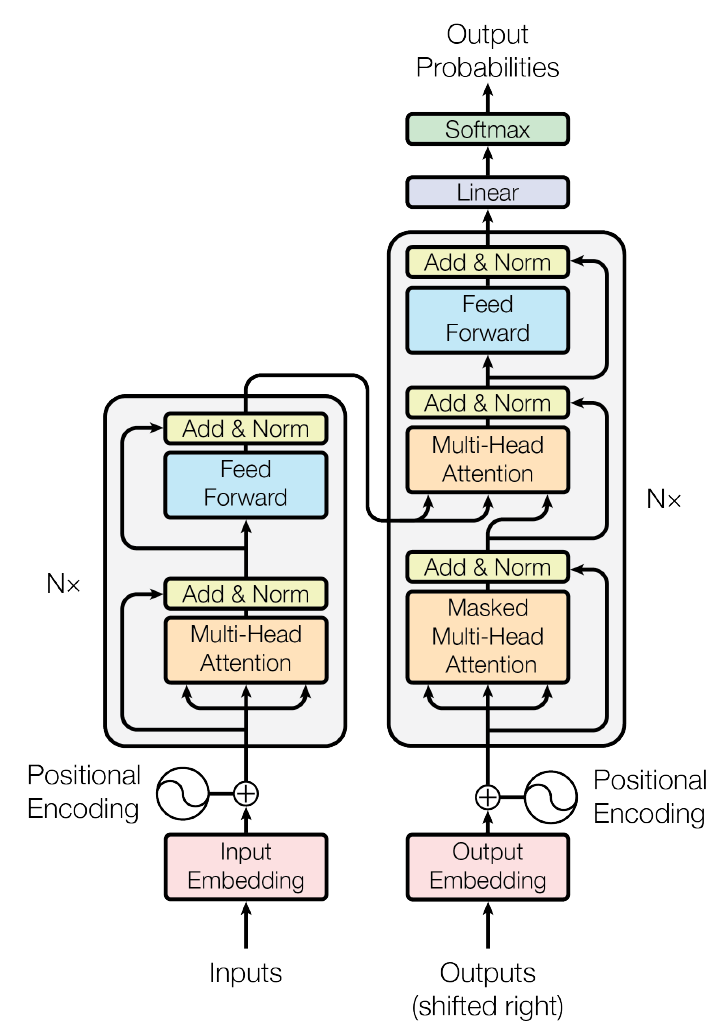

8017 前言 AI芯片(這里只談FPGA芯片用于神經(jīng)網(wǎng)絡(luò)加速)的優(yōu)化主要有三個(gè)方面:算法優(yōu)化,編譯器優(yōu)化以及硬件優(yōu)化。算法優(yōu)化減少的是神經(jīng)網(wǎng)絡(luò)的算力,它確定了神經(jīng)網(wǎng)絡(luò)部署實(shí)現(xiàn)效率的上限。編譯器優(yōu)化和硬件優(yōu)化

2020-09-29 11:36:09 4426

4426

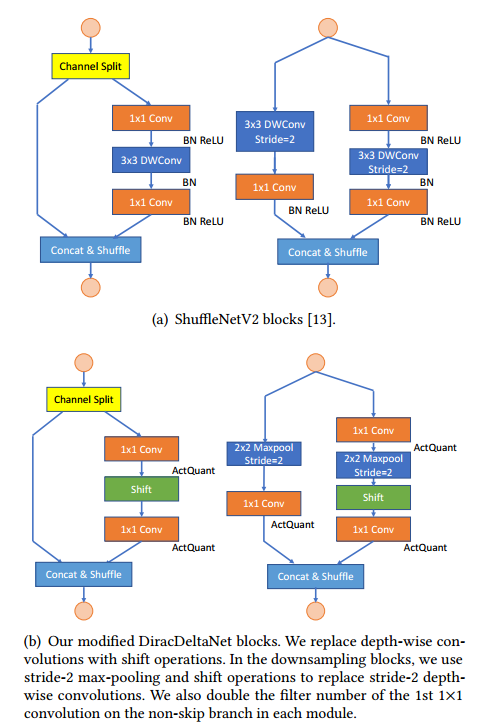

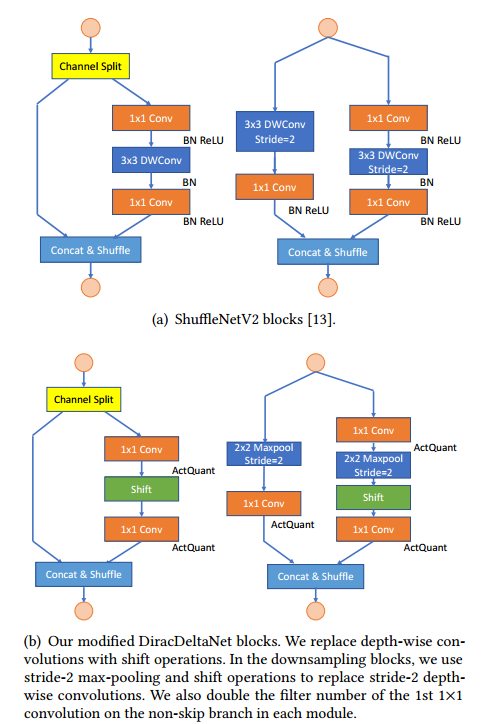

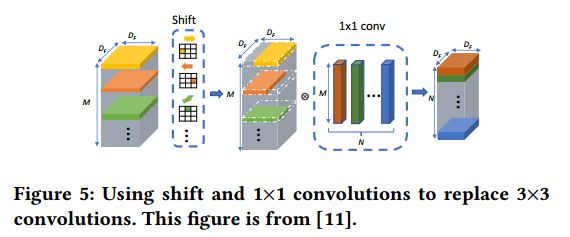

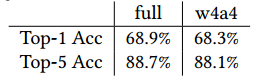

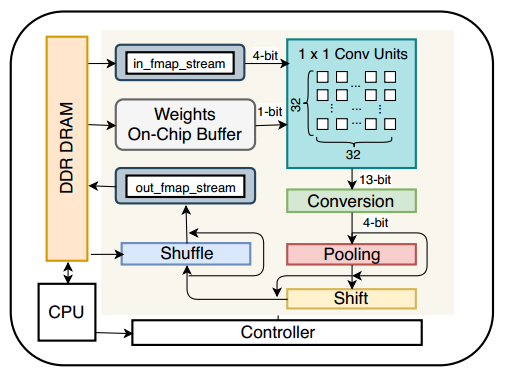

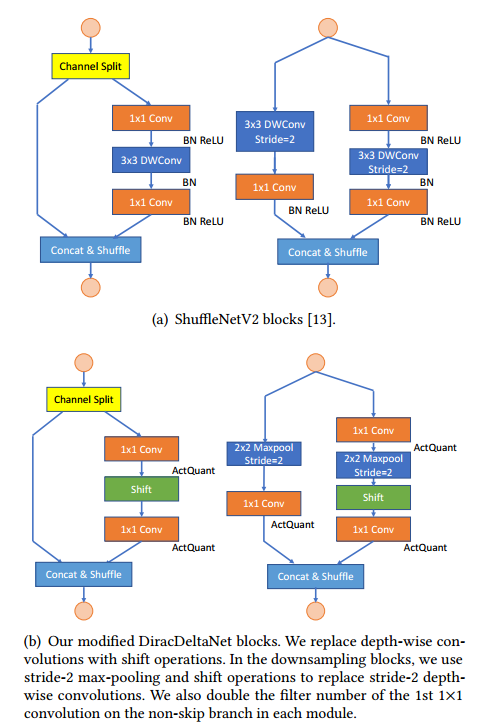

作者對(duì)shuffleNetV2網(wǎng)絡(luò)結(jié)構(gòu)進(jìn)行了更有利于FPGA部署的微調(diào)。

2020-11-21 10:36:02 2263

2263

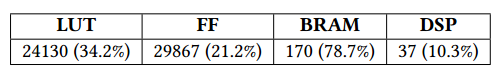

?一個(gè)卷積操作占用的內(nèi)存 2. PipeCNN可實(shí)現(xiàn)性 ??? PipeCNN論文解析:用OpenCL實(shí)現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速 ? ? 2.1?已實(shí)現(xiàn)的PipeCNN資源消耗 3. 實(shí)現(xiàn)大型神經(jīng)網(wǎng)絡(luò)

2022-07-10 09:24:45 1691

1691 各位高手,小弟想實(shí)現(xiàn)FPGA下的網(wǎng)絡(luò)數(shù)據(jù)包抓取,應(yīng)該怎么實(shí)現(xiàn)?功能與Sniffer相似!

2013-01-22 06:54:09

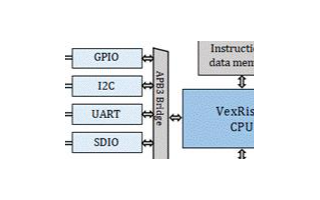

和外部設(shè)備。FPGA可以通過(guò)實(shí)現(xiàn)USB協(xié)議來(lái)支持USB通信。總的來(lái)說(shuō),選擇哪種網(wǎng)絡(luò)通信協(xié)議要根據(jù)應(yīng)用的具體需求和FPGA的性能來(lái)決定,需要對(duì)不同的協(xié)議進(jìn)行分析和評(píng)估。無(wú)意發(fā)現(xiàn)了個(gè)FPGA技術(shù)還不錯(cuò)的公司,叫芯加速,可以了解一下

2023-03-27 09:01:46

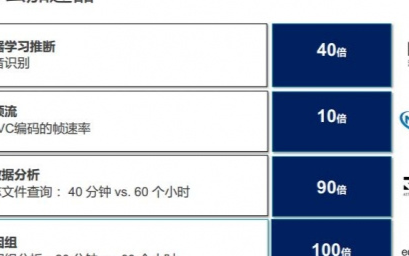

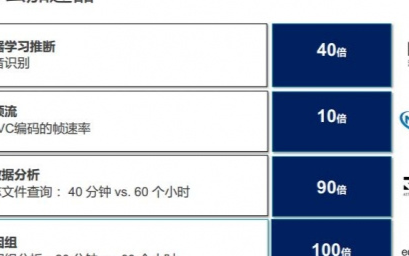

對(duì)于各種不同的數(shù)據(jù)中心工作負(fù)載,FPGA 可以顯著提高性能,最大程度減少附加功耗并降低總體擁有成本 (TCO)。

2019-08-13 08:03:44

是其中的一個(gè)分支:卷積神經(jīng)網(wǎng)絡(luò)(CNN)。團(tuán)隊(duì)使用FPGA對(duì)CNN計(jì)算進(jìn)行加速,增強(qiáng)違規(guī)圖片檢測(cè)能力,最終在深度學(xué)習(xí)的實(shí)踐中取得了FPGA處理性能是CPU機(jī)器4倍的戰(zhàn)績(jī)。騰訊云FPGA項(xiàng)目實(shí)踐的結(jié)果

2017-04-15 16:17:41

斯坦福大學(xué)與賽靈思研究實(shí)驗(yàn)室(Xilinx Research Labs)聯(lián)手開(kāi)發(fā)專(zhuān)門(mén)面向研究社群的第二代高速網(wǎng)絡(luò)設(shè)計(jì)平臺(tái) NetFPGA-10G。該新型平臺(tái)采用最先進(jìn)的技術(shù),能夠幫助研究人員迅速構(gòu)建

2011-07-19 15:51:05

FPGA加速的關(guān)鍵因素是什么?EdgeBoard中神經(jīng)網(wǎng)絡(luò)算子在FPGA中的實(shí)現(xiàn)方法是什么?

2021-09-28 06:37:44

USB 芯片和軟件廠商飛特蒂亞(FTDI)公司發(fā)布一款靈活而強(qiáng)大的開(kāi)發(fā)平臺(tái) Morph-IC-II,可加速基于FPGA的應(yīng)用與制作,并簡(jiǎn)化先進(jìn)邏輯電路設(shè)計(jì)中整合高速480Mbit/s USB通訊作業(yè)

2019-07-03 08:29:05

算法的軟件實(shí)現(xiàn)方式非常低效,所以業(yè)界對(duì)GNN的硬件加速有著非常迫切的需求。我們知道傳統(tǒng)的CNN(卷積神經(jīng)網(wǎng)絡(luò)網(wǎng)絡(luò))硬件加速方案已經(jīng)有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究,在

2021-07-07 08:00:00

實(shí)現(xiàn)了一種I/O流水線(xiàn)接口,該接口具有I/O連接加速器的典型性能。FPGA/PowerPC/APU接口FPGA允許硬件設(shè)計(jì)工程師利用單芯片上的處理器、解碼邏輯、外設(shè)和協(xié)處理器實(shí)現(xiàn)一個(gè)完整的計(jì)算系統(tǒng)

2015-02-02 14:18:19

項(xiàng)目名稱(chēng):基于PYNQ的卷積神經(jīng)網(wǎng)絡(luò)加速試用計(jì)劃:申請(qǐng)理由:本人研究生在讀,想要利用PYNQ深入探索卷積神經(jīng)網(wǎng)絡(luò)的硬件加速,在PYNQ上實(shí)現(xiàn)圖像的快速處理項(xiàng)目計(jì)劃:1、在PC端實(shí)現(xiàn)Lnet網(wǎng)絡(luò)的訓(xùn)練

2018-12-19 11:37:22

神經(jīng)網(wǎng)絡(luò)(CNN)、循環(huán)神經(jīng)網(wǎng)絡(luò)(RNN)等,并且涉及大量并行計(jì)算和流水線(xiàn)設(shè)計(jì),因此我在這里再寫(xiě)一個(gè)矩陣乘法加速器的VHDL實(shí)現(xiàn):

-- 好了,各位觀眾,我們現(xiàn)在要上演的是\"FPGA如何成為

2024-02-12 16:18:43

算法設(shè)計(jì)及其實(shí)現(xiàn)技術(shù)帶來(lái)了嚴(yán)峻的挑戰(zhàn)。在這種情況下,許多全新的基于圖形的機(jī)器學(xué)習(xí)算法或圖神經(jīng)網(wǎng)絡(luò)(GNN)不斷在學(xué)術(shù)界和工業(yè)界涌現(xiàn)。GNN對(duì)計(jì)算能力和存儲(chǔ)有非常高的要求,而且其算法的軟件實(shí)現(xiàn)效率非常低

2021-09-25 17:20:41

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速?

2021-04-13 06:39:25

為你的FPGA設(shè)計(jì)加加速,NIC、Router、Switch任意實(shí)現(xiàn)

優(yōu)秀的IC/FPGA開(kāi)源項(xiàng)目(二)-NetFPGA

《優(yōu)秀的IC/FPGA開(kāi)源項(xiàng)目》是新開(kāi)的系列,旨在介紹單一項(xiàng)目,會(huì)比《優(yōu)秀

2023-11-01 16:27:44

在FPGA上加速過(guò)winograd嗎,有沒(méi)有和arm端做過(guò)加速結(jié)果比較

2022-09-21 11:28:56

適合加速卷積神經(jīng)網(wǎng)絡(luò),但與之對(duì) 應(yīng)的是 GPU 有著功耗高,空間占用大等缺點(diǎn),很多場(chǎng)合對(duì)功耗有嚴(yán)格的限制,而 GPU 難 以應(yīng)用于這類(lèi)需求。近些年來(lái) FPGA 性能的不斷提升,同時(shí) FPGA 具有

2023-06-20 19:45:12

FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)關(guān)鍵問(wèn)題分析基于FPGA的ANN實(shí)現(xiàn)方法基于FPGA的神經(jīng)網(wǎng)絡(luò)的性能評(píng)估及局限性

2021-04-30 06:58:13

FPGA加速卡是如何產(chǎn)生的?主要的FPGA加速卡產(chǎn)品有哪些?基于加速卡的FPGA生態(tài)系統(tǒng)布局是怎樣的?

2021-06-17 06:07:15

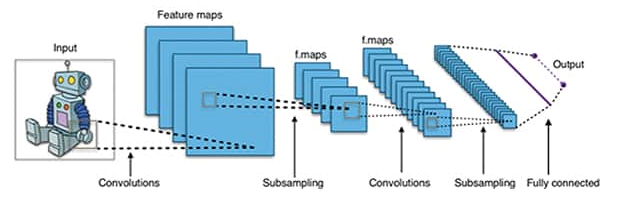

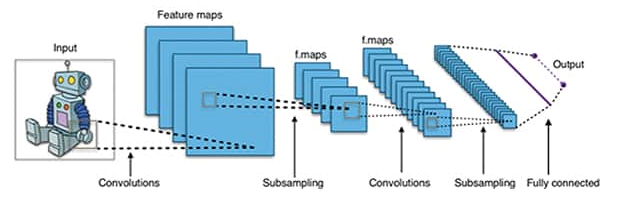

FPGA 上實(shí)現(xiàn)卷積神經(jīng)網(wǎng)絡(luò) (CNN)。CNN 是一類(lèi)深度神經(jīng)網(wǎng)絡(luò),在處理大規(guī)模圖像識(shí)別任務(wù)以及與機(jī)器學(xué)習(xí)類(lèi)似的其他問(wèn)題方面已大獲成功。在當(dāng)前案例中,針對(duì)在 FPGA 上實(shí)現(xiàn) CNN 做一個(gè)可行性研究

2019-06-19 07:24:41

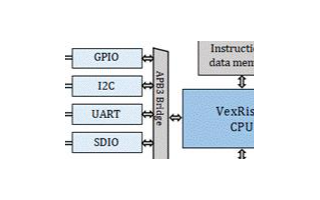

解決方案開(kāi)發(fā)者提供了極具吸引力的優(yōu)勢(shì)。圖11展示了一個(gè)實(shí)例,其中ECP5 FPGA用于實(shí)現(xiàn)推理加速器,對(duì)來(lái)自攝像頭的數(shù)據(jù)運(yùn)行預(yù)先訓(xùn)練好的卷積神經(jīng)網(wǎng)絡(luò)(CNN)進(jìn)行處理。運(yùn)行在FPGA上的CNN引擎識(shí)別

2020-10-21 11:53:02

FAST包處理器的核心功能是什么如何使用賽靈思FPGA加速包處理?

2021-04-30 06:32:20

NoC為FPGA設(shè)計(jì)提供了哪些優(yōu)勢(shì)?NoC在FPGA內(nèi)部邏輯互連中發(fā)揮的作用是什么?如何利用片上高速網(wǎng)絡(luò)創(chuàng)新地實(shí)現(xiàn)FPGA內(nèi)部超高帶寬邏輯互連?

2021-06-17 11:35:28

怎么實(shí)現(xiàn)基于FPGA設(shè)計(jì)安全的汽車(chē)通信網(wǎng)絡(luò)?

2021-05-17 06:23:54

,其算法的軟件實(shí)現(xiàn)方式非常低效,所以業(yè)界對(duì)GNN的硬件加速有著非常迫切的需求。我們知道傳統(tǒng)的CNN(卷積神經(jīng)網(wǎng)絡(luò)網(wǎng)絡(luò))硬件加速方案已經(jīng)有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究

2020-10-20 09:48:39

1、加速神經(jīng)網(wǎng)絡(luò)的必備開(kāi)源項(xiàng)目 到底純FPGA適不適合這種大型神經(jīng)網(wǎng)絡(luò)的設(shè)計(jì)?這個(gè)問(wèn)題其實(shí)我們不適合回答,但是FPGA廠商是的實(shí)際操作是很有權(quán)威性的,現(xiàn)在不論是Intel還是Xilinx都沒(méi)有在

2022-10-24 16:10:50

脈沖耦合神經(jīng)網(wǎng)絡(luò)(PCNN)在FPGA上的實(shí)現(xiàn),實(shí)現(xiàn)數(shù)據(jù)分類(lèi)功能,有報(bào)酬。QQ470345140.

2013-08-25 09:57:14

請(qǐng)問(wèn)一下fpga加速神經(jīng)網(wǎng)絡(luò)為什么要用arm核呢?用其他的不行嗎

2022-07-25 14:37:58

PCI Express是一種高性能互連協(xié)議,被廣泛應(yīng)用于網(wǎng)絡(luò)適配、圖形加速器、網(wǎng)絡(luò)存儲(chǔ)、大數(shù)據(jù)傳輸以及嵌入式系統(tǒng)等領(lǐng)域。文中介紹了PCIe的體系結(jié)構(gòu),以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

以太網(wǎng)線(xiàn)路接口卡模塊設(shè)計(jì)的重點(diǎn)之一,主要的功能是將各種標(biāo)準(zhǔn)的MAC幀數(shù)據(jù)格式轉(zhuǎn)換為網(wǎng)絡(luò)層統(tǒng)一的數(shù)據(jù)格式,為網(wǎng)絡(luò)層處理屏蔽掉底層物理接口。輸入處理FPGA采用Altera公司Stratix GX系列

2019-04-29 07:00:07

全球領(lǐng)先的中文互聯(lián)網(wǎng)搜索引擎提供商百度正在采用賽靈思FPGA加速其中國(guó)數(shù)據(jù)中心的機(jī)器學(xué)習(xí)應(yīng)用。兩家公司正合作進(jìn)一步擴(kuò)大FPGA加速平臺(tái)的部署規(guī)模。新興應(yīng)用的快速發(fā)展正日漸加重計(jì)算工作的負(fù)載,數(shù)據(jù)中心

2016-12-15 17:15:52

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-03-04 11:13:54

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-03-11 11:07:39

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-03-18 11:16:02

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-03-25 11:34:03

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-04-01 10:53:42

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-04-11 14:45:24

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-04-18 14:12:57

的高性能FPGA計(jì)算加速卡。作為基于服務(wù)器的PCI Express數(shù)據(jù)采集、處理、存儲(chǔ)設(shè)備,該板卡可以實(shí)現(xiàn)2通道萬(wàn)兆光纖網(wǎng)絡(luò)數(shù)據(jù)的高速采集、實(shí)時(shí)處理、實(shí)時(shí)記錄和寬帶回放,強(qiáng)大的FPGA處理性能,可以實(shí)現(xiàn)

2016-04-27 11:51:14

本文介紹了神經(jīng)網(wǎng)絡(luò)VLSI硬件實(shí)現(xiàn)的基本情況和VerilgHDL硬件設(shè)計(jì)方法的概念,在此基礎(chǔ)上利用FPGA設(shè)計(jì)出了Kohonen競(jìng)爭(zhēng)網(wǎng)絡(luò)硬件電路,其工作頻率為33Mhz,并對(duì)其工作過(guò)程進(jìn)行了較詳細(xì)的

2009-06-18 08:49:21 11

11 一種FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線(xiàn)結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探

2009-08-08 09:07:22 25

25 本文介紹了基于FPGA和MPC860架構(gòu)的網(wǎng)絡(luò)應(yīng)用硬件開(kāi)發(fā)平臺(tái)的設(shè)計(jì)原理及具體實(shí)現(xiàn),討論了其優(yōu)于網(wǎng)絡(luò)處理器的性能特點(diǎn),給出了利用該平臺(tái)進(jìn)行網(wǎng)絡(luò)應(yīng)用開(kāi)發(fā)的實(shí)例,并介紹了其在網(wǎng)

2010-03-02 16:28:24 13

13 本文闡述了用于FPGA的可優(yōu)化時(shí)鐘分配網(wǎng)絡(luò)功耗與面積的時(shí)鐘布線(xiàn)結(jié)構(gòu)模型。并在時(shí)鐘分配網(wǎng)絡(luò)中引入數(shù)字延遲鎖相環(huán)減少時(shí)鐘偏差,探討了FPGA時(shí)鐘網(wǎng)絡(luò)中鎖相環(huán)的實(shí)現(xiàn)方案。

2010-08-06 16:08:45 12

12 提出了模糊CMAC網(wǎng)絡(luò)的一種基于FPGA的硬件實(shí)現(xiàn)方法。首先,分析了模糊CMAC網(wǎng)絡(luò)的結(jié)構(gòu)與算法,并以MATLAB仿真為依據(jù),得到模糊CMAC網(wǎng)絡(luò)的FPGA實(shí)現(xiàn)所需的參數(shù);在此基礎(chǔ)上,對(duì)模糊CMAC

2010-08-09 14:55:03 19

19 提出了二維模糊CMAC網(wǎng)絡(luò)的一種基于FPGA的硬件實(shí)現(xiàn)方法。首先,分析了模糊CMAC網(wǎng)絡(luò)的結(jié)構(gòu)與算法,并以Matlab仿真為依據(jù),得到模糊CMAC網(wǎng)絡(luò)的FPGA實(shí)現(xiàn)所需的參數(shù);在此基礎(chǔ)上,對(duì)模糊CMAC網(wǎng)絡(luò)進(jìn)行硬件模塊劃分,基于VHDL實(shí)現(xiàn)了各硬件模塊的功能描述,并對(duì)模塊

2011-03-15 17:19:56 29

29 采用Spartan-6 FPGA加速紋理映射:這種要求嚴(yán)苛的圖形流程曾經(jīng)是定制ASIC內(nèi)核的應(yīng)用,而如今卻成為低成本FPGA的天下。 作為一種以 FPGA 為構(gòu)建基礎(chǔ),而非采用專(zhuān)業(yè)多媒體片上系統(tǒng)的手持

2012-10-08 13:57:33 4191

4191 2016年4月8日,中國(guó)北京—— All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司 (Xilinx, Inc. (NASDAQ:XLNX)) 與 IBM(NYSE: IBM)公司今天聯(lián)合宣布將通過(guò)SuperVesselOpenPOWER開(kāi)發(fā)云平臺(tái)實(shí)現(xiàn) FPGA加速。

2016-04-11 09:31:57 657

657 基于FPGA的侵徹加速度信號(hào)采集系統(tǒng)設(shè)計(jì)_董勝飛

2017-01-13 21:40:36 2

2 SuperVessel將包括賽靈思SDAccel開(kāi)發(fā)環(huán)境,支持用C、C++和OpenCL實(shí)現(xiàn)FPGA加速 All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司與IBM公司今天聯(lián)合宣布

2017-02-08 16:06:08 231

231 基于FPGA和DSP網(wǎng)絡(luò)單向時(shí)延測(cè)量系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)_唐旭

2017-03-19 11:38:26 0

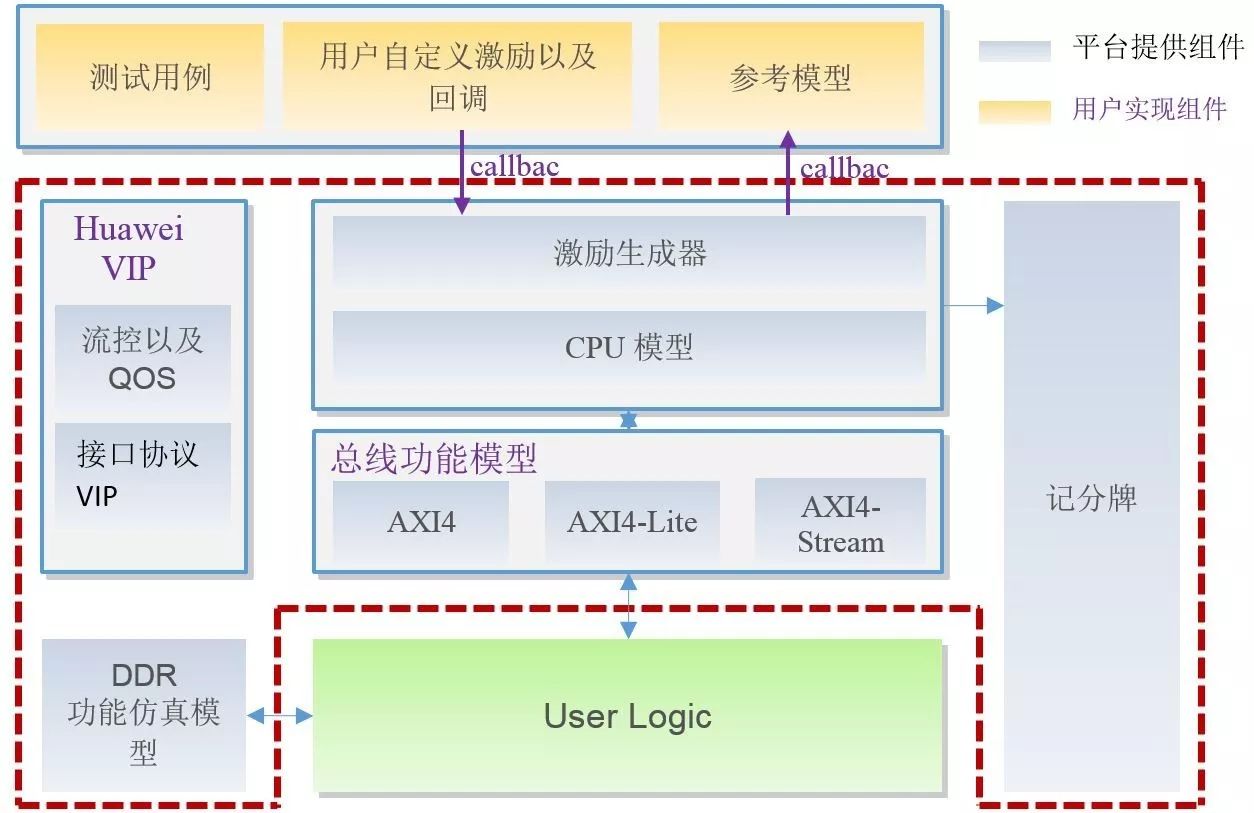

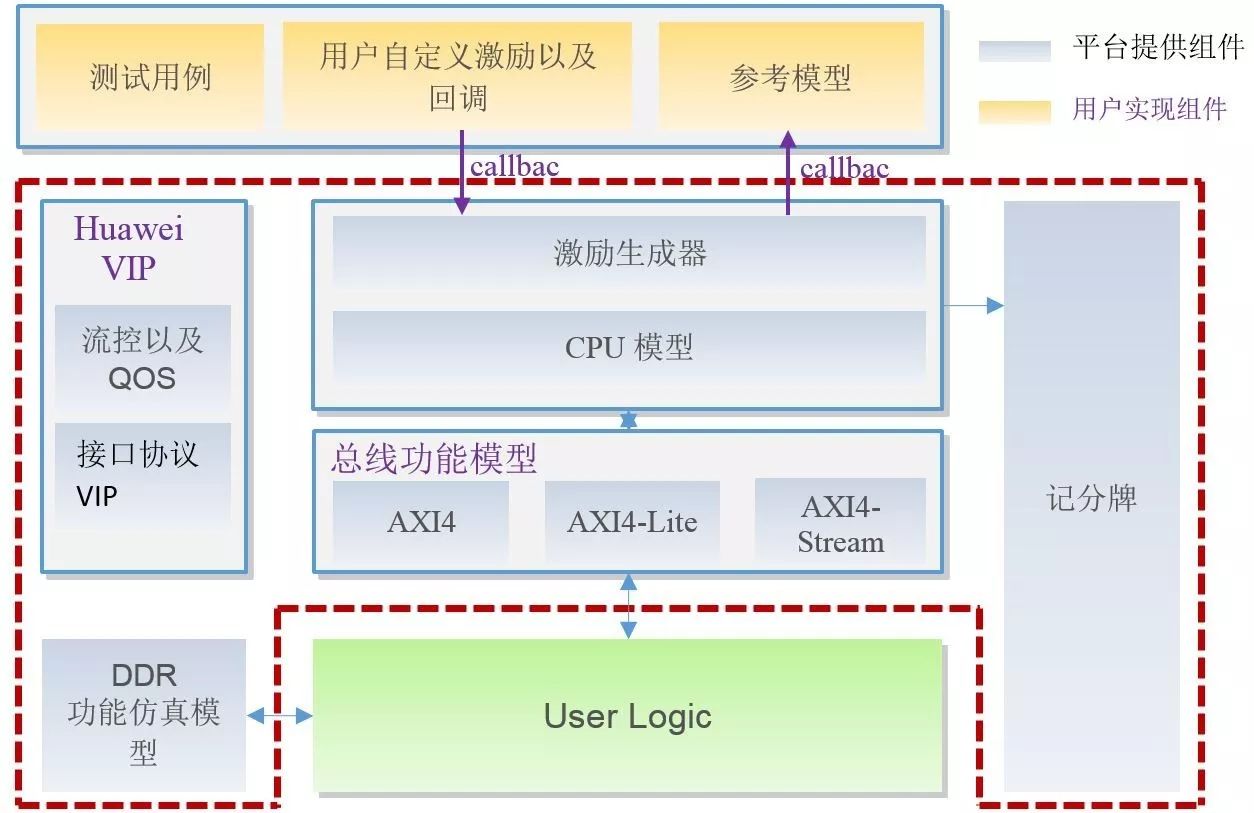

0 在數(shù)據(jù)中心引入 FPGA 并實(shí)現(xiàn)云化加速業(yè)務(wù)成為必然趨勢(shì)。隨著華為云 FPGA 加速服務(wù)的推出,打破原有 FPGA 開(kāi)發(fā)、測(cè)試和應(yīng)用存在的較高門(mén)檻,開(kāi)啟了一個(gè)顛覆 FPGA 開(kāi)發(fā)的新時(shí)代!

2017-10-10 10:49:17 4815

4815

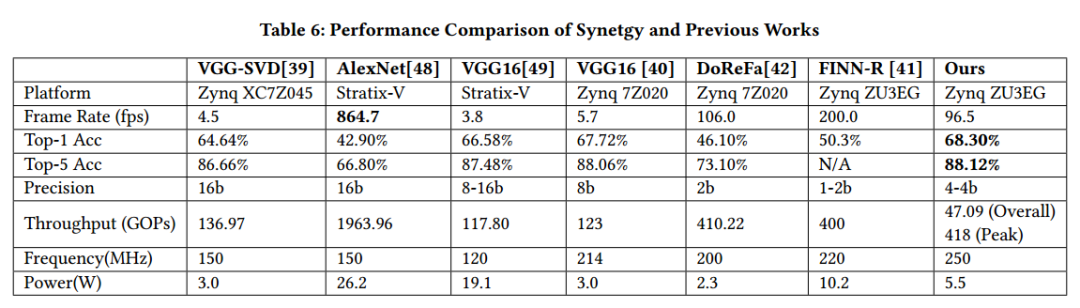

CNN已經(jīng)廣泛用于圖像識(shí)別,因?yàn)樗苣7律镆曈X(jué)神經(jīng)的行為獲得很高識(shí)別準(zhǔn)確率。最近,基于深度學(xué)習(xí)算法的現(xiàn)代應(yīng)用高速增長(zhǎng)進(jìn)一步改善了研究和實(shí)現(xiàn)。特別地,多種基于FPGA平臺(tái)的深度CNN加速器被提出

2017-11-17 13:31:01 7719

7719 實(shí)現(xiàn)成本低,但是在數(shù)據(jù)沖突較高時(shí)會(huì)導(dǎo)致查表性能急速下降;硬件TCAM方法具有優(yōu)良的時(shí)間特性,但其價(jià)格昂貴、耗能巨大。目前,隨著基于現(xiàn)場(chǎng)可編程門(mén)陣列FPGA的異構(gòu)計(jì)算技術(shù)的高速發(fā)展,利用系統(tǒng)已經(jīng)提供的FPGA資源對(duì)基于軟件實(shí)現(xiàn)的Hash表結(jié)構(gòu)進(jìn)行加速成

2017-11-27 14:46:24 0

0 剛好在知乎上看到這個(gè)問(wèn)題?如何用FPGA加速卷積神經(jīng)網(wǎng)絡(luò)CNN,恰巧我的碩士畢業(yè)設(shè)計(jì)做的就是在FPGA上實(shí)現(xiàn)CNN的架構(gòu),在此和大家分享。 先說(shuō)一下背景,這個(gè)項(xiàng)目的目標(biāo)硬件是Xilinx的PYNQ

2018-06-29 07:55:00 4555

4555

包含 FPGA 的英特爾至強(qiáng) CPU 的加速堆棧 一起,將使 FPGA 在數(shù)據(jù)中心的部署更簡(jiǎn)單更快速。輕松實(shí)現(xiàn) FPGA 加速。使用英特爾可編程加速卡(英特爾PAC),可以更快地完成 FPGA 加速

2018-05-18 06:31:00 2274

2274

在線(xiàn)路內(nèi)對(duì)沖場(chǎng)景下,來(lái)自以太網(wǎng)接口的流量將被傳遞至FPGA以實(shí)現(xiàn)網(wǎng)絡(luò)分流,而后被交付至ConnectX-5系統(tǒng)芯片處,最后才抵達(dá)主機(jī)。在旁觀配置下,流量則首先由該系統(tǒng)芯片處理,隨后主機(jī)加速工作負(fù)載流量被進(jìn)一步傳遞至FPGA處。

2018-07-12 08:38:00 5026

5026 Molex屬下Nallatech 公司近日推出用于高性能計(jì)算 (HPC)、網(wǎng)絡(luò)加速和數(shù)據(jù)分析的 FPGA 解決方案。使用低外形的 Nallatech 385A PCIe 加速卡,以及采用英特爾

2018-07-31 09:04:00 1615

1615 FPGA可編程加速卡(PAC)的一個(gè)重要應(yīng)用場(chǎng)合是減輕CPU的負(fù)擔(dān),把一些原來(lái)要在CPU上運(yùn)行的工作量轉(zhuǎn)移到FPGA的加速卡上,可用于從邊緣/智能設(shè)備到云的產(chǎn)品中(如圖1)。

2019-08-07 08:07:00 4270

4270 對(duì)于此次收購(gòu),賽靈思的解讀是賽靈思從FPGA器件向自適應(yīng)計(jì)算加速平臺(tái)提供商演變的戰(zhàn)略,就是要加速從云到端應(yīng)用上FPGA 加速技術(shù)的部署,經(jīng)深鑒科技優(yōu)化的神經(jīng)網(wǎng)絡(luò)剪枝技術(shù)運(yùn)行在賽靈思FPGA 器件

2018-11-12 10:59:10 1263

1263 在本演示中,來(lái)自IBM的Bruce Wile討論了新推出的CAPI SNAP框架,該框架支持FPGA加速。

“SNAP”框架是“存儲(chǔ),網(wǎng)絡(luò)和分析編程”的縮寫(xiě),可以在數(shù)據(jù)流動(dòng)時(shí)加速對(duì)數(shù)據(jù)的分析

2018-11-29 06:09:00 2981

2981 在本視頻中,Nimbix的首席技術(shù)官Leo Reiter討論了使用SDAccel開(kāi)發(fā)環(huán)境和Xilinx FPGA卡在Nimbix云加速工作流中實(shí)現(xiàn)FPGA開(kāi)發(fā)和運(yùn)行時(shí)間的民主化。

觀看此視頻,了解如何開(kāi)始使用wi

2018-11-29 06:06:00 1655

1655 和網(wǎng)絡(luò)加速應(yīng)用而設(shè)計(jì)的,并基于Speedster22i FPGA系列相同的高性能架構(gòu),采用Speedcore作為硬件加速器的方案被廣泛應(yīng)用到數(shù)據(jù)中心和通信基礎(chǔ)設(shè)施等領(lǐng)域。據(jù)了解,eFPGA IP授權(quán)業(yè)務(wù)

2018-12-23 16:29:40 4161

4161 網(wǎng)上對(duì)于FPGACNN加速的研究已經(jīng)很多了,神經(jīng)網(wǎng)絡(luò)的硬件加速似乎已經(jīng)滿(mǎn)大街都是了,這里我們暫且不討論誰(shuí)做的好誰(shuí)做的不好,我們只是根據(jù)許許多多的經(jīng)驗(yàn)來(lái)總結(jié)一下實(shí)現(xiàn)硬件加速,需要哪些知識(shí),考慮哪些因素。

2019-02-14 14:25:46 1225

1225 網(wǎng)上對(duì)于FPGACNN加速的研究已經(jīng)很多了,神經(jīng)網(wǎng)絡(luò)的硬件加速似乎已經(jīng)滿(mǎn)大街都是了,這里我們暫且不討論誰(shuí)做的好誰(shuí)做的不好,我們只是根據(jù)許許多多的經(jīng)驗(yàn)來(lái)總結(jié)一下實(shí)現(xiàn)硬件加速,需要哪些知識(shí),考慮哪些因素。

2019-03-08 14:44:33 3614

3614 近日,百度云與聯(lián)捷計(jì)算科技(CTAccel)共同推出基于FPGA的圖像加速解決方案(CIP,CTAccel Image Processor),實(shí)現(xiàn)對(duì)JPEG轉(zhuǎn)碼JPEG、JPEG轉(zhuǎn)碼WebP(M6)等進(jìn)行FPGA加速的功能,聚焦社交平臺(tái)、新聞網(wǎng)站、電商、云相冊(cè)等場(chǎng)景。

2019-06-18 14:35:55 1485

1485 通常提到FPGA,首先想到的是一款可編程的硬件產(chǎn)品,無(wú)論是用在嵌入式設(shè)備上,還是用在網(wǎng)絡(luò)傳輸加速方面,與軟件似乎都沒(méi)有太多的直接聯(lián)系。

2019-06-24 17:45:01 1952

1952

在2019年MWC大會(huì)的第一天,英特爾又推出了一款針對(duì)5G應(yīng)用的FPGA加速卡PAC N3000。這款加速卡可以實(shí)現(xiàn)高達(dá)100Gbps的網(wǎng)絡(luò)流量的加速處理,同時(shí)支持9GB DDR4和144MB QDR IV板上內(nèi)存。

2019-08-12 17:51:44 1141

1141 Achronix半導(dǎo)體公司與Mo-lex旗下FPGA加速器產(chǎn)品供應(yīng)商BittWare聯(lián)合推出全新的、面向高性能計(jì)算和數(shù)據(jù)加速應(yīng)用的FPGA加速卡,可實(shí)現(xiàn)云計(jì)算與邊緣計(jì)算加速,助力高帶寬應(yīng)用。

2019-11-08 15:07:23 569

569 FPGA加速卡采用CAPI接口設(shè)計(jì),通過(guò)CAPI接口與P&P服務(wù)器緊密集成;應(yīng)用于大數(shù)據(jù)分析、密碼解算、圖像圖片處理等領(lǐng)域,實(shí)現(xiàn)百倍的加速比;

2020-07-07 16:16:12 16

16 PipeCNN可實(shí)現(xiàn)性 PipeCNN論文解析:用OpenCL實(shí)現(xiàn)FPGA上的大型卷積網(wǎng)絡(luò)加速 2.1 已實(shí)現(xiàn)的PipeCNN資源消耗 3. 實(shí)現(xiàn)大型神經(jīng)網(wǎng)絡(luò)的方法 4. Virtex-7高端FPGA概覽

2021-04-19 11:12:02 2223

2223

基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)說(shuō)明。

2021-04-28 11:24:23 25

25 了一種基于FPGA的SIM卷積神經(jīng)網(wǎng)絡(luò)加速器架構(gòu)。以YOOV2目標(biāo)檢測(cè)算法為例,介紹了將卷積神經(jīng)網(wǎng)絡(luò)模型映射到FPGA上的完整流程;對(duì)加速器的性能和資源耗費(fèi)進(jìn)行深λ分析和建模,將實(shí)際傳輸延時(shí)考慮在內(nèi),縮小了加速器理論時(shí)延與實(shí)際時(shí)延

2021-05-28 14:00:22 23

23 基于FPGA的神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)方法說(shuō)明。

2021-06-01 09:35:16 37

37 BittWare 在之前發(fā)布的 IA-840F 企業(yè)級(jí) FPGA 加速器中添加了兩款基于英特爾 Agilex FPGA 和 SoC FPGA 的新加速器產(chǎn)品(詳見(jiàn)此前報(bào)道)。 全新的 IA-420F

2021-06-30 10:48:07 2111

2111 電子學(xué)報(bào)第七期《一種可配置的CNN協(xié)加速器的FPGA實(shí)現(xiàn)方法》

2021-11-18 16:31:06 15

15 新技術(shù)星期二:加速 FPGA 計(jì)算的 2 張卡

2022-12-30 09:40:20 555

555 本文詳細(xì)描述了FPGA實(shí)現(xiàn)圖像去霧的實(shí)現(xiàn)設(shè)計(jì)方案,采用暗通道先驗(yàn)算法實(shí)現(xiàn),并利用verilog并行執(zhí)行的特點(diǎn)對(duì)算法進(jìn)行了加速;

2023-06-05 17:01:45 879

879

推理、深度學(xué)習(xí)、數(shù)據(jù)采集、高頻交易、網(wǎng)絡(luò)信號(hào)處理、視頻圖像處理等多個(gè)領(lǐng)域,可為用戶(hù)提供高能效比的加速解決方案。產(chǎn)品規(guī)格中科億海微“億迅”系列FPGA加速卡,支持PC

2022-07-20 18:04:57 587

587

電子發(fā)燒友網(wǎng)站提供《FPGA加速神經(jīng)網(wǎng)絡(luò)的矩陣乘法.pdf》資料免費(fèi)下載

2023-09-15 14:50:36 0

0 電子發(fā)燒友網(wǎng)站提供《基于FPGA的加速基礎(chǔ)知識(shí).pdf》資料免費(fèi)下載

2023-09-18 10:12:20 0

0 電子發(fā)燒友網(wǎng)站提供《基于單片機(jī)和FPGA的網(wǎng)絡(luò)數(shù)據(jù)加密實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-18 09:48:25 0

0 電子發(fā)燒友網(wǎng)站提供《基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)的硬件實(shí)現(xiàn).pdf》資料免費(fèi)下載

2023-10-23 10:21:25 0

0 加速FPGA選擇和系統(tǒng)設(shè)計(jì)的架構(gòu)探索

2022-12-30 09:21:10 3

3 任務(wù)是將邏輯元件與連接線(xiàn)路進(jìn)行合理的布局和布線(xiàn),以實(shí)現(xiàn)性能優(yōu)化和電路連接的可靠性。然而,FPGA布局布線(xiàn)的過(guò)程通常是一項(xiàng)繁瑣且耗時(shí)的任務(wù),因此加速布局布線(xiàn)算法的研究具有重要意義。本文將詳盡探討FPGA布局布線(xiàn)算法加速的方法與技術(shù),分析其理論基礎(chǔ)和實(shí)踐應(yīng)用。 FPGA布局布

2023-12-20 09:55:13 249

249 到底純FPGA適不適合這種大型神經(jīng)網(wǎng)絡(luò)的設(shè)計(jì)?這個(gè)問(wèn)題其實(shí)我們不適合回答,但是FPGA廠商是的實(shí)際操作是很有權(quán)威性的,現(xiàn)在不論是Intel還是Xilinx都沒(méi)有在自己傳統(tǒng)的FPGA上推廣AI,都是

2024-01-24 09:51:33 425

425

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論