1、前言

本文詳細描述了FPGA實現圖像去霧的實現設計方案,采用暗通道先驗算法實現,并利用verilog并行執行的特點對算法進行了加速;

本設計以HDMI或者ov5640攝像頭作為輸入,經過圖像去霧算法去霧,再經過圖像緩存后輸出顯示器,以驗證圖像去霧算法在FPGA中加速的正確性;

工程代碼編譯通過后上板調試驗證,文章末尾有演示視頻,可直接項目移植,適用于在校學生、研究生,也適用于在職工程師做項目開發,可應用于醫療、軍工等行業的數字成像和圖像傳輸領域;

提供完整的、跑通的工程源碼和技術支持;

工程源碼和技術支持的獲取方式放在了文章末尾,請耐心看到最后。

2、目前我這里已有的圖像處理方案

目前我這里已有的圖像處理方案有很多,包括圖像縮放、圖像拼接、圖像旋轉、圖像識別跟蹤、圖像去霧等等

3、暗通道先驗算法介紹

4、本圖像去霧模塊的優缺點

優點1:純verilog代碼實現,無任何IP,可在xilinx、altera、國產FPGA等平臺間自由移植;

優點2:算法加速,利用了FPGA并行計算的特點;

優點3:提供了2套工程源碼,對接不同的視頻輸入接口;

缺點1:算法還不夠完美,去霧效果也不完美,個人覺得;待我優化;

缺點2:用于驗證、學習、課題等可以,做實際產品還不理想;

缺點3:對輸入的圖像要求稍微有點高,那種色差太過嚴重的去霧效果不好。

5、vivado工程詳解

工程代碼設計架構如下:

輸入:

提供2套工程源碼,一套以HDMI作為視頻輸入源,另一套以ov5640攝像頭視頻輸入源;HDMI輸入分辨率為1920x1080@60Hz;ov5640攝像頭輸入分辨率為1280x720@30Hz;

HDMI接收和發送采用silicon9011和silicon9134芯片驅動,silicon9011和silicon9134芯片需要i2c配置才能使用

暗通道先驗-圖像去霧:

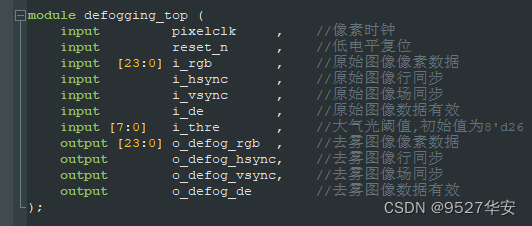

由3個模塊順序執行,3個模塊內部并行執行,實現了FPGA加速算法的目的,分別由求RGB最小值和求折射率以及圖像去霧組成;

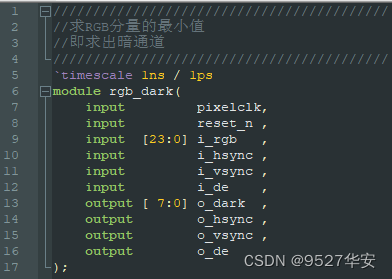

求RGB最小值的目的是實時的比較求出每個像素點RGB分量的最小值,也就是暗通道,該模塊頂層接口如下:

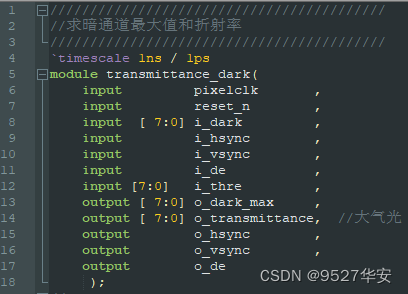

求折射率的目的是輸出暗通道最大值和折射率,該模塊頂層接口如下:

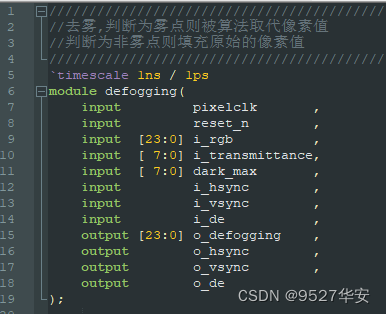

圖像去霧的目的是輸出暗通道最大值和折射率,該模塊頂層接口如下:

三個模塊整合封裝后的圖像去霧模塊接口如下:

FDMA圖像緩存:

串口解析:

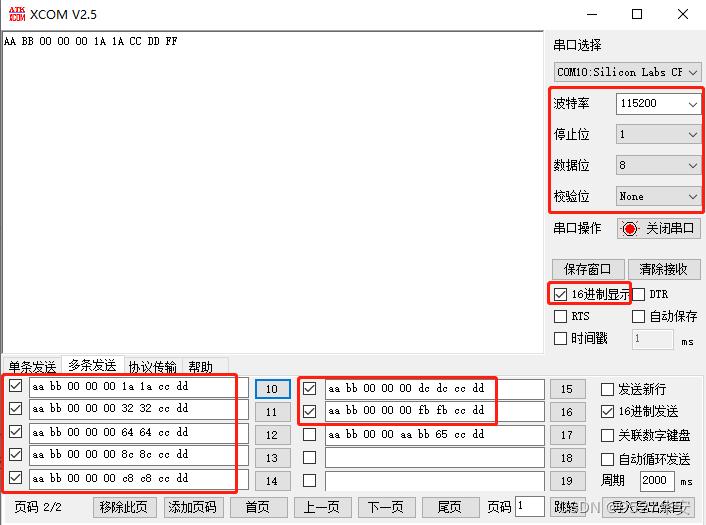

串口解析模塊的作用是用電腦發送命令控制圖像去霧模塊的輸入閾值,這個閾值的初始值為十進制26,如果你在使用過程中覺得圖像去霧效果不好,可以將這個閾值調大或者調小,我這里通過串口調試助手設置了多種閾值進行調整,如下:

比如要發送閾值為26,則發送控制命令如下:

aa bb 00 00 00 1a 1a cc dd;

要發送閾值為251,則發送控制命令如下:

aa bb 00 00 00 fb fb cc dd;

vivado工程1詳解

開發板FPGA:Xilinx xc7a35tfgg484-2

開發環境:vivado2019.1;

輸入:HDMI-1920x1080@60Hz;

輸出:HDMI-1920x1080@60Hz;

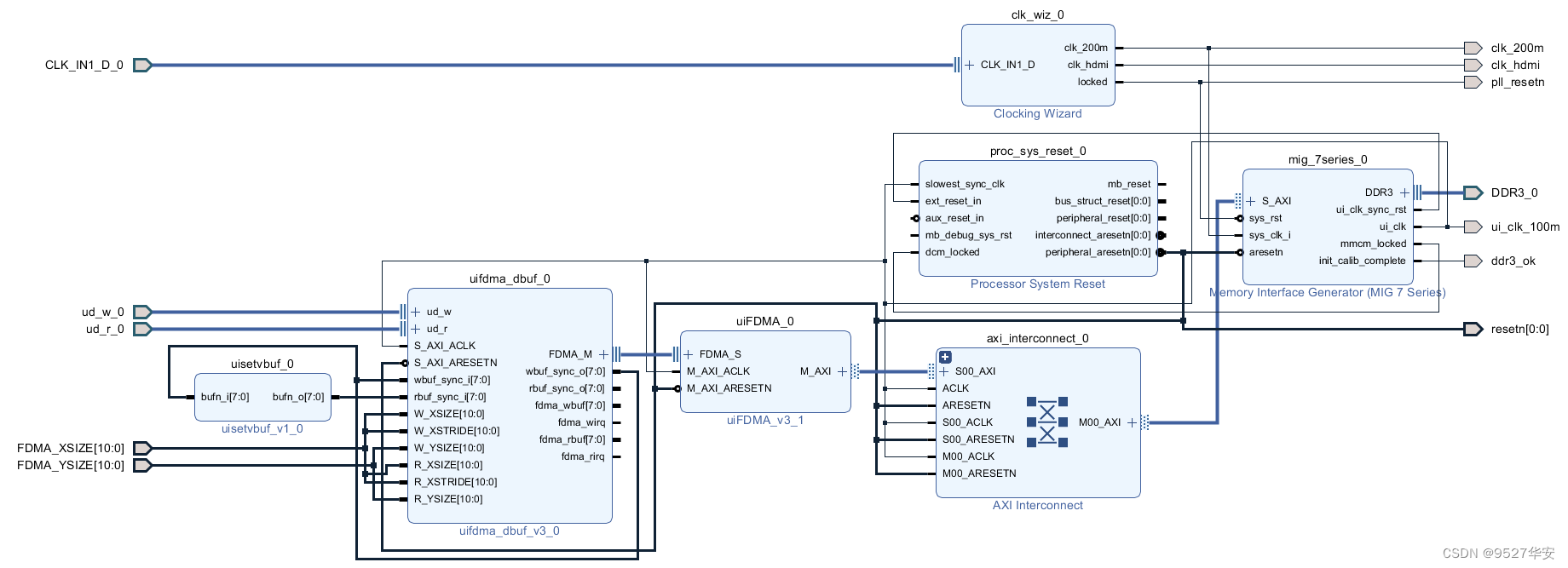

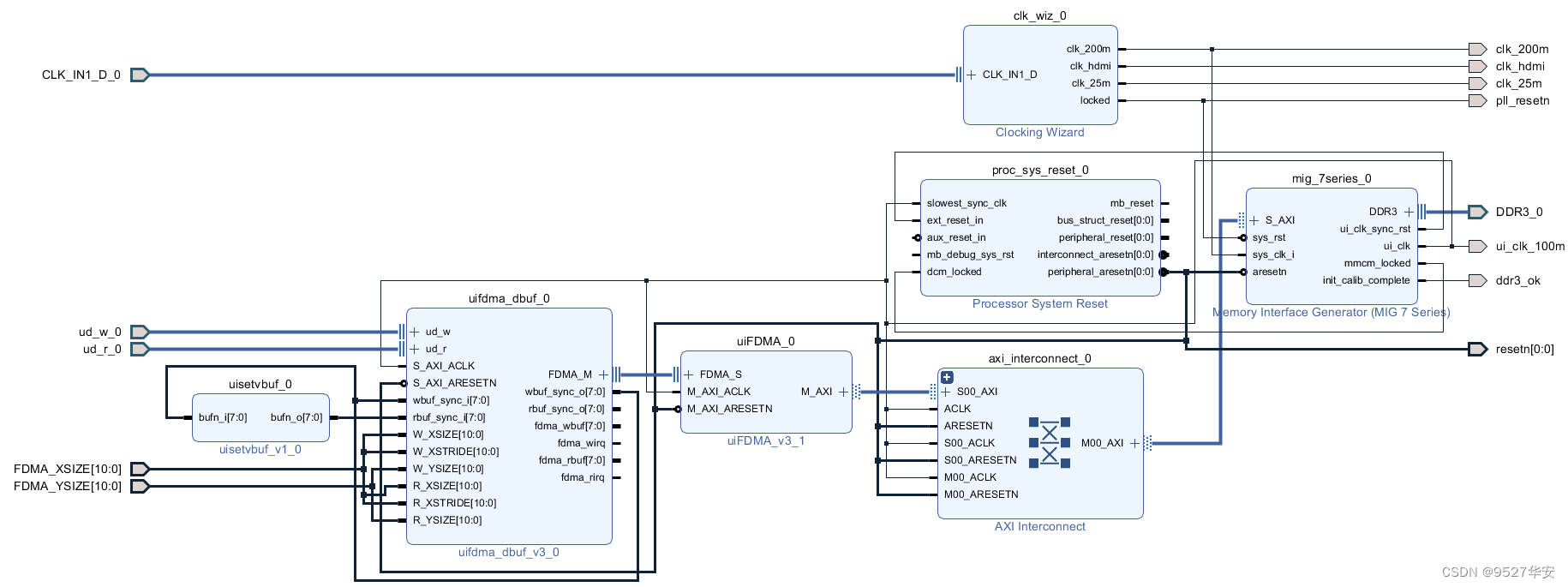

工程Block Design如下:

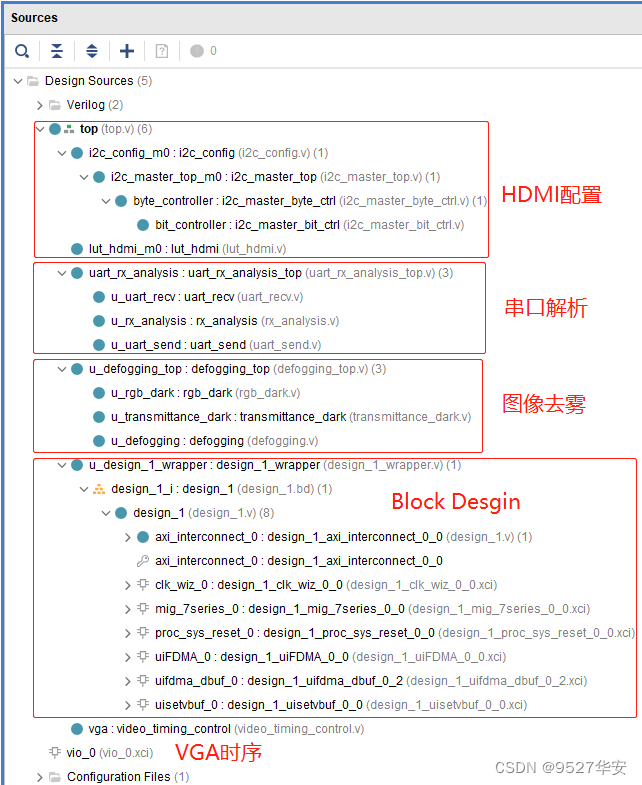

工程代碼架構如下:

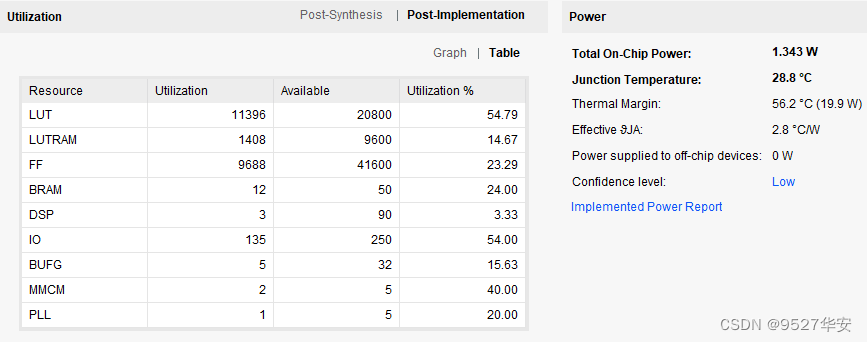

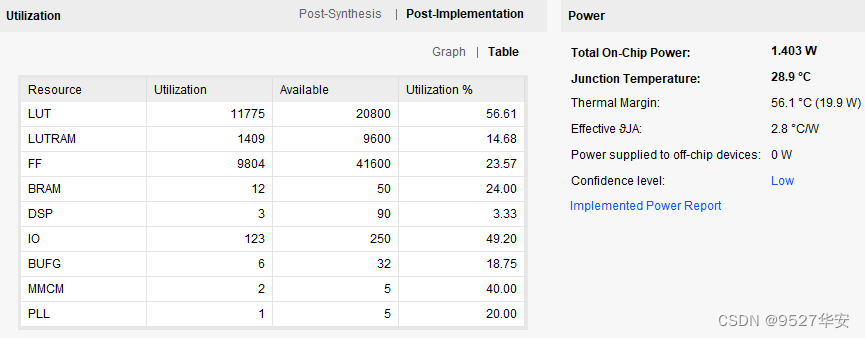

FPGA資源消耗和功耗預估如下:

vivado工程2詳解

開發板FPGA:Xilinx xc7a35tfgg484-2

開發環境:vivado2019.1;

輸入:ov5640攝像頭-1280x720@30Hz;

輸出:HDMI-1920x1080@60Hz;

工程Block Design如下:

工程代碼架構如下:

FPGA資源消耗和功耗預估如下:

電子發燒友App

電子發燒友App

評論