王琦,華為公司2012實驗室

高雪松,華為云IaaS服務(wù)產(chǎn)品部

FPGA 開發(fā)日益走向高層次綜合型,從門級、開關(guān)級到 RTL 級再到算法及未來再到系統(tǒng)級,而在應(yīng)用層面,由于 FPGA 有天生的并行處理機制,在人工智能、大數(shù)據(jù)處理方面無器件能出其右 。因此,在數(shù)據(jù)中心引入 FPGA 并實現(xiàn)云化加速業(yè)務(wù)成為必然趨勢。隨著華為云 FPGA 加速服務(wù)的推出,打破原有 FPGA 開發(fā)、測試和應(yīng)用存在的較高門檻,開啟了一個顛覆 FPGA 開發(fā)的新時代!

華為 FPGA 加速云服務(wù)——更懂您設(shè)計習(xí)慣的開發(fā)套件

華為在FPGA領(lǐng)域深耕多年,有著全球最專業(yè)的FPGA開發(fā)團隊,積累了大量FPGA開發(fā)經(jīng)驗和IP,這些積累結(jié)合其領(lǐng)先的彈性云服務(wù)架構(gòu),可以為用戶提供簡單易用的FPGA云服務(wù)。 總結(jié)起來,華為FPGA云加速服務(wù)優(yōu)勢體現(xiàn)在以下技術(shù)方面:

傳統(tǒng)FPGA開發(fā)方式以RTL語言開發(fā)為主,在云時代,用FPGA快速進行算法驗證,讓軟件工程師也能快速使用FPGA等需要,促進了使用OpenCL和C/C++等高級語言開發(fā)FPGA的需求。華為FPGA加速云服務(wù)開發(fā)套件提供了HDL、SDAccel和C/C++等多種語言開發(fā)環(huán)境,用戶可以選擇最熟悉和擅長的環(huán)境完成業(yè)務(wù)的設(shè)計開發(fā)。

華為積累的大量高質(zhì)高效常用FPGA設(shè)計組件,例如器件無關(guān)乎的ram,字節(jié)級和幀級的通用fifo,高效的支持絕對優(yōu)先級SP、公平輪詢RR、權(quán)重輪詢WRR等多種調(diào)度組件,多通道的DDR控制器,帶PFC等功能100G Eth接口控制器,通用矩陣運算、傅里葉變換等各種組件,用于可以直接調(diào)用這些設(shè)計組件,從而提升FPGA開發(fā)效率。在加速IP方面,華為積累了網(wǎng)絡(luò)轉(zhuǎn)發(fā)、網(wǎng)絡(luò)協(xié)議、安全加解密、壓縮解壓縮、AI、媒體、大數(shù)據(jù)、數(shù)據(jù)庫等覆蓋CT和IT各領(lǐng)域的通用加速 IP,通過華為IP marketplace,用戶可以快速的調(diào)用這些IP,從而快速構(gòu)建自己的加速應(yīng)用。

shell邏輯提供了PCIe接口、DDR控制、DMA引擎、Flash控制器等基本功能。憑借在CT領(lǐng)域高質(zhì)量和高性能需求場景的多年積累,華為可以提供業(yè)界領(lǐng)先的高性能和us級低時延的自研shell,滿足您高性能低時延的應(yīng)用場景;也同時提供高靈活性和低開發(fā)門檻的SDAccel shell,方便您移植基于GPU等平臺的應(yīng)用,快速地上線FPGA加速的業(yè)務(wù)。

華為FPGA加速云服務(wù)也提供了一系列的開發(fā)套件,支持用戶一鍵式創(chuàng)建用戶目錄,快速地構(gòu)建工程。

無需掌握TCL或者SHELL腳本語言,無需修改構(gòu)建腳本,只需要簡單修改配置參數(shù),開發(fā)套件即會自動生成約束文件及綜合編譯腳本,使用戶的開發(fā)更簡單。

用戶可以選擇單步執(zhí)行綜合、實現(xiàn)、PR校驗、目標文件生成及加密操作,也可以通過套件一鍵式完成工程構(gòu)建,生成自己的加速IP。

工程構(gòu)建套件提供了時序自動檢測功能和定時構(gòu)建等功能。用戶可以預(yù)約任意時間進行工程構(gòu)建。工程構(gòu)建完成后,用戶無需打開log查看構(gòu)建結(jié)果,套件會自動檢查用戶時序,以直觀的方式通知您設(shè)計的時序情況。

華為 FPGA 加速云服務(wù)——簡單易用的全流程驗證

FPGA開發(fā)過程中,仿真是保證FPGA產(chǎn)品質(zhì)量最重要且難度最大的環(huán)節(jié),具體的:

(1)傳統(tǒng)FPGA開發(fā)方式中仿真平臺搭建需要大量驗證工程師投入,難度大,導(dǎo)致驗證人員無法專注于驗證邏輯功能;

(2)驗證專用IP開發(fā)難度高,如果購買第三方VIP價格昂貴,使得用戶難以保障功能的穩(wěn)定性;

(3)使用驗證平臺進行驗證門檻高,如果驗證基礎(chǔ)薄弱,很難駕馭,不利于驗證工作的開展。

華為FPGA加速云驗證平臺采用業(yè)界通用的systemverilog2012語言開發(fā),由具有豐富驗證經(jīng)驗的團隊維護和升級。不僅提供簡易的端到端的流程指導(dǎo),還提供豐富的驗證IP(VIP),滿足用戶的各種需求。

相對業(yè)界其他FPGA云開發(fā)平臺,華為除了提供通用仿真平臺,還提供增強版仿真平臺以滿足更專業(yè)的用戶需求。增強版仿真平臺采用業(yè)界成熟的UVM方法學(xué),提供比通用版更多的特性以及更強的性能。

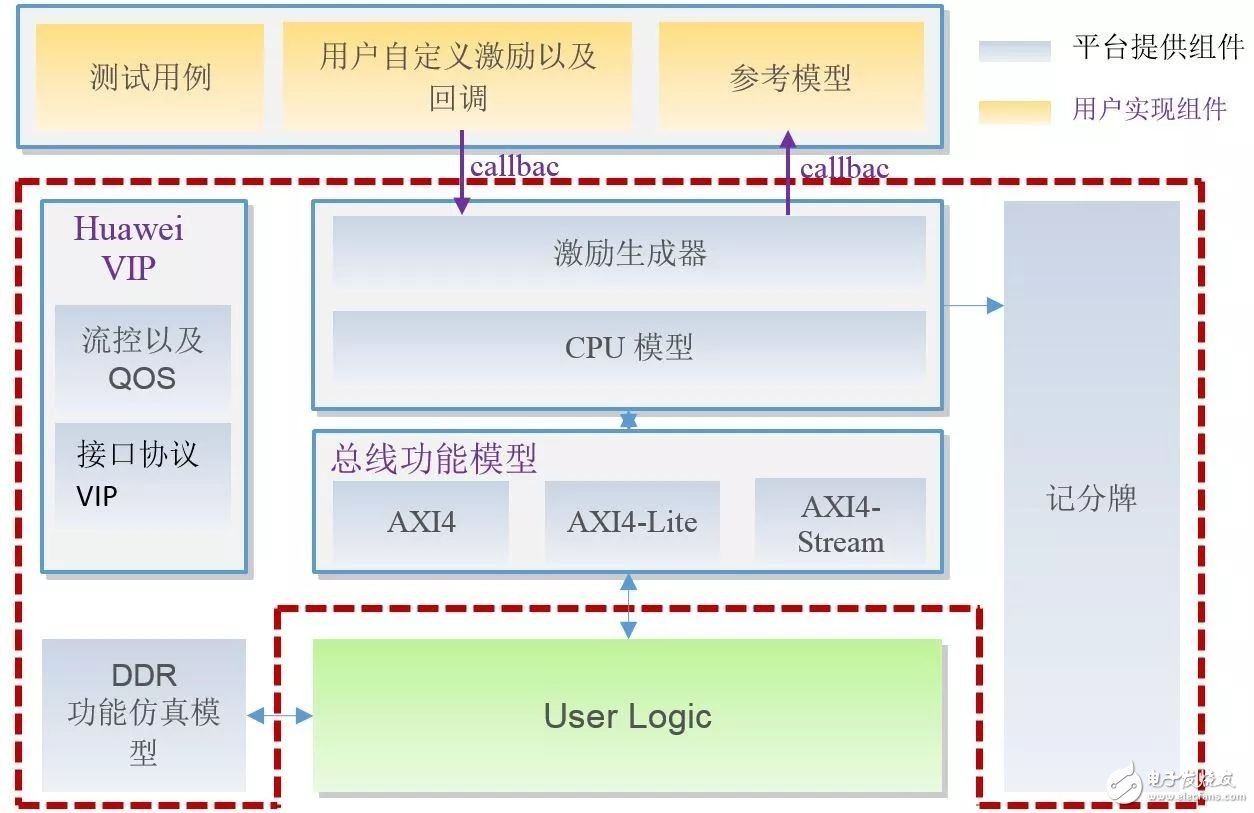

驗證平臺采用Testbench與Testcase完全分離的架構(gòu),即用戶可在完全不改變仿真平臺的前提下增刪并執(zhí)行測試用例。Testbench中包含基礎(chǔ)激勵組件、AXI4接口的BFM、CPU模型、DDR功能仿真模型、記分牌以及VIP。其中用戶可自定義部分通過用戶激勵組件、callback、rm等動態(tài)重配到testbench中而完全無需修改testbench。

針對使用云上加速資源的用戶,華為FPGA加速云服務(wù)為用戶提供完整的Testbench,用戶只需要設(shè)計自己的激勵組件、參考模型然后即可進行仿真測試,而無需關(guān)注接口時序,平臺連接、腳本實現(xiàn)等繁雜事務(wù),極大的提高了用戶的仿真驗證效率。

用戶可通過華為FPGA加速云服務(wù)提供的覆蓋率報告以及回歸腳本等工具對測試的覆蓋情況進行統(tǒng)計和閉環(huán)。

華為FPGA加速云服務(wù)平臺針對用戶仿真速度慢的問題,通過預(yù)編譯仿真庫以及一次編譯多次執(zhí)行的方法,大幅提高用戶的仿真速度。

華為也將提供豐富的VIP(驗證IP)庫,包含自己信息領(lǐng)域多年積累的高效能VIP,此類VIP將覆蓋總線接口,外掛存儲,網(wǎng)絡(luò)處理,高速接口等,用戶可以通過華為云IP MarketPlace快速的選擇及使用。

華為 FPGA 加速云服務(wù)——簡約而不簡單的驗證平臺

驗證平臺是驗證環(huán)節(jié)最重要的組件之一,傳統(tǒng)FPGA開發(fā)方式不僅需要投入大量人力搭建驗證平臺,而且如果需要完成復(fù)雜的測試往往會導(dǎo)致驗證平臺過于復(fù)雜,對非熟練用戶不友好,不易上手。

華為云驗證平臺不僅擁有強大的功能與擴展性,而且結(jié)構(gòu)簡單,易于新手使用,簡約而不簡單。

如圖1所示,Testbench中包含AXI4接口的BFM、DDR仿真模型、記分牌等組件。用戶如需使用Testbench僅需編寫自己的測試用例、激勵以及參考模型等功能而完全無需關(guān)注BFM、組件連接,最大程度上簡化用戶的驗證工作。華為的通用仿真平臺還支持代碼與功能覆蓋率的收集、斷言和C混合編程等高級仿真方法。

圖1 華為FPGA加速云驗證平臺架構(gòu)圖

華為 FPGA 加速云服務(wù)——志當存高遠,新模式,更高效,創(chuàng)未來

華為FPGA加速云服務(wù)開啟了一種新的FPGA開發(fā)模式,隨著華為云MarketPlace的推出,未來FPGA開發(fā)業(yè)者可以在任何時間和地點專注開發(fā)屬于自己的IP,并將其出售;同時,華為FPGA加速云服務(wù)還開啟了共享智慧,這將再次顛覆FPGA開發(fā)模式,如果你是FPGA專家,你完全可以在家通過華為云開始屬于自己的事業(yè)!

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605167 -

華為

+關(guān)注

關(guān)注

216文章

34530瀏覽量

252589

原文標題:華為 FPGA 加速云服務(wù)顛覆傳統(tǒng) FPGA 開發(fā)

文章出處:【微信號:xilinx_inc,微信公眾號:賽靈思】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

英特爾FPGA 支持阿里云的加速即服務(wù)

FPGA/CPLD與單片機相比有哪些優(yōu)勢?

FPGA較傳統(tǒng)CPU強在哪里?

FPGA是如何實現(xiàn)30倍速度的云加速的?都加速了哪些東西?

【FPGA-F3】阿里云FAAS平臺,極大簡化FPGA開發(fā)部署流程

華為FPGA加速云服務(wù)器如何加速讓硬件應(yīng)用高效上云?

與傳統(tǒng)模式的芯片設(shè)計進行對比FPGA芯片有哪些優(yōu)勢

ARM硬核的引入相比傳統(tǒng)FPGA是否會降低zynq的性價比和靈活度呢

zynq這種FPGA器件相對以往傳統(tǒng)FPGA有哪些優(yōu)勢和劣勢

Xilinx與IBM通過SuperVesselOpenPOWER開發(fā)云平臺實現(xiàn)FPGA加速

Xilinx 助力華為加速云服務(wù)器

一站式FPGA基礎(chǔ)設(shè)施服務(wù)詳情-FPGA加速云服務(wù)器亮相華為歐洲生態(tài)大會

華為做了什么讓傳統(tǒng)FPGA開發(fā)被顛覆

華為 FPGA 加速云服務(wù)與傳統(tǒng) FPGA 開發(fā)相比有哪些優(yōu)勢?

華為 FPGA 加速云服務(wù)與傳統(tǒng) FPGA 開發(fā)相比有哪些優(yōu)勢?

評論