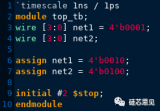

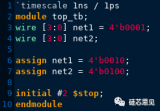

在Verilog和SystemVerilog中經常需要在使用變量或者線網之前,期望變量和線網有對應的初始值

2023-08-25 09:47:56 264

264

SystemVerilog 的VMM 驗證方法學教程教材包含大量經典的VMM源代碼,可以實際操作練習的例子,更是ic從業人員的絕佳學習資料。SystemVerilog 的VMM 驗證方法學教程教材[hide][/hide]

2012-01-11 11:21:38

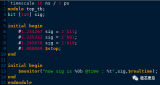

在SystemVerilog中,輸出信息顯示時間時,經常會在輸出信息格式中指定“%t”格式符,一般情況下“%t”輸出的格式都是固定的,但是這樣固定的輸出顯示的時間可能有時會讓用戶看起來感覺比較詫異,例如下面的示例。

2023-08-16 09:41:58 297

297

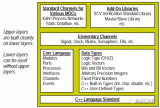

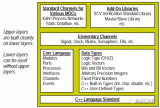

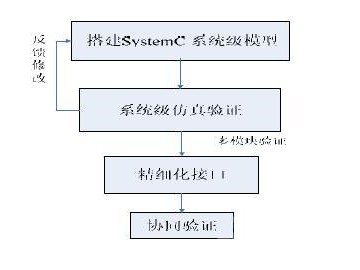

SystemC是基于C++的系統級設計語言,兼具描述硬件電路模型和面向對象的抽象能力。

2023-08-07 09:43:45 306

306

SystemVeirlog的全面支持是開發商用仿真器的第一道門檻。市面上可以找到不少基于純Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可數。如何全面地支持SystemVerilog語言,是開發仿真器的一個重要任務。

2023-07-14 15:15:25 191

191

本文講一下SystemVerilog的time slot里的regions以及events的調度。SystemVerilog語言是根據離散事件執行模型定義的,由events驅動。

2023-07-12 11:20:32 471

471

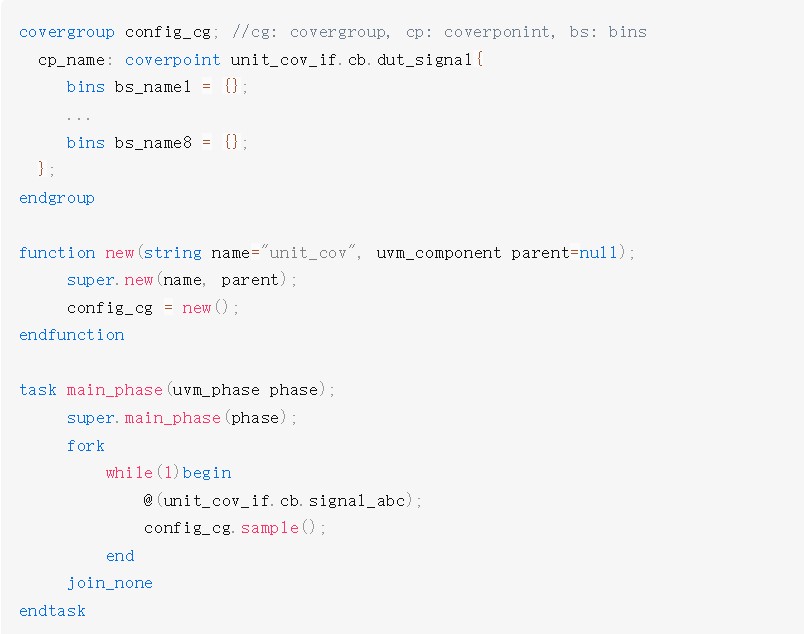

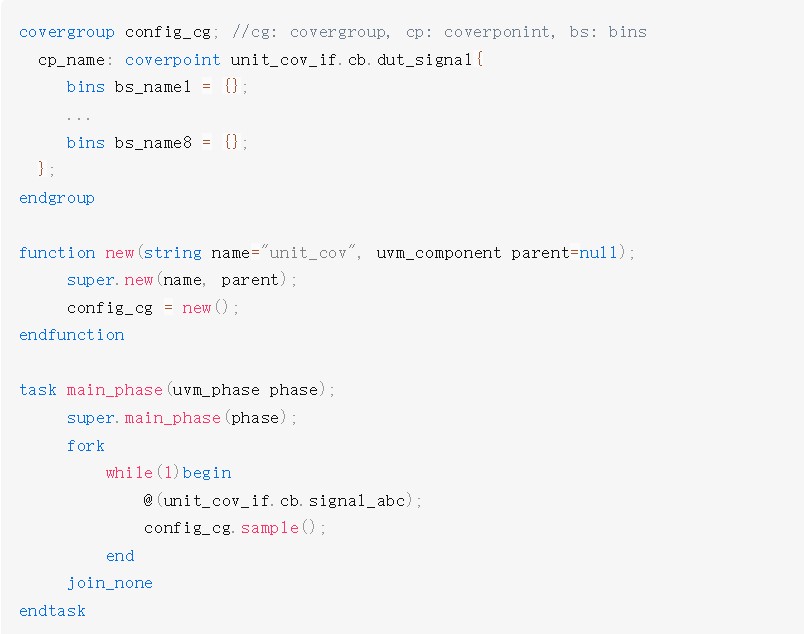

為了確保驗證的完備性,我們需要量化驗證目標。SystemVerilog提供了一套豐富的覆蓋率建模方式。

2023-06-25 10:44:16 294

294 在systemverilog中,net用于對電路中連線進行建模,driving strength(驅動強度)可以讓net變量值的建模更加精確。

2023-06-14 15:50:16 434

434

在SystemVerilog中,我們知道可以使用動態數組實現數組元素個數的動態分配,即隨用隨分

2023-06-09 09:46:24 1541

1541

SystemVerilog是一名芯片驗證工程師,必須掌握的一門語言,其中Function Coverage是必須要懂的知識點之一;

2023-06-04 16:30:24 1891

1891

我們在工作中常常會針對數組施加各式的約束,下面列舉一下有趣的**Systemverilog數組約束**示例

2023-05-30 11:13:21 243

243 寫過Verilog和systemverilog的人肯定都用過系統自定義的函數$display,這是預定好的,可以直接調用的功能。

2023-05-16 09:27:02 382

382

SystemVerilog Interface是modport的一種,但比簡單的輸入、輸出或輸入輸出端口的功能更多。

2023-04-28 14:12:22 1225

1225

SystemVerilog Interface是modport的一種,但比簡單的輸入、輸出或輸入輸出端口的功能更多。

2023-04-28 14:10:06 740

740

數獨是一種非常流行的游戲,數獨本質上也是一個約束問題,所以我們可以讓SystemVerilog的約束求解器來幫助我們解決。 約束求解器的精妙之處就是,我們只描述約束限制,繁重的數值生成工作由工具來幫我們完成。 你只需“既要...又要...”,其他的讓下人干吧。

2023-03-08 14:06:00 630

630 我們在工作中常常會針對數組施加各式的約束,下面列舉一下有趣的Systemverilog數組約束示例。

2023-03-08 13:12:00 373

373 上一篇文章介紹了SystemVerilog的各種隨機化方法,本文將在其基礎上引入SystemVerilog的隨機約束方法(constraints)。通過使用隨機約束,我們可以將隨機限制在一定的空間內,有針對性地提高功能覆蓋率。

2023-01-21 17:03:00 981

981 SystemVerilog中Semaphore(旗語)是一個多個進程之間同步的機制之一,這里需要同步的原因是這多個進程共享某些資源。

2022-12-12 09:50:58 1712

1712 SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充了 C語言 數據類型、結構、壓縮和非

2022-12-08 10:35:05 935

935 SystemVerilog中可以將類屬性聲明為常量,即“只讀”。目的就是希望,別人可以讀但是不能修改它的值。

2022-11-29 10:25:42 1393

1393 SystemVerilog中多態能夠工作的前提是父類中的方法被聲明為virtual的。

2022-11-28 11:12:42 358

358 要想理解清楚SystemVerilog語言中的Upcasting和Downcasting概念,最好的方式從內存分配的角度理解。

2022-11-24 09:58:15 625

625 SystemVerilog中的句柄賦值和對象復制的概念是有區別的。

2022-11-21 10:32:59 378

378 在systemverilog中,如果一個類沒有顯式地聲明構造函數(new()),那么編譯仿真工具會自動提供一個隱式的new()函數。這個new函數會默認地將所有屬性變量。

2022-11-16 09:58:24 2400

2400 SystemVerilog union允許單個存儲空間以不同的數據類型存在,所以union雖然看起來和struct一樣包含了很多個成員,實際上物理上共享相同的存儲區域。

2022-11-09 09:41:28 440

440 SystemVerilog“struct”表示相同或不同數據類型的集合。

2022-11-07 10:18:20 1512

1512 SystemVerilog packages提供了對于許多不同數據類型的封裝,包括變量、task、function、assertion等等,以至于可以在多個module中共享。

2022-11-07 09:44:45 693

693 SystemVerilog中除了數組、隊列和關聯數組等數據結構,這些數據結構還可以嵌套。

2022-11-03 09:59:08 915

915 SystemVerilog提供了幾個內置方法來支持數組搜索、排序等功能。

2022-10-31 10:10:37 1320

1320 學習Systemverilog必備的手冊,很全且介紹詳細

2022-10-19 16:04:06 2

2 SystemVerilog casting意味著將一種數據類型轉換為另一種數據類型。在將一個變量賦值給另一個變量時,SystemVerilog要求這兩個變量具有相同的數據類型。

2022-10-17 14:35:40 1571

1571 event是SystemVerilog語言中的一個強大特性,可以支持多個并發進程之間的同步。

2022-10-17 10:21:33 772

772 Block,也就是語句塊,SystemVerilog提供了兩種類型的語句塊,分別是begin…end為代表的順序語句塊,還有以fork…join為代表的并發語句塊。

2022-09-14 10:27:30 713

713 HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

2022-08-31 09:06:59 937

937 IEEE SystemVerilog標準:統一的硬件設計規范和驗證語言

2022-08-25 15:52:21 0

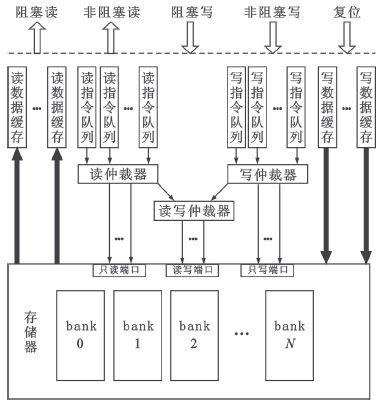

0 利用Systemverilog+UVM搭建soc驗證環境

2022-08-08 14:35:05 2

2 本文定義了通常用于描述使用SystemVerilog對硬件功能進行建模的詳細級別的術語。

2022-03-30 11:42:02 1151

1151 作者:limanjihe ?https://blog.csdn.net/limanjihe/article/details/83005713 SystemVerilog是一種硬件描述和驗證語言

2021-10-11 10:35:38 1882

1882 手冊的這一部分探討了使用SystemVerilog進行驗證,然后查看了使用SystemVerilog的優點和缺點。

2021-03-29 10:32:46 22

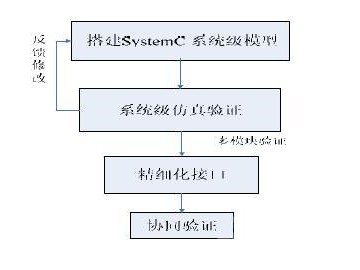

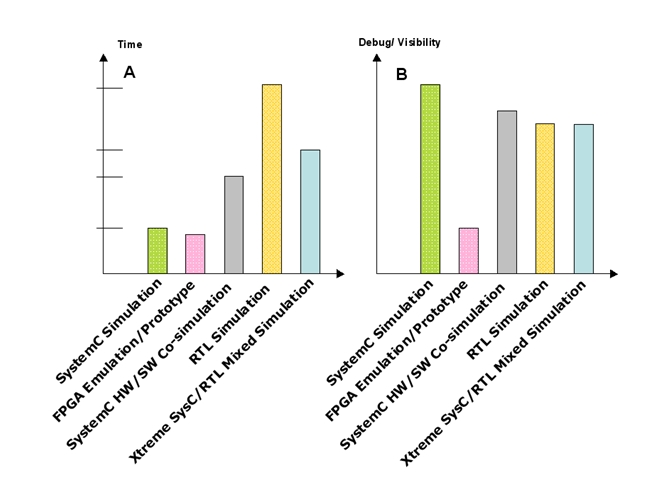

22 支持SystemC的電子系統級(ESL)設計和驗證環境旨在設計,分析,優化和驗證片上系統(SoC)平臺模型。這樣的環境構成了已建立的RTL實現流程的前端。

2019-10-03 17:05:00 4189

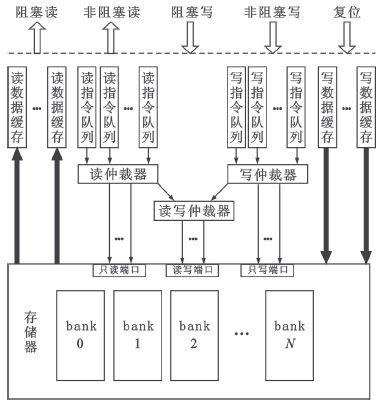

4189 硬件建模。但是隨著軟硬件復雜度的提高,C/C++語言難以再滿足要求。OSCI適時推出了SystemC語言來適應新的需求。如今SystemC已經被廣泛應用于SoC軟硬件建模中。

2018-12-05 07:43:00 5041

5041

SystemC 是由C++衍生而來,本質是在C++的基礎上添加了硬件擴展庫和仿真核,這使SystemC 可以在不同抽象級對復雜電子系統建模。

2018-07-19 11:55:00 4496

4496

基于SystemC構建多核DSP軟件仿真平臺_韋祎

2017-01-03 17:41:32 3

3 systemc語言簡單介紹,有助于初學者更好的運用和了解

2015-12-07 10:33:57 4

4 為了實現軟硬件協同設計和提高仿真速度的需求,采用SystemC語言的建模方法,通過對片上網絡體系結構的研究,提出了一種片上網絡的建模方案,并對一個mesh結構完成了SystemC的建模設

2013-07-30 11:46:44 42

42 在介紹SystemVerilog 斷言的概念、使用斷言的好處、斷言的分類、斷言的組成以及斷言如何被插入到被測設計(DUT)的基礎上,本文詳細地介紹了如何使用不同的斷言語句對信號之間的復

2011-05-24 16:35:19 36

36 本內容提供了SystemC片上系統設計及源代碼 #include scv.h #include fifo_mutex.h class rw_task_if : virtual public

2011-05-10 15:32:40 100

100 文章主要介紹《VMM for SystemVerilog》一書描述的如何利用SystemVerilog語言,采用驗證方法學以及驗證庫開發出先進驗證環境。文章分為四部分,第一部分概述了用SystemVerilog語言驗證復雜S

2011-05-09 15:22:02 51

51 SystemVerilog 是過去10年來多方面技術發展和實際試驗的結晶,包括硬件描述語言(HDL)、硬件驗證語言(HVL)、SystemC、Superlog和屬性規范語言。它們都從技術和市場的成敗中得到了豐富的經

2010-09-07 09:55:16 1075

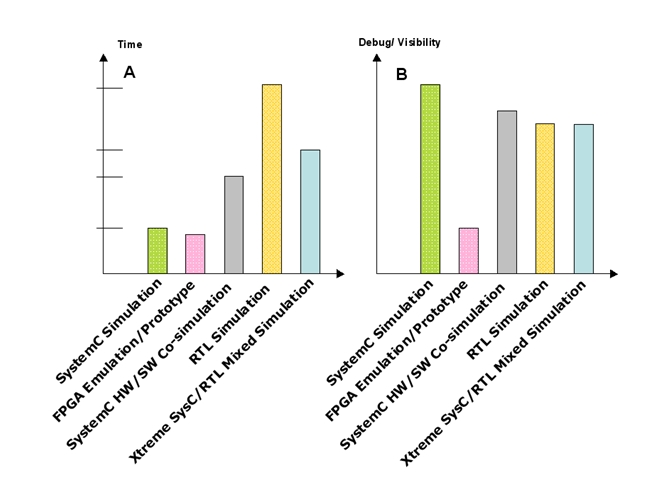

1075 隨著項目復雜程度的提高,最新的系統語言的聚合可以促進生產能力的激增,并為處在電子設計自動化(EDA)行業中的設計企業帶來益處。SystemVerilog和SystemC這兩種語言在設計流

2010-08-25 09:44:47 1119

1119 數字專用集成電路設計中的SystemC建模驗證方法

2010-07-17 16:36:23 31

31 視頻編解碼芯片中運動估計與補償單元(MECU)的算法復雜,使用傳統硬件描述語言建立模型和模型驗證的過程繁瑣耗時,為了縮短芯片驗證時間,本文針對MECU模塊提出了基于SystemC語言

2010-02-24 12:07:21 16

16 如何采用SystemVerilog 來改善基于FPGA 的ASIC 原型關鍵詞:FPGA, ASIC, SystemVerilog摘要:ASIC 在解決高性能復雜設計概念方面提供了一種解決方案,但是ASIC 也是高投資風險的,如90nm ASIC/S

2010-02-08 09:53:33 10

10 利用基于SystemC/TLM的方法學進行IP開發和FPGA建模

隨著系統級芯片技術的出現,設計規模正變得越來越大,因而變得非常復雜,同時上市時間也變得更加苛刻。通常RTL已

2010-01-04 13:11:50 5058

5058

本文利用形式化的方法對SystemVerilog的指稱語義進行研究,采用EBES(extendedbundle event structure)作為抽象模型,以便更好的描述SystemVerilog真并發的特點。我們的主要工作是:首先,

2009-12-22 14:01:07 12

12 事務級(Transaction-Level,TL)建模是SystemC 中提出的一種新型高層次建模方法,以CoCentric System Studio(CCSS)作為SystemC 仿真工具,以一個IP 路由系統為建模實例,分析了事務級建模

2009-07-30 15:27:27 24

24 Chapter 1: Introduction to SystemVerilogChapter 2: SystemVerilog Declaration SpacesExample 2-1: A

2009-07-22 14:48:12 115

115 Chapter 1: Introduction to SystemVerilogChapter 2: SystemVerilog Declaration SpacesExample 2-1: A

2009-07-22 14:45:34 20

20 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:12:50 19

19 SystemVerilog Assertion Handbook1 ROLE OF SYSTEMVERILOG ASSERTIONSIN A VERIFICATION METHODOLOGY

2009-07-22 14:08:48 188

188 This time, we have responded to a growing interest not

only in object-oriented programming but also in SystemVerilog. The w

2009-07-20 09:26:57 30

30 This time, we have responded to a growing interest not

only in object-oriented programming but also in SystemVerilog. The w

2009-07-20 09:24:47 35

35 Systemc From The Ground Up:The first question any reader should ask is “Why this book?” We

2009-07-10 17:27:57 36

36 IC 技術已發展到SoC 階段,系統級設計、仿真和驗證已成為IC 設計面臨的巨大挑戰。SystemC 是新興的系統級設計語言,為復雜系統的設計與驗證提供了解決方案。本文介紹SystemC 的特點

2009-05-18 13:44:58 27

27 decided

to write this book after learning SystemC and after using minimal documents

to help us through the quest of bec

2009-02-12 09:30:34 45

45

電子發燒友App

電子發燒友App

評論