SystemVerilog中的句柄賦值和對象復制的概念是有區別的。

PCI p1; p1 = new; PCI p2; p2 = p1; //class assignment

經過上面的代碼執行后,“p1”和 “p2” 最終指向的還是同一個內存空間,也就是說他們指向的是同一個對象實例。

如果你希望將p1的內容原封不同地復制到p2,他們就得是兩個不同的對象實例,即指向不同的內存空間。

PCI p1; p1 = new; PCI p2; p2 = new p1; //shallow copy

在上面的例子中,“p2”是一個新的對象實例,其中所有屬性值都復制自“p1.”

這在概念上稱為“shallow copy”,這是相對于“deep copy”而言的,具體的區別我們后面的文章會介紹。

shallow copy會復制對象中所有的屬性,包括類中其他的對象句柄,注意只能復制類中的對象句柄,而不能復制類中其他的對象實例。

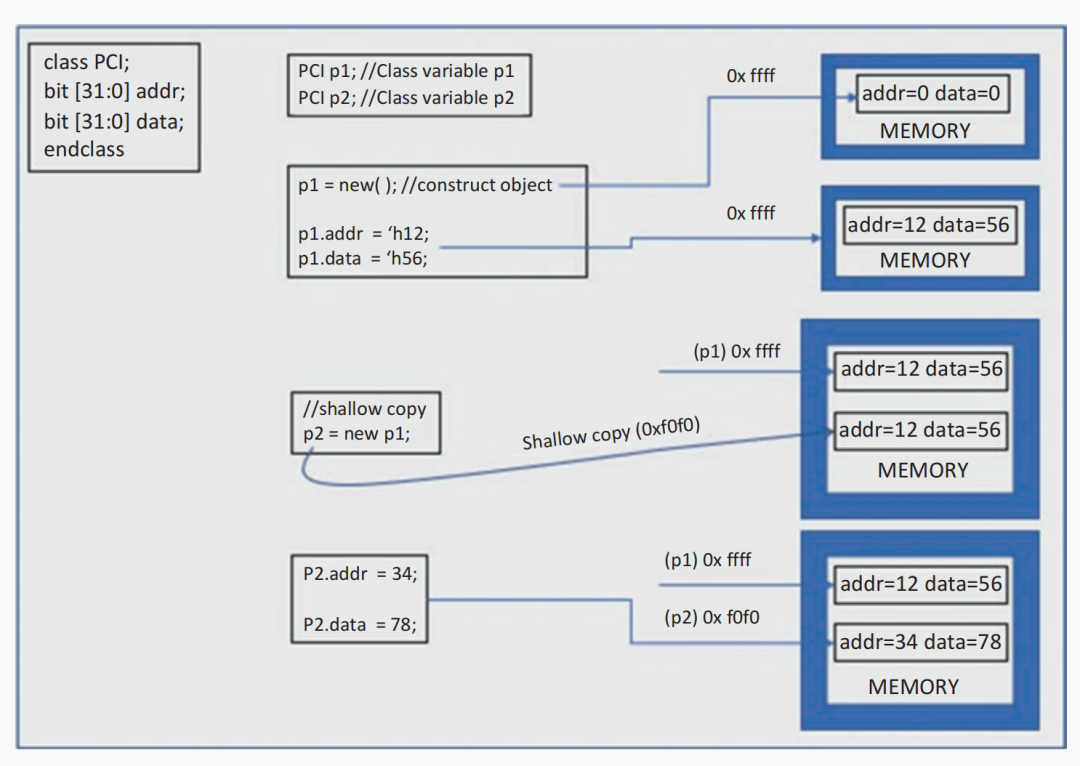

在上圖中,我們聲明了一個類“PCI” 和2個類句柄“p1” 和“p2”。

我們實例化“p1”,如上圖所示分配的物理地址空間是0xffff,屬性addr和data的初始值都是0。

然后別分別賦值addr為‘h12,data為‘h56。

shallow copy p1到p2,會分配一個新的物理地址空間0xf0f0。并且將p1中的“addr”和“data”復制給p2。

p2 = new p1;

我們改變p2中addr為34,data為78。因為是不同的對象實例,所以p2不會影響到p1。

假如我們想要復制的類中還有一個類對象,情況會怎樣?

module class_TOP( ); class PCIChild; logic [7:0] burstC; function new (logic [7:0] burst); burstC = burst; endfunction endclass : PCIChild class PCITop; logic [31:0] addrTop; logic [31:0] dataTop; PCIChild PCIc; task PCIM(logic [31:0] addr, logic [31:0] data, logic [7:0] burst); PCIc = new(burst); //instantiate PCIc addrTop = addr; dataTop = data; endtask function void disp (string instName); $display("[%s] addr = %h data = %h burst=%h", instName, addrTop, dataTop, PCIc.burstC); endfunction endclass : PCITop PCITop PCI1, PCI2; initial begin; PCI1 = new; PCI1.PCIM(32'h 0000_00f, 32'h f0f0_f0f0, 8'h12); PCI1.disp("PCI1"); PCI2 = new PCI1; //Shallow copy of PCI1 into PCI2 PCI2.disp("PCI2"); //copied content displayed PCI2.addrTop = 32'h1234_5678; PCI2.dataTop = 32'h5678_abcd; PCI2.PCIc.burstC = 8'h 9a; PCI2.disp("PCI2"); PCI1.disp("PCI1"); end endmodule

仿真log:

[PCI1] addr = 000000ff data = f0f0f0f0 burst=12 [PCI2] addr = 000000ff data = f0f0f0f0 burst=12 [PCI2] addr = 12345678 data = 5678abcd burst=9a [PCI1] addr = 000000ff data = f0f0f0f0 burst=9a V C S S i m u l a t i o n R e p o r t

在上面的例子中,我們聲明了一個名為PCIChild的類,其中含有屬性“burstC”。

我們還聲明了一個叫做PCITop的類,它有兩個屬性“addrTop”和“dataTop”。

我們在類PCITop中聲明類型為PCIChild的變量PCIc并在任務“PCIM”中實例化。

因此,PCIc現在擁有一個PCIChild類型的對象句柄。

后面我們聲明兩個類型為PCITop的變量“PCI1”和“PCI2”,并實例化PCI1。然后我們將PCI1的shallow copy到PCI2中(PCI2 = new PCI1;)。

在打印的log中我們可以發現PCI2中“addrTop”和“dataTop”修改不會反映到PCI1,而對PCI2中對象PCIc的修改會反映到PCI1。

PCI2.PCIc.burstC = 8'h 9a;

這是因為shallow copy只復制了類中的對象句柄,而沒有為對象PCI2.PCIc再次分配內存空間。

-

Verilog

+關注

關注

28文章

1351瀏覽量

110250 -

System

+關注

關注

0文章

165瀏覽量

37020 -

代碼

+關注

關注

30文章

4821瀏覽量

68890

原文標題:SystemVerilog中的Shallow Copy

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SystemVerilog中的Deep Copy概念

SystemVerilog中的“const”類屬性

關于SV中擴展類的copy函數的疑問

如何用questasim進行systemverilog仿真

SystemVerilog中的Deep Copy是如何實現的呢

SystemVerilog的斷言手冊

SystemVerilog中$cast的應用

SystemVerilog中的Semaphores

Systemverilog中的Driving Strength講解

SystemVerilog中的Shallow Copy

SystemVerilog中的Shallow Copy

評論