異步時序電路是指電路中除以使用帶時鐘的觸發器外,還可以使用不帶時鐘的觸發器和延遲元件作為存儲元件;電路中沒有統一的時鐘;電路狀態的改變由外部輸入的變化直接引起。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21786瀏覽量

605059 -

存儲

+關注

關注

13文章

4344瀏覽量

86047 -

觸發器

+關注

關注

14文章

2002瀏覽量

61284

發布評論請先 登錄

相關推薦

FPGA實戰演練邏輯篇54:VGA驅動接口時序設計之1概述

VGA驅動接口時序設計之1概述本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 第六章第8節中

發表于 07-26 21:56

用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

發表于 06-07 15:11

?33次下載

FPGA異步練習之測試文件(2)

FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能,FPGA允許無限次的編程。

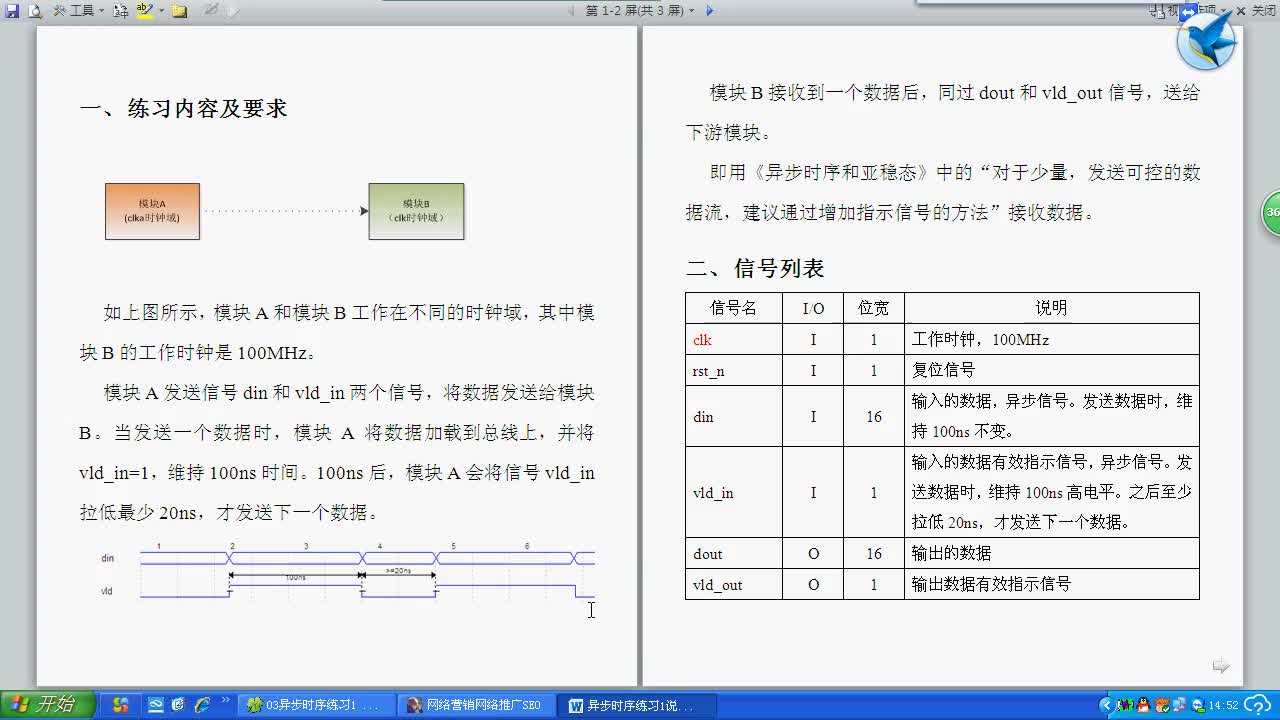

FPGA之異步練習1:設計思路

基于FPGA的數字系統設計中大都推薦采用同步時序的設計,也就是單時鐘系統。但是實際的工程中,純粹單時鐘系統設計的情況很少,特別是設計模塊與外圍芯片的通信中,跨時鐘域的情況經常不可避免。

FPGA之何為異步時序

異步時序電路是指電路中除以使用帶時鐘的觸發器外,還可以使用不帶時鐘的觸發器和延遲元件作為存儲元件;電路中沒有統一的時鐘;電路狀態的改變由外部輸入的變化直接引起.

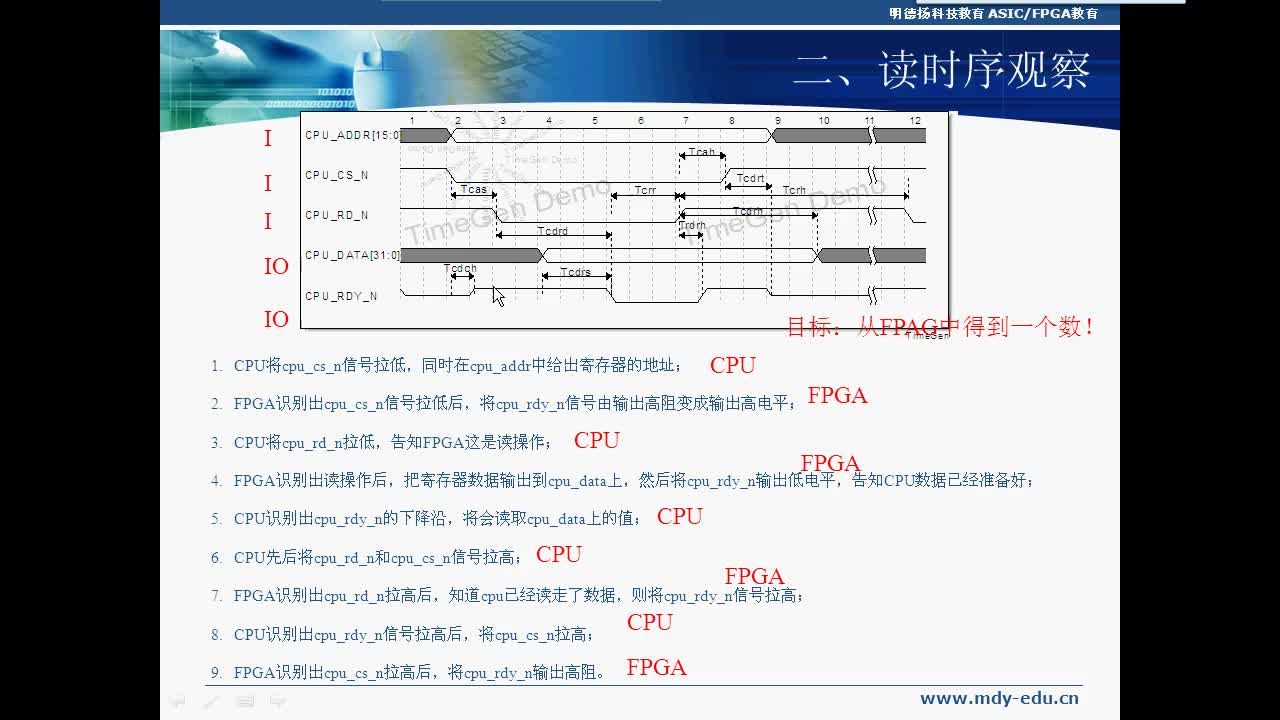

FPGA之異步練習2:接口時序參數

FPGA之異步練習2:接口時序參數

評論