一. 概述

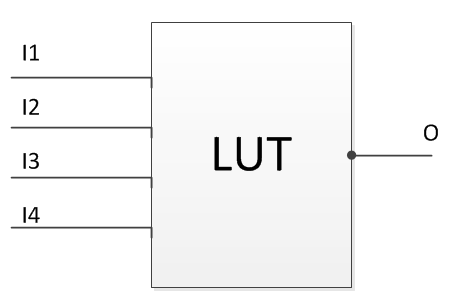

在文章《初識FPGA CLB之LUT實現邏輯函數》里面我們講過了LUT的原理,實現邏輯函數時,相當于一個ROM將結果預存,然后把通過輸入信號當作地址對預存的結果進行尋址。因此同樣借助LUT加幾個端口,就可以實現RAM。SLICEM里面的LUT就可以用來實現RAM資源。

二. 原理介紹

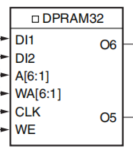

SLICEM里面的LUT跟SLICEL里面的LUT相比多了DI2,WA[6:1],CLK,WE這幾個端口。做RAM用的時候,其中DI1,DI2是寫數據輸入端口,O5,O6同樣是數據輸出端口,支持一次性兩bit或者單bit讀寫。A[6:1]為讀地址,WA[6:1]為寫地址,WE為寫使用,CLK為時鐘端口。

從這可以看出,一個LUT具有2^6=64bit的存儲空間。

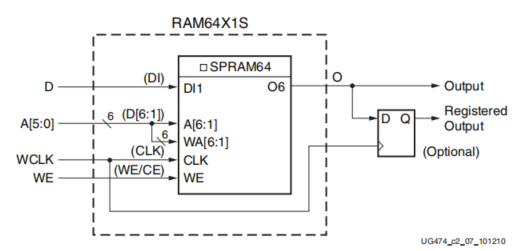

故一個LUT可以作為64x1bits的RAM(內存大小為64bit,1bit讀寫),地址為6位。當讀寫地址共用一個端口時為單端口RAM,不共用時則為雙端口RAM(SLICEM里面第一個LUT的WA與A是連在一起的,故第一個LUT做不了雙端口RAM)。輸出數據可以經過SLICEM里面的Register資源打一拍以提高時序特性(在工具里面可以自己設置)。

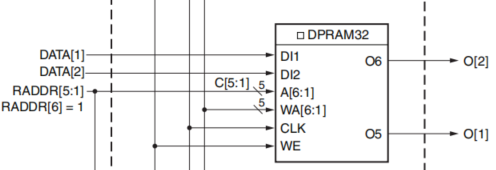

或者作為32x2bits的RAM(2bit讀寫),地址為5位,A[6]拉高。輸出為O5,O6。

三. 擴展與提升

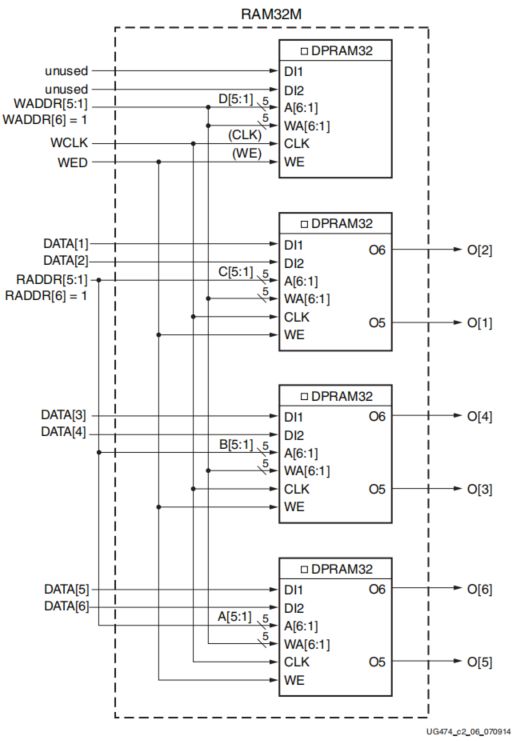

一個SLICEM里面有4個LUT,他們可以組合得到多種大小的RAM。首先就是四端口的32x2bits的RAM,支持一次性讀寫2bits,原理如下圖。四個LUT的寫數據端口DI1,DI2,寫使能WE,寫地址WA共用,稱為寫控制信號共用。讀地址A分別控制。

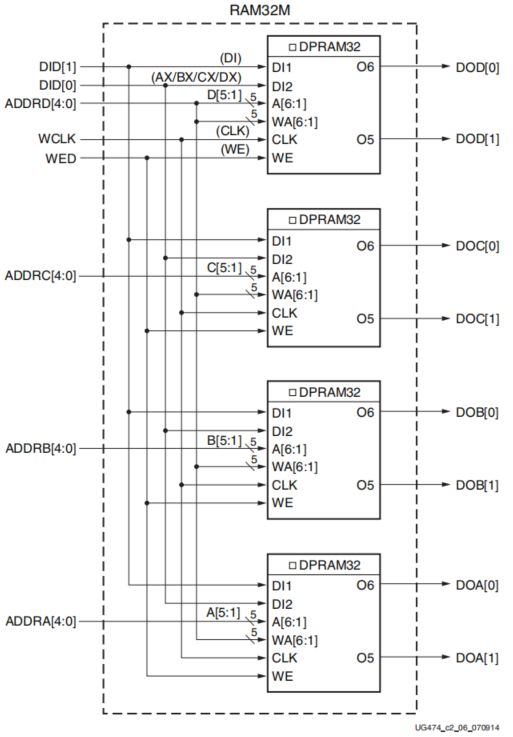

如下圖,4個LUT構成32x6bits的RAM,支持6bits讀寫操作。當讀寫共用一個地址時,就是單端口RAM,當讀寫不共用地址時就是雙端口RAM。可以看到第一個LUT其實沒用到,是因為第一個LUT的A與WA是連到一起的不能改變,所以做不了雙端口。其實現原理就是3個LUT的并行2bit讀寫。

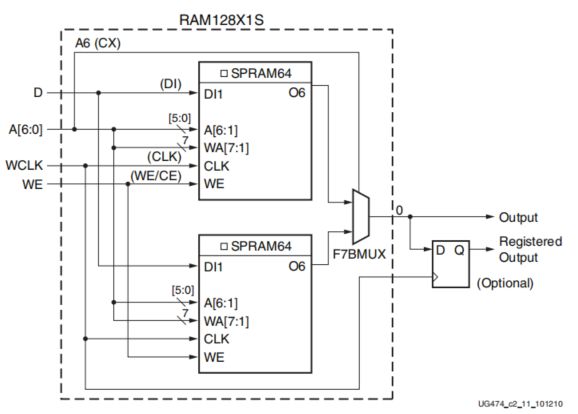

當然大家自己開動腦筋想一下也就知道了還可以組成其它什么類型的RAM,這里我們再舉個例子就是借助選擇器實現128x1bits的RAM。

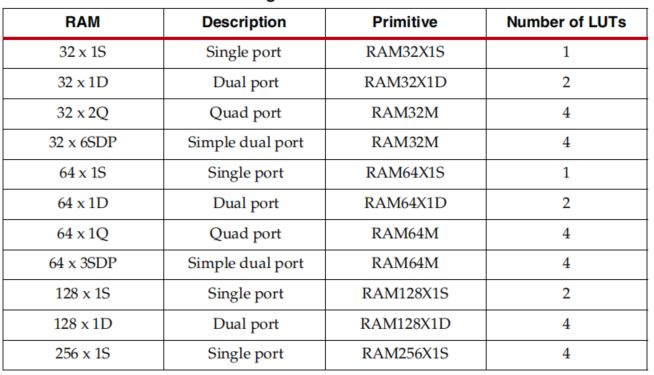

同樣借助選擇器在一個SLICEM里面還可以構成256x1bit的RAM,這里就不贅述,大家可以自行思考。總之在一個SLICEM里面可以實現的RAM有如下表中的幾種。

多個SLICEM資源配合就可以構成更多內存大小種類的RAM。

-

RAM

+關注

關注

8文章

1369瀏覽量

114896 -

輸出數據

+關注

關注

0文章

4瀏覽量

6162

原文標題:初識FPGA CLB之LUT實現RAM

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA重要資源CLB、Slice、LUT介紹

初識FPGA CLB之LUT實現邏輯函數

Virtex-6 FPGA上的可重配置LUT無法打包

寄存器中的RAM合成而不是LUT

SLICEM和SLICEL的輸出差異怎么回事

如何讀出LUT中RAM的上電值?

在FPGA設計中如何用LUT組建分布式的RAM

一文看懂ARM里的RAM和SDRAM有什么區別

FPGA內部可編程邏輯資源的結構,CLB資源介紹

Xilinx FPGA的三種片上存儲資源

對于Xilinx FPGA的片上存儲資源的統計介紹

FPGA的RAM存儲資源詳細資料說明

介紹SLICEM里的LUT如何形成RAM資源

介紹SLICEM里的LUT如何形成RAM資源

評論