7系列FPGA擁有豐富的時(shí)鐘資源。各種緩沖器類(lèi)型、時(shí)鐘輸入管腳和時(shí)鐘連接,可以滿(mǎn)足許多不同的應(yīng)用需求。選擇合適的時(shí)鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

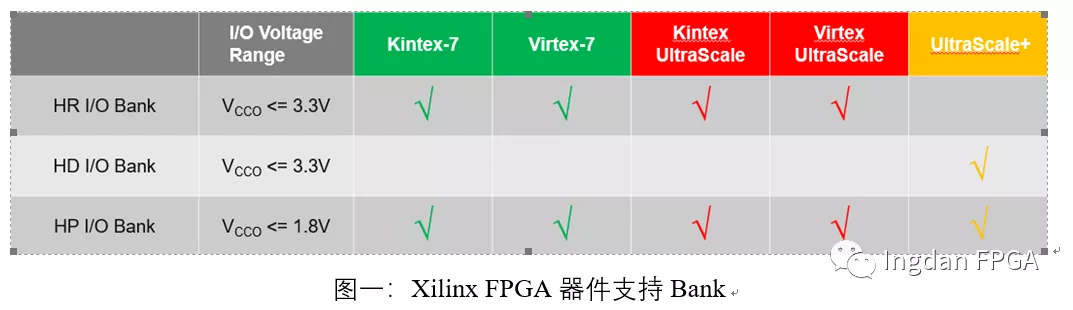

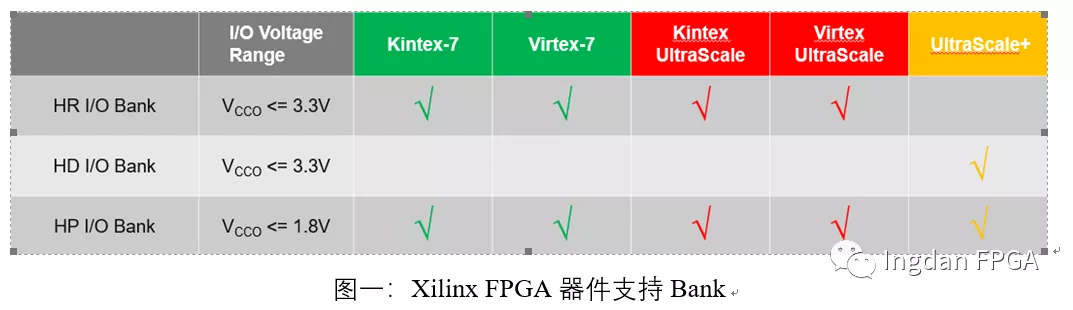

2475 引言:本文我們簡(jiǎn)單介紹下Xilinx FPGA管腳物理約束,包括位置(管腳)約束和電氣約束。

2022-07-25 10:13:44 4067

4067 FPGA是電子器件中的萬(wàn)能芯片,Xilinx FPGA處于行業(yè)龍頭地位更是非常靈活。FPGA管腳兼容性強(qiáng),能跟絕大部分電子元器件直接對(duì)接。Xilinx SelectIO支持電平標(biāo)準(zhǔn)多,除MIPI

2022-08-02 09:31:28 4824

4824

Xilinx FPGA的組成部分 本文是以Xilinx Kintex UltraScale+ 系列為參考所寫(xiě),其他系列有所不同,可以參考相應(yīng)的user guide文檔。 Xilinx家的FPGA有這

2022-12-27 15:54:52 1788

1788 鎖相環(huán)基本上是每一個(gè)fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時(shí)鐘資源對(duì)xilinx fpga的底層時(shí)鐘資源做過(guò)說(shuō)明,但是對(duì)于fpga的應(yīng)用來(lái)說(shuō),使用Clocking Wizard IP時(shí)十分方便的。

2023-06-12 17:42:03 2883

2883

。Xilinx FPGA7系列分為全局時(shí)鐘(Global clock)和局部時(shí)鐘(Regional clock)資源。目前,大型設(shè)計(jì)一般推薦使用同步時(shí)序電路。同步時(shí)序電路基于時(shí)鐘觸發(fā)沿設(shè)計(jì),對(duì)時(shí)鐘的周期

2023-07-24 11:07:04 655

655

本文主要介紹FPGA中常用的RAM、ROM、CAM、SRAM、DRAM、FLASH等資源,包括特性、工作原理、應(yīng)用場(chǎng)景等。

2023-08-15 15:41:12 1148

1148 通過(guò)上一篇文章“時(shí)鐘管理技術(shù)”,我們了解Xilinx 7系列FPGA主要有全局時(shí)鐘、區(qū)域時(shí)鐘、時(shí)鐘管理塊(CMT)。 通過(guò)以上時(shí)鐘資源的結(jié)合,Xilinx 7系列FPGA可實(shí)現(xiàn)高性能和可靠的時(shí)鐘分配

2023-08-31 10:44:31 1032

1032

本文主要介紹Xilinx FPGA的GTx的參考時(shí)鐘。下面就從參考時(shí)鐘的模式、參考時(shí)鐘的選擇等方面進(jìn)行介紹。

2023-09-15 09:14:26 1956

1956

Xilinx Block Memory Generator(BMG)是一個(gè)先進(jìn)的內(nèi)存構(gòu)造器,它使用Xilinx fpga中的嵌入式塊RAM資源生成面積和 性能優(yōu)化的內(nèi)存。

2023-11-14 17:49:43 736

736

.com建立時(shí)間:1984總部:加利福尼亞圣何塞市介紹:Xilinx是全球領(lǐng)先的可編程邏輯完整解決方案的供應(yīng)商,也是目前排名第一的FPGA解決方案提供商。開(kāi)發(fā)工具:Vivado,ISE(出了vivado之后

2018-01-29 11:05:29

的,存儲(chǔ)在存儲(chǔ)器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯(lián)接方式,并最終決定了FPGA所能實(shí)現(xiàn)的功能, 加電時(shí),FPGA芯片將EPROM中數(shù)據(jù)讀入片內(nèi)編程RAM中,配置完成后

2014-08-16 10:32:45

,FPGA上的全局時(shí)鐘管腳用完了就出現(xiàn)不夠用的情況。FPGA全局時(shí)鐘約束(Xilinx版本)[hide][/hide]

2012-02-29 09:46:00

片上資源如下圖,芯片選型時(shí)可以查閱一下。2)對(duì)于Xilinx的spartan系列:建議選擇spartan 6。選擇原因如下:1、首先現(xiàn)在有一部分高校開(kāi)設(shè)fpga課程使用的就是spartan 6

2020-09-04 10:10:49

XILINX FPGA 芯片整體架構(gòu)是如何構(gòu)成的?XILINX FPGA 芯片有哪些資源?

2021-10-29 06:26:23

本本將從常見(jiàn)的XILINX FPGA和Altera 兩家FPGA的電源供電作如下介紹:XILINX FPGA:FPGA(FPGA

2021-12-28 06:38:44

Xilinx FPGA上的嵌入式系統(tǒng)設(shè)計(jì)實(shí)例

2017-10-31 12:26:40

文檔創(chuàng)建既然是ROM,那么我們就必須實(shí)現(xiàn)給它準(zhǔn)備好數(shù)據(jù),然后在FPGA實(shí)際運(yùn)行時(shí),我們直接使用這些預(yù)存儲(chǔ)好的數(shù)據(jù)就行。Xilinx FPGA的片內(nèi)ROM支持初始化數(shù)據(jù)配置。如圖所示,我們可以創(chuàng)建一個(gè)名為

2019-01-09 16:02:21

Xilinx FPGA入門(mén)連載43:FPGA片內(nèi)ROM實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-06 12:22:53

文檔創(chuàng)建既然是ROM,那么我們就必須實(shí)現(xiàn)給它準(zhǔn)備好數(shù)據(jù),然后在FPGA實(shí)際運(yùn)行時(shí),我們直接使用這些預(yù)存儲(chǔ)好的數(shù)據(jù)就行。Xilinx FPGA的片內(nèi)ROM支持初始化數(shù)據(jù)配置。如圖所示,我們可以創(chuàng)建一個(gè)

2016-01-08 13:12:44

`Xilinx FPGA入門(mén)連載46:FPGA片內(nèi)ROM實(shí)例之chipscope在線調(diào)試特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm

2016-01-18 12:30:14

Xilinx FPGA入門(mén)連載47:FPGA片內(nèi)RAM實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-01-20 12:28:28

`Xilinx FPGA入門(mén)連載49:FPGA片內(nèi)RAM實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx庫(kù)

2016-01-25 12:55:23

Xilinx FPGA入門(mén)連載50:FPGA片內(nèi)RAM實(shí)例之chipscope在線調(diào)試特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-01-27 13:10:35

Xilinx FPGA入門(mén)連載51:FPGA片內(nèi)FIFO實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-02-26 10:26:05

`Xilinx FPGA入門(mén)連載53:FPGA片內(nèi)FIFO實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx

2016-03-02 12:30:57

`Xilinx FPGA入門(mén)連載54:FPGA 片內(nèi)FIFO實(shí)例之chipscope在線調(diào)試特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-04 13:13:12

`Xilinx FPGA入門(mén)連載55:FPGA 片內(nèi)異步FIFO實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

`Xilinx FPGA入門(mén)連載57:FPGA 片內(nèi)異步FIFO實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-03-16 11:32:11

`Xilinx FPGA入門(mén)連載58:FPGA 片內(nèi)異步FIFO實(shí)例之chipscope在線調(diào)試特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:13:05

`Xilinx FPGA入門(mén)連載59:FPGA 片內(nèi)ROM FIFO RAM聯(lián)合實(shí)例之功能概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2016-03-16 12:43:36

SF-SP6入門(mén)指南 -- FPGA片內(nèi)存儲(chǔ)器聯(lián)合實(shí)例之功能概述Lesson62 特權(quán)Xilinx FPGA SF-SP6入門(mén)指南 -- FPGA片內(nèi)存儲(chǔ)器聯(lián)合實(shí)例之功能仿真Lesson63 特權(quán)

2015-07-22 11:49:20

Xilinx公司產(chǎn)品導(dǎo)購(gòu)手冊(cè)Xilinx(賽靈思)相關(guān)產(chǎn)品介紹? Virtex-6 FPGA(XC6V)? Virtex-5 FPGA(XC5V)? Virtex-II FPGA(XC2V

2012-02-28 16:43:31

好。 另外就是關(guān)于塊RAM,Xilinx的雙口RAM是真的,Altera的沒(méi)有雙口RAM,如果你要實(shí)現(xiàn)真正的雙口RAM,只能用兩塊RAM來(lái)背靠背地實(shí)現(xiàn),這樣你的RAM資源就少了一半,如果你的應(yīng)用對(duì)片內(nèi)雙口RAM的需求很重要,用Altera的就劃不來(lái)。更多資料請(qǐng)點(diǎn)擊下載:[hide][/hide]

2012-02-28 14:40:59

xilinx_fpga結(jié)構(gòu)及工作原理介紹

2012-08-02 22:59:43

“S32K144是NXP推出的基于ARM Cortex-M4F內(nèi)核的汽車(chē)級(jí)通用MCU系列S32K1xx的第一顆高性能單片機(jī)。本文首先簡(jiǎn)要介紹S32K系列MCU的內(nèi)核和片上資源信息,然后列出S32K

2021-11-01 08:20:58

的內(nèi)存控制器的設(shè)計(jì)與應(yīng)用.pdf基于Spartan-3+FPGA的DDR2+SDRAM存儲(chǔ)器接口設(shè)計(jì).pdf一種采用FPGA設(shè)計(jì)的SDRAM控制器.pdf用Xilinx+FPGA實(shí)現(xiàn)DDR+SDRAM控制器.pdf

2012-07-28 14:40:53

ARM在片上資源確定的情況下,能否具備類(lèi)似FPGA自由分配管腳功能的能力?比如說(shuō)集成UART的TX/RX可以分配到任意管腳,而并不是只能分配到指定的幾個(gè)管腳?謝謝

2022-08-01 14:17:49

Cortex-A9 處理器,但該器件上的 FPGA 數(shù)量存在差別,如表 1 所示:[td]Xilinx Zynq SoC可編程邏輯單元塊 RAM 的容量大小 (Mb)DSP 切片

2018-08-31 14:43:05

⑴ 結(jié)合Xilinx、Altera 等公司的FPGA 芯片,簡(jiǎn)要羅列一下FPGA 內(nèi)部的資源或?qū)S媚K,并簡(jiǎn)要說(shuō)明這些資源的一些作用或用途。(至少列出5 項(xiàng),越多越好)⑵ 如果,對(duì)內(nèi)部特定資源,曾有

2012-03-08 11:03:49

丑。大神勿噴。因有小伙伴想學(xué)習(xí)Xilinx的FPGA,現(xiàn)在打算拿出兩塊板子,和有需要的朋友交換一下。現(xiàn)在只打算換Xilinx的FPGA的板子,這里再簡(jiǎn)單介紹一下板子上面的資源,或者可以實(shí)現(xiàn)的資源:1

2015-06-19 21:38:36

流程1.3.1 FPGA設(shè)計(jì)方法概論1.3.2 典型FPGA開(kāi)發(fā)流程1.3.3 基于FPGA的SOC設(shè)計(jì)方法1.4 Xilinx公司主流可編程邏輯器件簡(jiǎn)介1.4.1 Xilinx FPGA芯片介紹

2012-04-24 09:23:33

關(guān)于FPGA芯片資源介紹不看肯定后悔

2021-09-18 08:53:05

Xilinx Virtex-II Pro devices have redefined FPGAs.

2019-07-31 09:43:56

數(shù)據(jù)緩沖區(qū)。系統(tǒng)不需要CPU和外部存儲(chǔ)器。NVMeG3-IP的更多詳細(xì)信息在其數(shù)據(jù)表中描述,可以從我們的網(wǎng)站下載。下表1中顯示了XCZU9EG-2FFVB1156E FPGA器件上的FPGA資源使用情況

2020-09-03 16:07:35

,MicroBlaze通過(guò)OPB總線與外設(shè)IP及外部存儲(chǔ)器控制接口相連接,通過(guò)LMB(Local Memory Bus)總線與FPGA片上塊存儲(chǔ)器BRAM(Block RAM)相連接,還可以通過(guò)EMC

2009-06-25 08:12:37

是Block RAM。在Altera 和Xilinx 的各型號(hào)FPGA 器件上都集成了一種稱(chēng)為Block RAM 的片上內(nèi)存,它們以若干Kbits 為一塊,不同型號(hào)集成不同數(shù)量的塊,例如在Spartan-3E

2012-05-14 12:37:37

在FPGA 上設(shè)計(jì)一個(gè)高性能、靈活的、面積小的通信體系結(jié)構(gòu)是一項(xiàng)巨大的挑戰(zhàn)。大多數(shù)基于FPGA 的片上網(wǎng)絡(luò)都是運(yùn)行在一個(gè)單一時(shí)鐘下。隨著FPGA 技術(shù)的發(fā)展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

基于FPGA片上系統(tǒng)開(kāi)發(fā)的工程師。目錄第1章 基于XILINX FPGA嵌入式系統(tǒng)片上系統(tǒng)開(kāi)發(fā)概述第2章 MicroBlaze的構(gòu)架及接口第3章 MPMC的構(gòu)架、接口及使用第4章 嵌入式開(kāi)發(fā)套件(EDK

2017-12-08 14:27:35

基于Xilinx FPGA的DDR2 SDRAM存儲(chǔ)器接口

2012-08-20 18:55:15

320x240,而且都知道7670的顯示效果也不怎么樣,這是一次偶然的機(jī)會(huì)我得到的資源,便在basys3、zybo、國(guó)產(chǎn)FPGA PGT180H上移植成功,總體的顯示效果也是可能達(dá)到7670應(yīng)有的標(biāo)準(zhǔn)

2018-07-03 10:56:57

320x240,而且都知道7670的顯示效果也不怎么樣,這是一次偶然的機(jī)會(huì)我得到的資源,便在basys3、zybo、國(guó)產(chǎn)FPGA PGT180H上移植成功,總體的顯示效果也是可能達(dá)到7670應(yīng)有的標(biāo)準(zhǔn)

2018-07-09 09:31:05

如何利用Xilinx FPGA和存儲(chǔ)器接口生成器簡(jiǎn)化存儲(chǔ)器接口?

2021-05-06 07:23:59

切片是整個(gè)切片數(shù)量的一部分還是它們?cè)?b class="flag-6" style="color: red">FPGA上共享資源?2)如果我們沒(méi)有進(jìn)行任何DSP操作,那么DSP48E Slice是否可以用于實(shí)現(xiàn)某些常規(guī)邏輯,或者這些DSP Slice是否專(zhuān)門(mén)用于實(shí)現(xiàn)DSP

2019-04-04 06:36:56

(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門(mén)電路數(shù)有限的缺點(diǎn)。 本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時(shí)序邏輯來(lái)詳細(xì)的分析

2019-06-17 09:03:28

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP產(chǎn)品介紹使用Xilinx的FPGA、SoC和ACAP進(jìn)行設(shè)計(jì)和開(kāi)發(fā)

2021-01-22 06:38:47

怎么才能榨干FPGA的片上存儲(chǔ)資源?

2021-04-29 06:51:32

FPGA的片上存儲(chǔ)資源主要是分布式的RAM以及FLIP-FLOP觸發(fā)器,目前想做的是視覺(jué)追蹤相關(guān)的作品,想用FLIP-FLOP例化為RAM對(duì)部分圖像進(jìn)行緩存(擔(dān)心讀RAM速度不夠快),但是不知道

2023-08-16 08:25:55

作為開(kāi)發(fā)工具,7-series、UltraSCALE 和 UltraSCALE+ 系列使用 Vivado 作為開(kāi)發(fā)工具。 2.片上硬件資源 關(guān)于各系列的片上資源,可直接參考各系列的芯片選型手冊(cè)

2020-12-23 17:21:03

簡(jiǎn)談FPGA的片內(nèi)資源

2024-01-08 22:12:08

請(qǐng)問(wèn),如何對(duì)xilinx的virtex Ⅱ進(jìn)行功耗統(tǒng)計(jì)?在官網(wǎng)上的xpe文件沒(méi)有virtex Ⅱ的,那該如何統(tǒng)計(jì)呢?謝謝大神

2016-03-26 18:11:48

使用EMIF將Xilinx FPGA與TI DSP平臺(tái)接口:本應(yīng)用指南使用外部存儲(chǔ)器接口 (EMIF) 實(shí)現(xiàn)了 Xilinx FPGA 到 Texas Instruments 數(shù)字信號(hào)處理器 (DSP) 平臺(tái)的幾種連接。指南目錄本手冊(cè)包含以下章節(jié)

2009-11-01 15:00:09 68

68 十分鐘學(xué)會(huì)Xilinx FPGA 設(shè)計(jì)

Xilinx FPGA設(shè)計(jì)基礎(chǔ)系統(tǒng)地介紹了Xilinx公司FPGA的結(jié)構(gòu)特點(diǎn)和相關(guān)開(kāi)發(fā)軟件的使用方法,詳細(xì)描述了VHDL語(yǔ)言的語(yǔ)法和設(shè)計(jì)方法,并深入討

2010-03-15 15:09:08 177

177 本文介紹了FPGA外部存儲(chǔ)器的設(shè)計(jì)方法,可以有效地解決雷達(dá)實(shí)時(shí)信號(hào)處理過(guò)程中海量數(shù)據(jù)的存儲(chǔ)問(wèn)題,同時(shí)也可以充分利用FPGA去控制SDRAM和FLASH,不僅保證了資源的充分利用,也可以

2011-08-18 11:46:45 7309

7309

電子發(fā)燒友網(wǎng):針對(duì)目前 電子發(fā)燒友網(wǎng) 舉辦的 玩轉(zhuǎn)FPGA:iPad2,賽靈思開(kāi)發(fā)板等你拿 ,小編在電話回訪過(guò)程中留意到有很多參賽選手對(duì) Xilinx 公司的 FPGA 及其設(shè)計(jì)流程不是很熟悉,所以

2012-06-27 13:39:47 334

334 本書(shū)系統(tǒng)地論述了Xilinx FPGA開(kāi)發(fā)方法、開(kāi)發(fā)工具、實(shí)際案例及開(kāi)發(fā)技巧,內(nèi)容涵蓋Xilinx器件概述、Verilog HDL開(kāi)發(fā)基礎(chǔ)與進(jìn)階、Xilinx FPGA電路原理與系統(tǒng)設(shè)計(jì)

2012-07-31 16:20:42 11268

11268

本文是關(guān)于 xilinx公司的7系列FPGA應(yīng)用指南。xilinx公司的7系列FPGA包括3個(gè)子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對(duì)這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對(duì)比表

2012-08-07 17:22:55 201

201 FPGA 設(shè)計(jì)人員在滿(mǎn)足關(guān)鍵時(shí)序余量的同時(shí)力爭(zhēng)實(shí)現(xiàn)更高性能,在這種情況下,存儲(chǔ)器接口的設(shè)計(jì)是一個(gè)一向構(gòu)成艱難而耗時(shí)的挑戰(zhàn)。Xilinx FPGA 提供 I/O 模塊和邏輯資源,從而使接口設(shè)計(jì)變

2013-03-14 15:16:07 71

71 Xilinx FPGA工程例子源碼:Xilinx DDR2存儲(chǔ)器接口調(diào)試代碼

2016-06-07 14:54:57 27

27 FPGA學(xué)習(xí)資料教程之Xilinx-FPGA-引腳功能詳細(xì)介紹

2016-09-01 15:27:27 0

0 談到數(shù)字邏輯,談到FPGA設(shè)計(jì),每位工程師都離不開(kāi)時(shí)鐘。這里我們簡(jiǎn)單介紹一下xilinx 7 系列中的時(shí)鐘資源。時(shí)鐘設(shè)計(jì)的好壞,直接影響到布局布線時(shí)間、timing的收斂情況,FPGA的時(shí)鐘

2017-02-08 05:33:31 561

561

Xilinx FPGA編程技巧常用時(shí)序約束介紹,具體的跟隨小編一起來(lái)了解一下。

2018-07-14 07:18:00 4129

4129

Xilinx FPGA的Maxim參考設(shè)計(jì)

2017-10-31 09:59:24 23

23 這一次給大家分享的內(nèi)容主要涉及Xilinx FPGA內(nèi)的CLBs,SelectIO和Clocking資源,適合對(duì)FPGA設(shè)計(jì)有時(shí)序要求,卻還沒(méi)有足夠了解的朋友。

2018-03-21 14:48:00 4672

4672

介紹賽靈思為各企業(yè)提供的專(zhuān)業(yè)的關(guān)于Xilinx的資源培訓(xùn),以及課程內(nèi)容

2018-05-22 13:47:33 3154

3154

JESD204B協(xié)議是目前高速AD,DA通用的協(xié)議。對(duì)于基帶使用FPGA用戶(hù)來(lái)說(shuō),Xilinx品牌的FPGA使用更為常見(jiàn)。Xilinx提供了JESD204的IP core,設(shè)計(jì)起來(lái)比較方便。

2018-07-04 10:12:00 3977

3977 現(xiàn)在的FPGA里面有很多存儲(chǔ)資源,DSP(數(shù)字信號(hào)處理)資源,布線通道,I/O資源,當(dāng)然最根本的還是CLB(Configurable Logic Block)。Xilinx的資源分布采用ASMBL架構(gòu)。

2018-10-22 11:00:43 5270

5270 在本演示中,Eideticom描述了NoLoad?,這是一款面向Xilinx FPGA的存儲(chǔ)和計(jì)算加速平臺(tái)。

2018-11-26 06:26:00 3054

3054 Xilinx FPGA是支持OpenStack的第一個(gè)(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺(tái)上運(yùn)行每個(gè)演示,并使用OpenStack進(jìn)行配置和管理。

2018-11-23 06:14:00 3322

3322 Xilinx FPGA有三種可以用來(lái)做片上存儲(chǔ)(RAM,ROM等等)的資源,第一個(gè)就是Flip Flop;第二種就是SLICEM里面LUT;第三種就是Block RAMs資源。

2018-12-16 11:31:21 12305

12305

本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 5120

5120 Xilinx 7系列FPGA概覽 文章目錄 Xilinx 7系列FPGA概覽 1.Xilinx的四個(gè)工藝級(jí)別 2.Virtex、Kintex、Artix和Spartan 3.7系列特點(diǎn) 4.7系列

2020-11-13 18:03:30 14065

14065 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的RAM存儲(chǔ)資源詳細(xì)資料說(shuō)明包括了:1、 FPGA存儲(chǔ)資源簡(jiǎn)介,2、 不同廠家的 Block RAM 布局,3、 塊 RAM 和分布式 RAM 資源,4、 Xilinx Block RAM 架構(gòu)及應(yīng)用

2020-12-09 15:31:00 10

10 Xilinx7系列FPGA的體系結(jié)構(gòu)具有靈活的內(nèi)部?jī)?nèi)存資源,可以配置為各種不同的大小。本白皮書(shū)詳細(xì)介紹了可用的功能,說(shuō)明了各種可用內(nèi)存大小,并顯示了使用不同資源執(zhí)行不同大小內(nèi)存功能的利弊。

2020-12-09 16:15:00 8

8 Xilinx7系列FPGA包括四個(gè)FPGA系列,它們都是為最低功耗而設(shè)計(jì)的,以使一個(gè)通用設(shè)計(jì)能夠跨系列擴(kuò)展以獲得最佳的功率、性能和成本。斯巴達(dá)-7系列是7系列產(chǎn)品中密度最低、成本最低的入門(mén)級(jí)產(chǎn)品

2020-12-10 14:20:00 18

18 xilinx FPGA的資源一般指IOB,CLB,BRAM,DCM,DSP五種資源。其中IOB就是input/output block,完成不同電氣特性下對(duì)輸入輸出信號(hào)的的驅(qū)動(dòng)和匹配要求。

2020-12-29 16:59:33 12

12 SRL(移位寄存器)資源,在FPGA中都有,不過(guò)是叫不同的名字。Xilinx FPGA內(nèi)部的LUT有個(gè)特殊功能,就是可以配置成可變長(zhǎng)度SRL。

2020-12-31 16:45:35 8

8 本文檔的主要內(nèi)容詳細(xì)介紹的是Xilinx 7 系列FPGA中的Serdes總結(jié)。

2020-12-31 17:30:58 25

25 Xilinx 7系列FPGA由四類(lèi)FPGA系列組成,解決了從低成本、小尺寸、成本敏感、高容量應(yīng)用到最苛刻的高性能應(yīng)用的超高端連接帶寬、邏輯容量和信號(hào)處理能力等完整的系統(tǒng)需求。 首先我們先看

2021-03-09 11:44:22 6523

6523 引言:7系列FPGA具有多個(gè)時(shí)鐘路由資源,以支持各種時(shí)鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時(shí)鐘路由資源,必須了解如何從PCB到FPGA獲取用戶(hù)時(shí)鐘,確定哪些時(shí)鐘路由資源

2021-03-22 10:16:18 4353

4353

引言:從本文開(kāi)始,我們陸續(xù)介紹Xilinx 7系列FPGA的時(shí)鐘資源架構(gòu),熟練掌握時(shí)鐘資源對(duì)于FPGA硬件設(shè)計(jì)工程師及軟件設(shè)計(jì)工程師都非常重要。本章概述7系列FPGA時(shí)鐘,比較了7系列FPGA時(shí)鐘

2021-03-22 10:25:27 4326

4326 Xilinx FPGA pcb設(shè)計(jì)

2023-05-29 09:11:36 0

0 上一篇文章,介紹了基于STM32F103的JTAG邊界掃描應(yīng)用,演示了TopJTAG Probe軟件的應(yīng)用,以及邊界掃描的基本功能。本文介紹基于Xilinx FPGA的邊界掃描應(yīng)用,兩者幾乎是一樣。

2023-09-13 12:29:37 655

655

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論