1. 基本的約束方法

為了保證成功的設計,所有路徑的時序要求必須能夠讓執行工具獲取。最普遍的三種路徑為:

輸入路徑(Input Path),使用輸入約束

寄存器到寄存器路徑(Register-to-Register Path),使用周期約束

輸出路徑(Output Path),使用輸出約束

具體的異常路徑(Path specific exceptions),使用虛假路徑.多周期路徑約束

1.1. 輸入約束Input Constraint

OFFSET IN約束限定了輸入數據和輸入時鐘邊沿的關系。

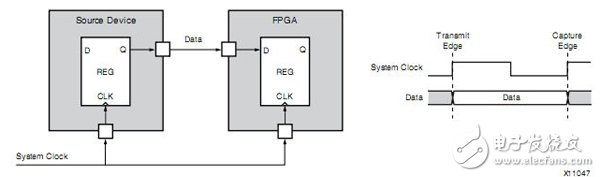

1.1.1. 系統同步輸入約束System Synchronous Input

在系統同步接口中,同一個系統時鐘既傳輸數據也獲取數據。考慮到板子路徑延時和時鐘抖動,接口的操作頻率不能太高。

1.1簡化的系統同步輸入SDR接口電路圖

1.2SDR系統同步輸入時序

上述時序的約束可寫為:

NET “SysClk” TNM_NET = “SysClk”;

TIMESPEC “TS_SysClk” = PERIOD “SysClk” 5 ns HIGH 50%;

OFFSET = IN 5 ns VALID 5 ns BEFORE “SysClk”;

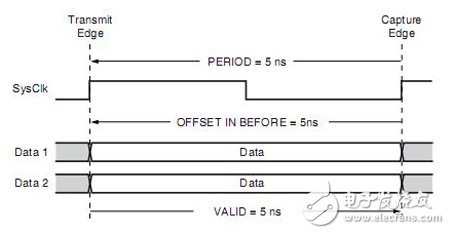

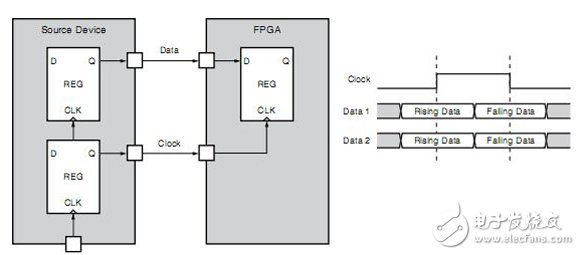

1.1.2. 源同步輸入約束Source Synchronous Input

在源同步接口中,時鐘是在源設備中和數據一起產生并傳輸。

1.3簡化的源同步輸入DDR接口電路

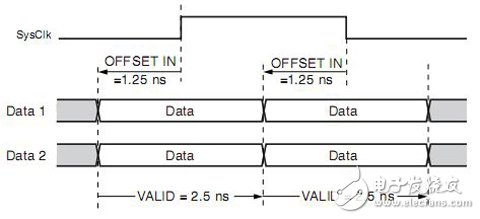

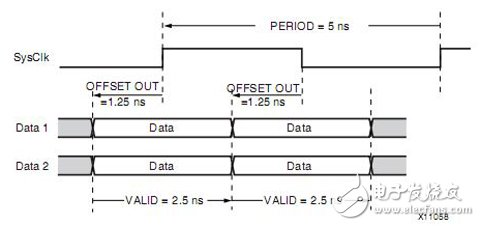

1.4DDR源同步輸入時序

上圖的時序約束可寫為:

NET “SysClk” TNM_NET = “SysClk”;

TIMESPEC “TS_SysClk” = PERIOD “SysClk” 5 ns HIGH 50%;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE “SysClk” RISING;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE “SysClk” FALLING;

1.2. 寄存器到寄存器約束Register-to-Register Constraint

寄存器到寄存器約束往往指的是周期約束,周期約束的覆蓋范圍包括:

覆蓋了時鐘域的時序要求

覆蓋了同步數據在內部寄存器之間的傳輸

分析一個單獨的時鐘域內的路徑

分析相關時鐘域間的所有路徑

考慮不同時鐘域間的所有頻率.相位.不確定性差異

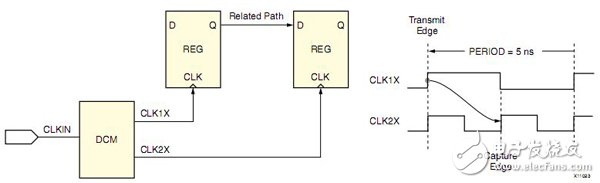

1.2.1. 使用DLL, DCM, PLL, and MMCM等時鐘器件自動確定同步關系

使用這一類時鐘IP Core,只需指定它們的輸入時鐘約束,器件將自動的根據用戶生成IP Core時指定的參數約束相關輸出,不需用戶手動干預。

1.5輸入到DCM的時鐘約束

上圖的時序約束可寫為:

NET “ClkIn” TNM_NET = “ClkIn”;

TIMESPEC “TS_ClkIn” = PERIOD “ClkIn” 5 ns HIGH 50%;

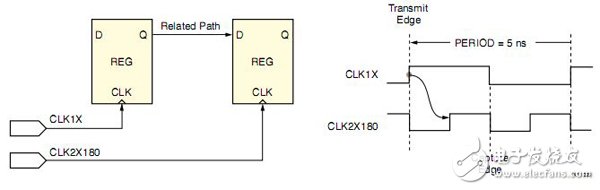

1.2.2. 手動約束相關聯的時鐘域

在某些情況下,工具并不能自動確定同步的時鐘域之間的時鐘時序關系,這個時候需要手動約束。例如:有兩個有相位關系的時鐘從不同的引腳進入FPGA器件,這個時候需要手動約束這兩個時鐘。

1.6通過兩個不同的外部引腳進入FPGA的相關時鐘

上圖的時序約束可寫為:

NET“Clk1X“TNM_NET=“Clk1X”;

NET“Clk2X180“TNM_NET=“Clk2X180”;

TIMESPEC“TS_Clk1X”=PERIOD“Clk1X 7 5ns;

TIMESPEC”TS_Clk2X180“=PERIOD”Clk2X180“TS_Clk1X/2PHAS2 +1.25ns;

1.2.3. 異步時鐘域

異步時鐘域的發送和接收時鐘不依賴于頻率或相位關系。因為時鐘是不相關的,所以不可能確定出建立時間.保持時間和時鐘的最終關系。因為這個原因,Xilinx推薦使用適當的異步設計技術來保證對數據的成功獲取。Xilinx約束系統允許設計者在不需考慮源和目的時鐘頻率.相位的情況下約束數據路徑的最大延時。

異步時鐘域使用的約束方法的流程為:

為源寄存器定義時序組

為目的寄存器定義時序組

使用From-to和DATAPATHDELAY關鍵字定義寄存器組之間的最大延時

1.3. 輸出約束Output Constraint

輸出時序約束約束的是從內部同步元件或寄存器到器件管腳的數據。

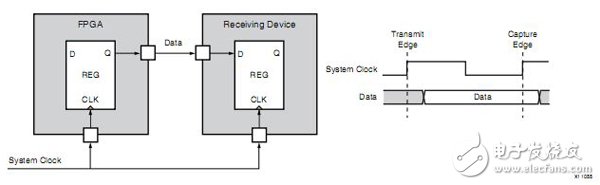

1.3.1. 系統同步輸出約束System Synchronous Output Constraint

系統同步輸出的簡化模型如圖所示,在系統同步輸出接口中,傳輸和獲取數據是基于同一個時鐘的。

1.7系統同步輸出

其時序約束可寫為:

NET “ClkIn” TNM_NET = “ClkIn”;

OFFSET = OUT 5 ns AFTER “ClkIn”;

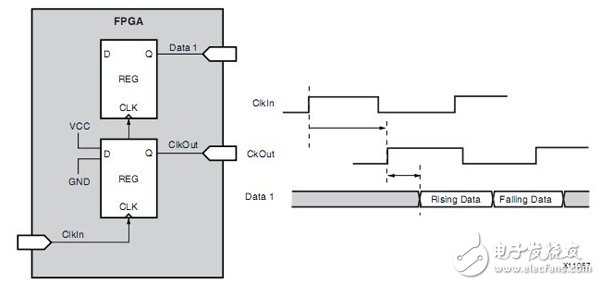

1.3.2. 源同步輸出約束Source Synchronous Output Constraint

在源同步輸出接口中,時鐘是重新產生的并且在某一FPGA時鐘的驅動下和數據一起傳輸至下游器件。

1.8源同步輸出簡化電路時序圖

1.9源同步小例子時序圖

小例子的時序約束可寫為:

NET “ClkIn” TNM_NET = “ClkIn”;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” RISING;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” FALLING;

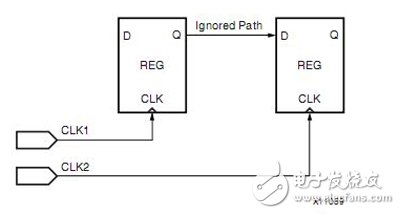

1.3.3. 虛假路徑約束False Path Constraint

令SRC_GRP為一組源寄存器,DST_GRP為一組目的寄存器,如果你確定SRC_GRP到DST_GRP之間的路徑不會影響時序性能,那么可以將這一組路徑約束為虛假路徑,工具在進行時序分析的時候將會跳過對這組路徑的時序分析。這種路徑最常見于不同時鐘域的寄存器數據傳輸,如下圖:

1.10虛假路徑

其約束可寫為:

NET “CLK1” TNM_NET = FFS “GRP_1”;

NET “CLK2” TNM_NET = FFS “GRP_2”;

TIMESPEC TS_Example = FROM “GRP_1” TO “GRP_2” TIG;

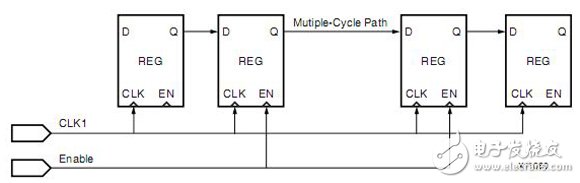

1.3.4. 多周期路徑約束Multi-Cycle Path Constraint

在多周期路徑里,令驅動時鐘的周期為PERIOD,數據可以最大n*PERIOD的時間的從源同步元件傳輸到目的同步元件,這一約束降低工具的布線難度而又不會影響時序性能。這種約束通常用在有時鐘使能控制的同步元件路徑中。

圖 1-11時鐘使能控制的寄存器路徑

必須說明的是上圖Enable信號的產生周期必須大于等于n*PERIOD,且每個Enable傳輸一個數據。假設上圖的n=2,MC_GRP為時鐘使能Enable控制的多周期同步元件組,則約束可寫為:

NET “CLK1” TNM_NET = “CLK1”;

TIMESPEC “TS_CLK1” = PERIOD “CLK1” 5 ns HIGH 50%;

NET “Enable” TNM_NET = FFS “MC_GRP”;

TIMESPEC TS_Example = FROM “MC_GRP” TO “MC_GRP” TS_CLK1*2;

-

Xilinx

+關注

關注

71文章

2168瀏覽量

121660 -

fpga編程

+關注

關注

0文章

4瀏覽量

4643

發布評論請先 登錄

相關推薦

深入了解時序約束以及如何利用時序約束實現FPGA 設計的最優結果

正點原子FPGA靜態時序分析與時序約束教程

Xilinx FPGA編程技巧常用時序約束介紹

Xilinx FPGA編程技巧常用時序約束介紹

評論