首先開門見山的回答這個問題——LUT的作用是 實現(xiàn)所有的邏輯函數(shù) ,也就是類似于計算Y=A&B+C+D之類的算式結果!

LUT是什么構成的?

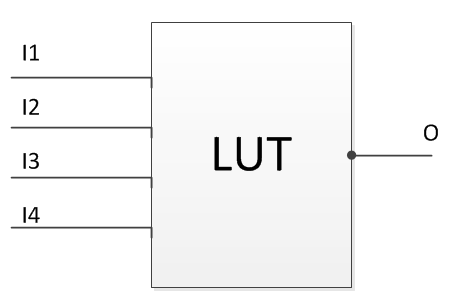

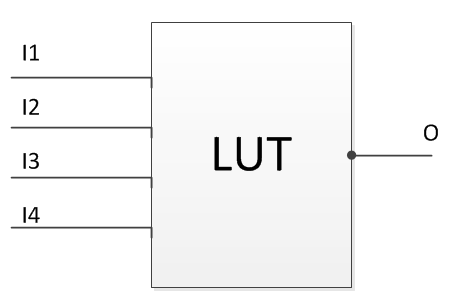

xilinx的LUT是4輸入1輸出的 RAM ,也就是4根地址線的,一根數(shù)據(jù)線的RAM,并且I1是高地址位,I4是低地址位,樣子參考下圖。I1到I4就是地址線,O是輸出數(shù)據(jù)線。

RAM怎么實現(xiàn)邏輯運算?

假設要實現(xiàn)運算Y=A&B+C+D。假設I1代表A,I2代表B,I3代表C,I4代表D,O代表Y。此時將下表存入LUT中。從下表可以看出,LUT存儲的就是函數(shù)Y=A&B+C+D的真值表。 **4個輸入信號的地址對應的位置上存儲的就是4個地址進行邏輯運算后的真值!** 這樣任何4輸入的所有邏輯運算都可以通過存取真值表的方法實現(xiàn)。一旦輸入地址中的任何一個數(shù),立馬就會輸出存儲位置上對應的結果。

verilog怎么實現(xiàn)上面的函數(shù)呢?

reg Y;

reg [3:0] I ;

always@(*)begin Y=(I[0] & I1) | I2 | I3;end

請注意( )里面是 ,代表不需要時鐘,實現(xiàn)的是組合邏輯。如果最后一行變成如下:

always@(posedge clk)begin Y=(I[0] & I1) | I2 | I3;end

則生成的不是一個LUT是一個LUT加一個觸發(fā)器FF。如下圖。

-

RAM

+關注

關注

8文章

1369瀏覽量

114901 -

觸發(fā)器

+關注

關注

14文章

2003瀏覽量

61290 -

LUT

+關注

關注

0文章

49瀏覽量

12550 -

FPGA系統(tǒng)

+關注

關注

0文章

10瀏覽量

7053 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8289

發(fā)布評論請先 登錄

相關推薦

初識FPGA CLB之LUT實現(xiàn)邏輯函數(shù)

FPGA中LUT設計

使用的LUT觸發(fā)器對的數(shù)量與Slice Register和Slice LUT的關系是什么?

LUT實現(xiàn)的逆變器真的是FPGA上的逆變器嗎?

LUT和Kintex 7 FPGA芯片中的FF所需的資源

Spartan 6 FPGA LUT中是否有pmos和nmos transisors?

LUT名字的數(shù)字含義是什么?

LUT如何構成邏輯函數(shù)

FPGA中實現(xiàn)LUT設計的簡介

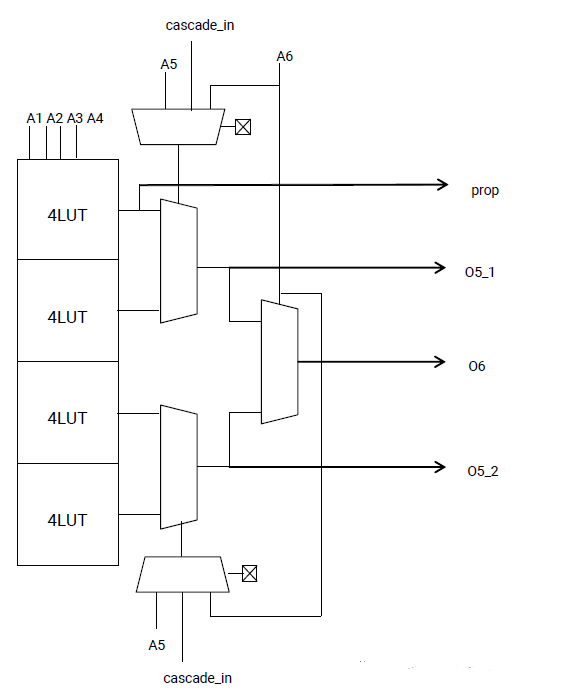

物理可級聯(lián)的LUT的優(yōu)勢在哪?

FPGA——LUT/FDRE/FDCE/FDSE/FDPE

FPGA中的LUT有什么作用

LUT是什么構成的?FPGA里的LUT有什么作用?

LUT是什么構成的?FPGA里的LUT有什么作用?

評論