一前言

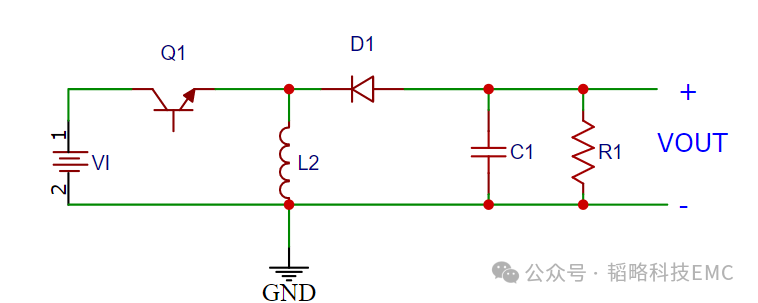

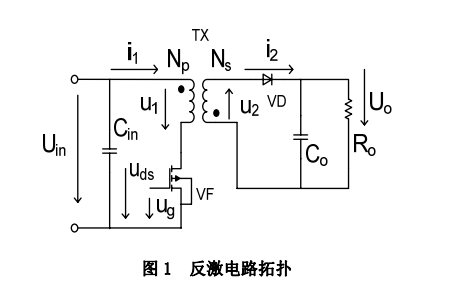

目前市面上機器的電源電路設計,普遍采用buck和boost,或者buck-boost。今天所講的反激式電路就是基于buck-boost的電路拓撲所演變的,下圖是buck-boost的電路拓撲。

反激式電路相對BUCK和boost電路的整改思路有所不同,但是回到本質上,噪聲超標還是dv/dt或者di/dt過高的問題,只要找到問題源頭,整改措施還是一樣。

二前期準備

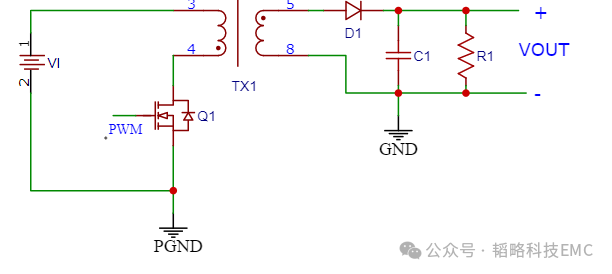

整改前期,我們可以對反激電路工作原理進行理解,這樣可以方便我們后續定位噪聲源頭,對POE供電的反激式電路進行電路分析。以下是反激式電路的電路圖,而POE的芯片內部集成MOS管,替代了Q1MOS管。

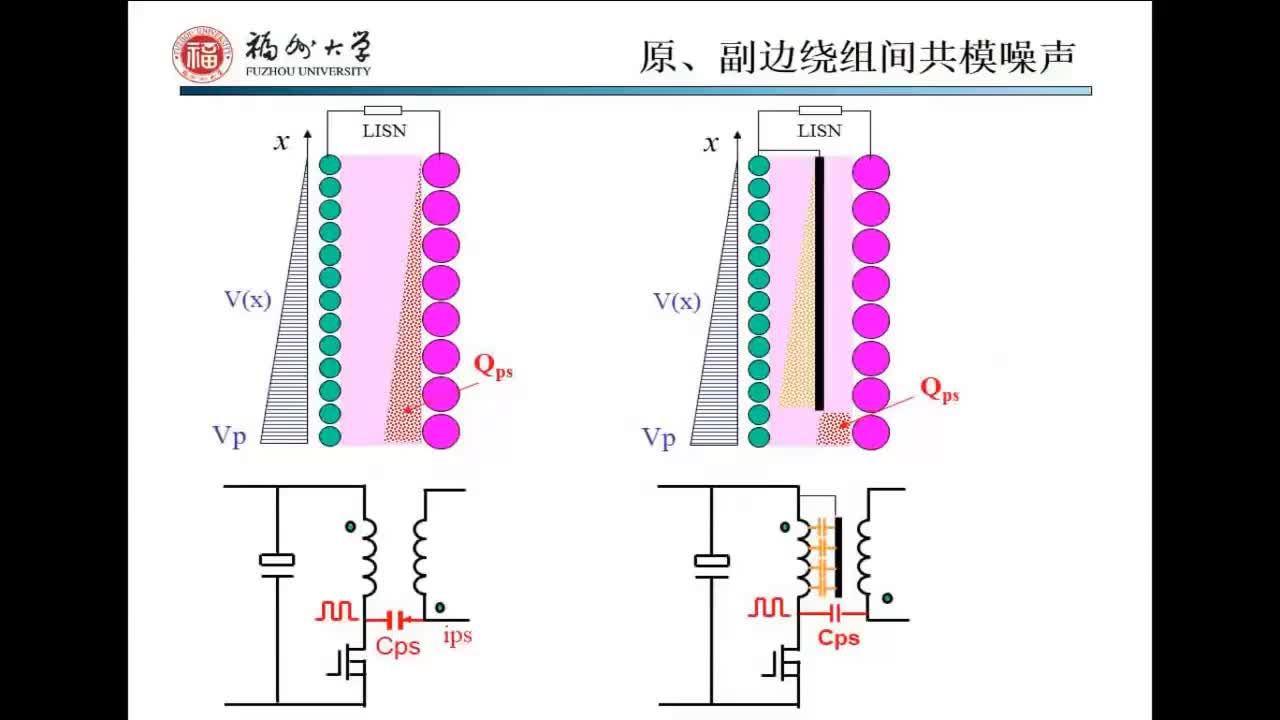

當Q1導通時輸入給初級線圈充電,而次級線圈由于同名端極性相同,續流管D1截止,后端負載由輸出電容提供;這也是Flyback名字的由來。當Q1截止時,初級線圈的極性反轉,此時次級線圈電壓上正下負,續流管Q1導通。對于噪聲源來說,大的di/dt和dv/dt 產生的地方:1.變壓器TX1;2.MOSFET Q1;3.輸出二極管D1。

三案例分析

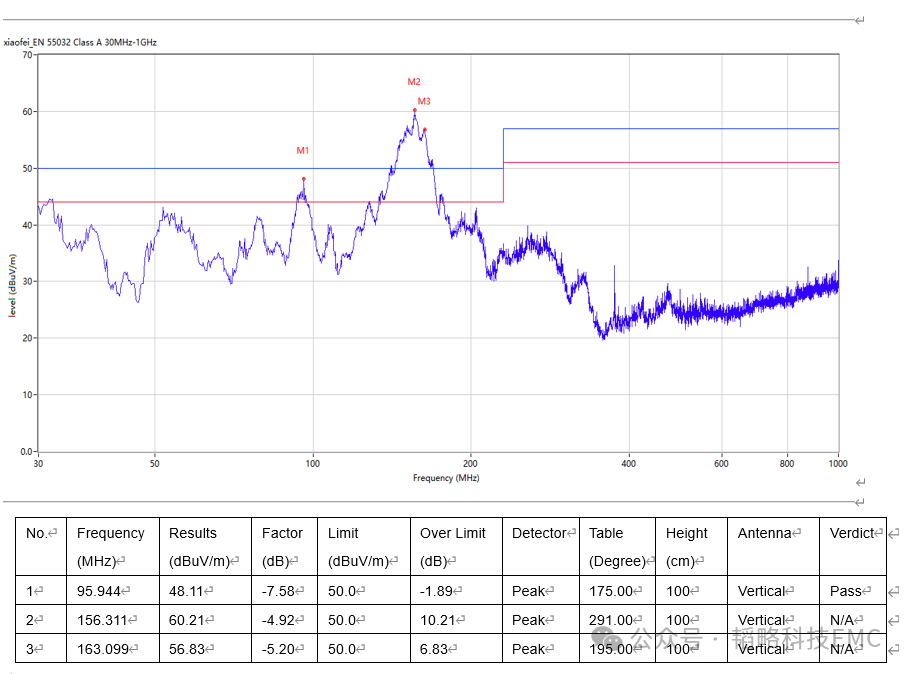

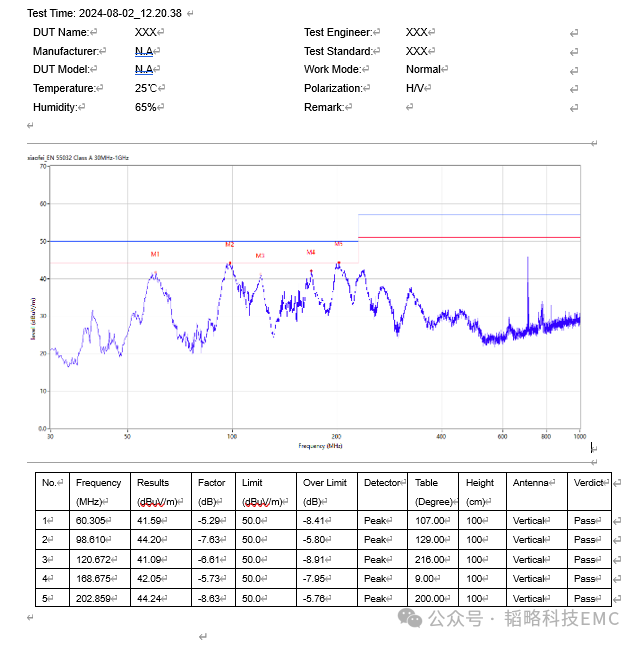

一般采用反激式電路方案,在實際使用過程會遇到雷擊或者工作環境惡劣,需要將變壓器兩端地做隔離來防雷擊,這樣就會導致噪聲走過的路徑變大。POE供電的工業攝像頭恰好就需要采用這樣的方案,由于用在工業上,所以測試等級是EN55032-classA,以下是摸底數據。

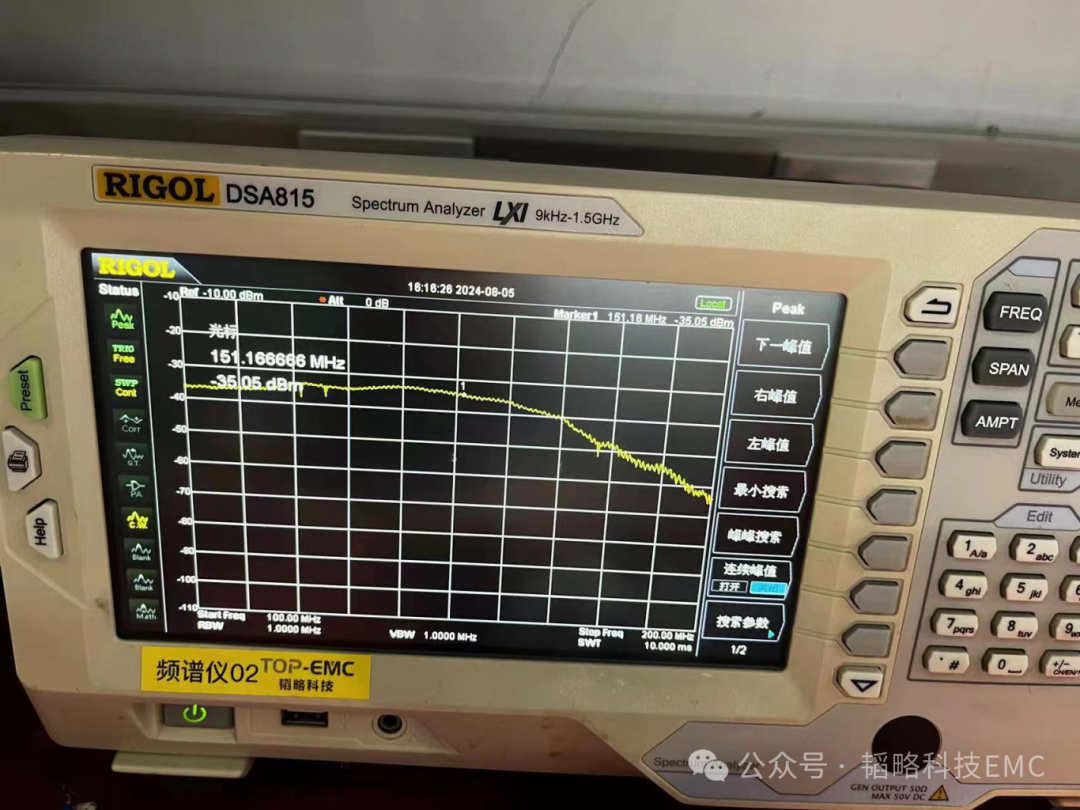

噪聲超標呈現包絡狀,初步判斷是電源噪聲問題。在近場,通過頻譜儀尋找噪聲源頭,發現在反激式變壓器和電源輸出端噪聲特別高,以下是近場頻譜儀噪聲掃描圖。同時在原理圖上,一級電源以后的供電部分由電源管理芯片PMIC供電,電壓和電流的突變并沒有反激電路的大,同時通過頻譜儀,也沒有發現對應的噪聲頻段,因此確定噪聲來源是反激式電源造成。

四整改措施

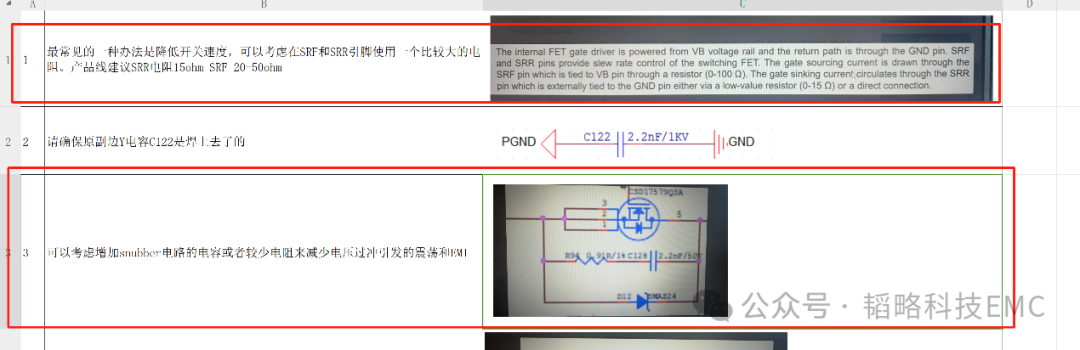

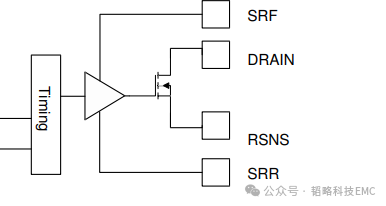

在前期電路設計中我們可以先參考原廠芯片EMI設計,預留抑制EMI的器件位置,后續我們整改就更方便,也有可能不用改板,只需要修改參數。以下是某POE芯片的EMI設計: 1.降低開關速度?讓我們看下芯片的內部電路圖

1.降低開關速度?讓我們看下芯片的內部電路圖

為何將SRF和SRR的電阻調大能抑制EMI呢?原來這兩個電阻分別是比較器的上拉和下拉電阻,增大后能使管子充放電時間變長,從而抑制EMI。2.snubber電路又稱阻尼電路,通過增加C和R將噪聲源的諧振改變,使電路進入過阻尼狀態,從而抑制EMI。實際上,該機器前期設計就有上述這兩個措施,依舊不能通過測試。因此我做了以下措施,整改措施分為三步:(1)針對150M左右超標頻率,對續流管D1輸出端對地并1nF電容,通過高頻電容將輸出回路減小;(2)對變壓器進行包屏蔽接前端地,減小噪聲對地阻抗;(3)在路徑上進行消耗,在輸入端加入(TLDCM4745-2-102TF-TA)共模濾波器吸收共模噪聲。以下是整改后數據:

五總結

EMC主要分為三要素:1.騷擾源;2.敏感源;3.耦合路徑。在騷擾源上,對續流二極管輸出端對地并1nF電容,通過高頻電容將輸出回路減小,對變壓器進行屏蔽接地。在耦合路徑上,在電源輸入端加共模濾波器,對噪聲進行消耗。在測試中,敏感源相當于測試天線。在前期電路設計中,可以提前預留抑制EMI的電阻電容,這樣能減少后期改板次數,加快量產時間。以上是小編的拙見,有任何錯誤,歡迎指出。

-

噪聲

+關注

關注

13文章

1132瀏覽量

47660 -

電源電路設計

+關注

關注

0文章

13瀏覽量

8019 -

emc

+關注

關注

170文章

4012瀏覽量

184778 -

反激電路

+關注

關注

7文章

46瀏覽量

22129

發布評論請先 登錄

相關推薦

評論