uPP是具有專用數據線和最小控制信號的并行接口,時鐘同步傳輸接口,支持單倍數據速率和雙倍數據速率傳輸。設計用于與8bit數據位寬的高速ADC、DAC或者FPGA進行連接。

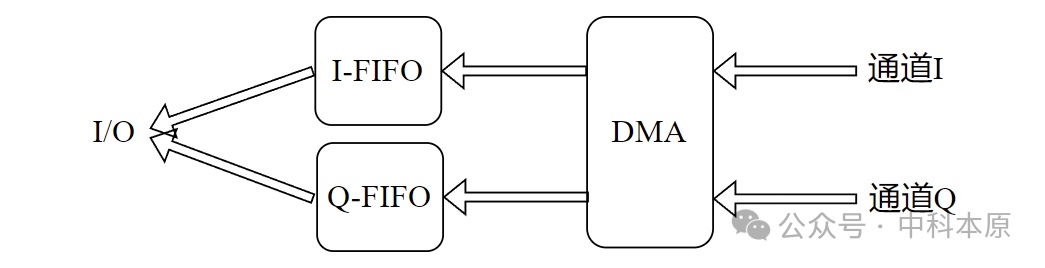

uPP內置獨立DMA控制器,保證數據傳輸期間最小化CPU開銷。DMA控制器有兩個DMA通道,支持數據交錯模式。同時uPP內部連接專用數據RAM(發送和接收各一個),每個大小512B。

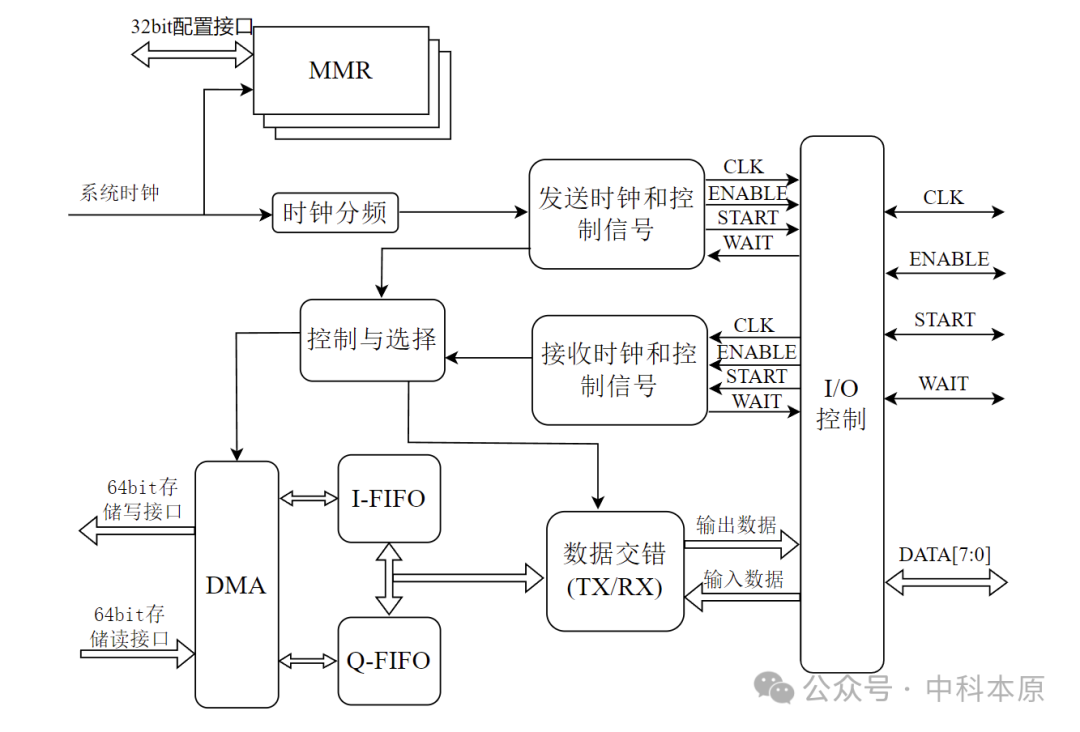

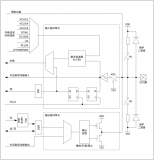

功能框圖

圖1 uPP功能框圖

傳輸模式

數據通道編號遵循:

?I/O通道標記為 “ I/O”

?DMA通道標記為 “通道 I” 和 “通道Q”

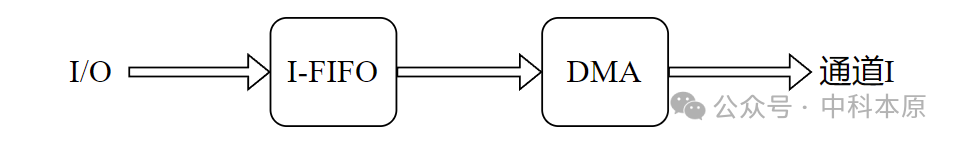

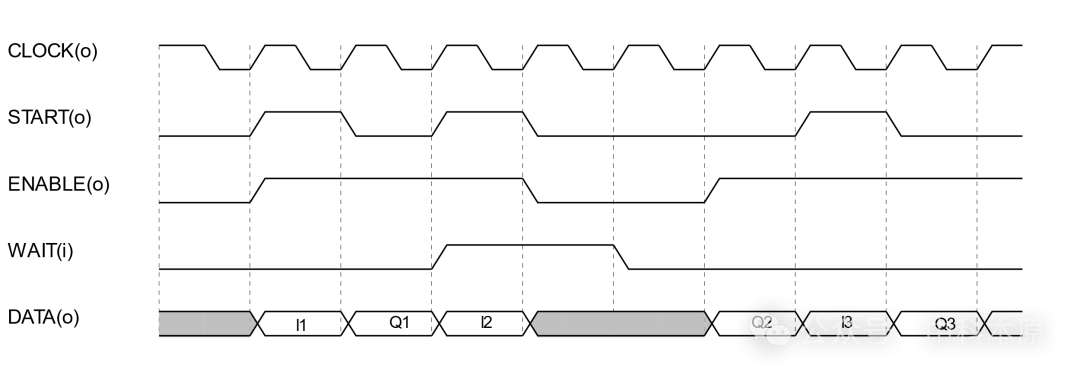

圖2說明了在SDR模式下或DDR模式下接收的數據流。只使用一個DMA通道(通道I)。

圖2 在SDR模式下或DDR模式下接收

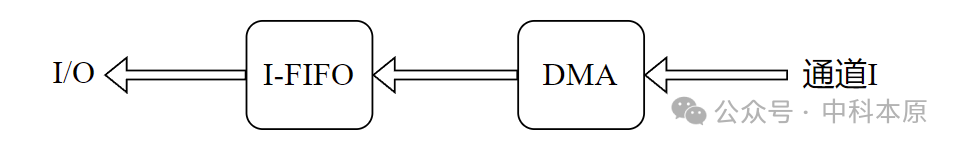

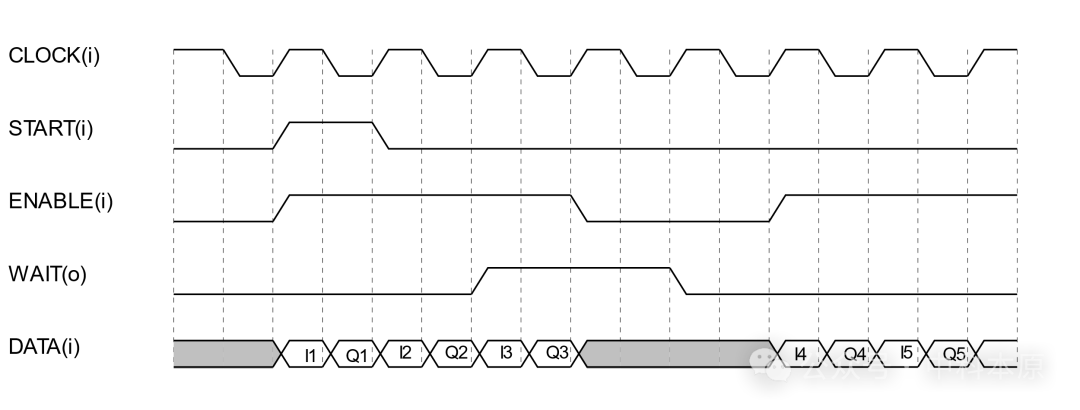

圖3說明了在SDR模式下或DDR模式下發送的數據流。只使用一個DMA通道(通道I)。

圖3 在SDR模式下或DDR模式下發送

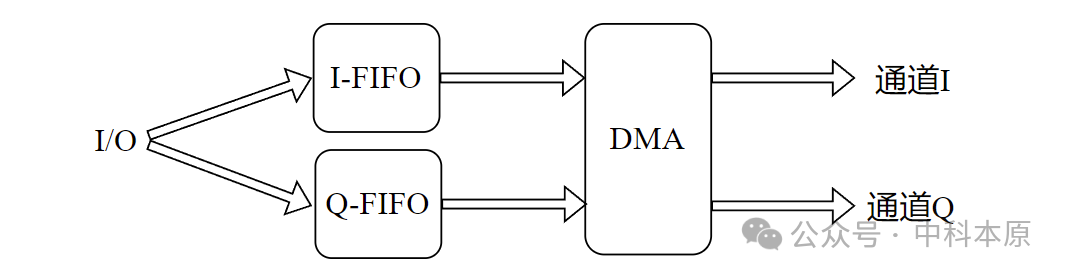

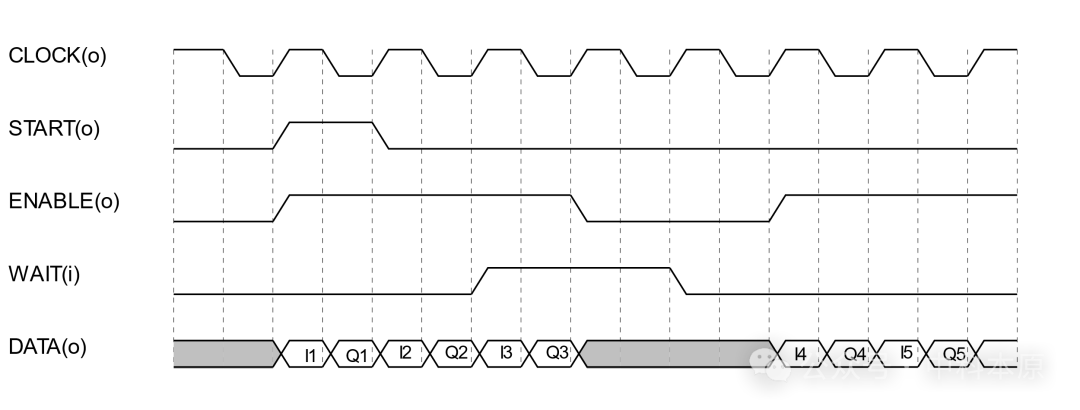

圖4說明了在DDR交錯模式下接收的數據流。使用兩個DMA通道(通道I和通道Q)。SDR交錯模式在接收模式下不可用。

圖4 在DDR交錯模式下接收

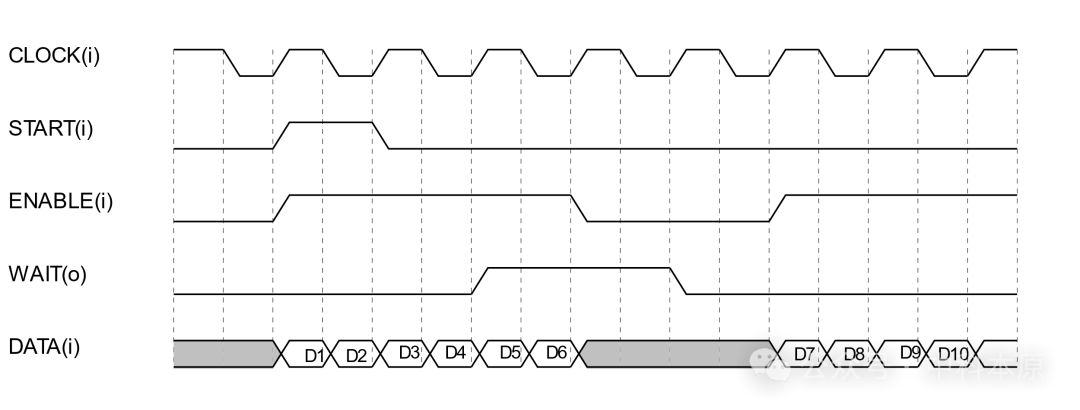

圖5說明了在SDR交錯模式下和DDR交錯模式下發送的數據流。使用兩個DMA通道(通道I和通道Q)。

圖5 在SDR交錯模式或DDR交錯模式下發送

DMA控制器描述

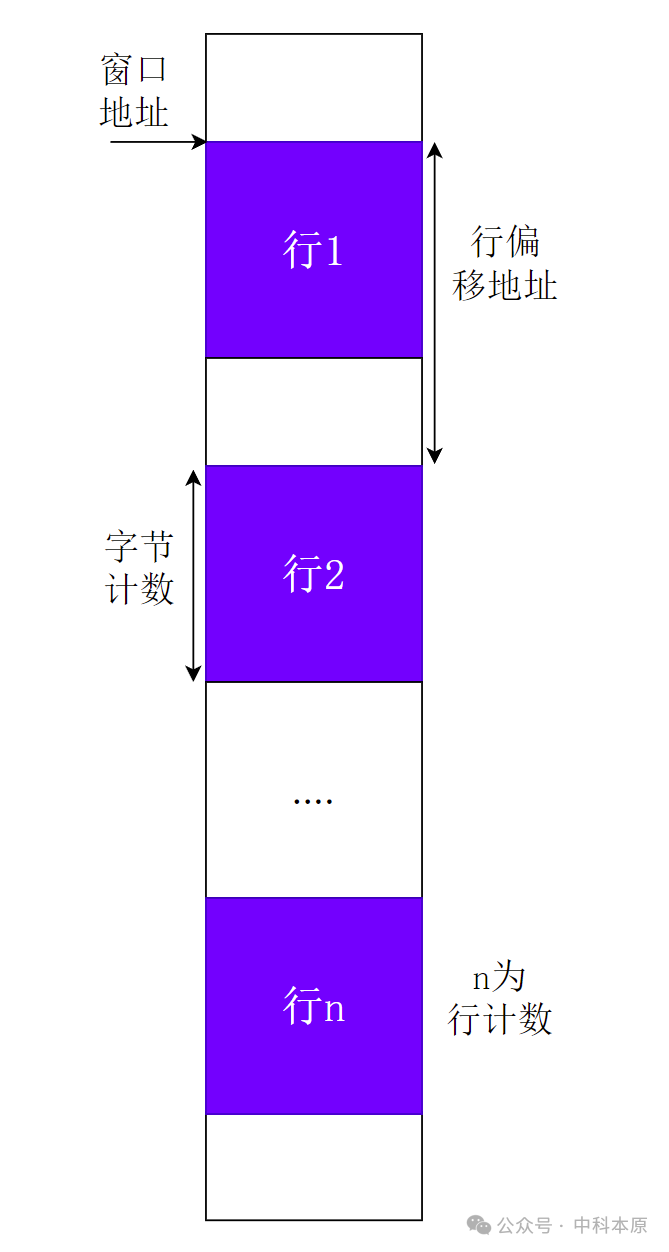

每個DMA通道需要配置四個參數:窗口地址,字節計數,行計數和行偏移地址。

窗口地址:uPP數據存儲器中的第一個字節的位置。uPP工作在接收模式時,DMA通道從I/O端口接收輸入數據寫入該地址。uPP工作在發送模式時,DMA通道從該地址開始讀取數據并將數據發送到I/O端口。窗口地址64bit邊界對齊(地址低三位為0)。

字節計數:每行的字節數。字節計數為偶數。

行計數:每個窗口的行數。傳輸的字節總數等于字節計數X行計數。

行偏移地址:連續行中第一個字節間的偏移地址。64bit對齊。

圖6顯示了典型的DMA窗口定義。

圖6 DMA窗口和存儲結構

其中行偏移地址=字節計數。讀取數據是存儲器中的大小等于行計數X字節計數的連續數據塊。

行偏移地址=0,說明數據由單行組成。發送模式下,DMA通道連續發送該行。接收模式下,DMA通道重復寫入該行存儲空間。

如果DMA通道被初始化并且空閑時,DMA通道I和通道Q的配置參數可以直接寫入相應描述寄存器中,DMA傳輸立即開始。同時每個DMA通道允許第二次配置在當前DMA傳輸仍在運行時排隊。每個DMA通道最多支持有一個傳輸進行和一個排隊,這可以保證傳輸在邊界上連續。但是DMA不支持自動重新寫入。DMA控制器總是以64字節對存儲器進行突發讀寫。

協議描述

接口信號說明

| 信號 | 說明 |

| CLK |

發送或接收時鐘 發送模式下輸出 接收模式下輸入 |

| START |

每行(幀)的第一個數據字 發送模式下輸出 接收模式下輸入 極性可編程 接收端選用信號,如果不使用,接收端可忽略 |

| ENABLE |

數據有效信號 發送模式下輸出 接收模式下輸入 極性可編程 接收端選用信號,如果不使用,接收端可忽略 |

| WAIT |

表示接收端沒有準備好接收數據。uPP在等待信號為高后的下一個時鐘周期停止發送數據 發送模式下輸入 接收模式下輸出 極性可編程 WAIT信號需要接收端置位一個完整時鐘周期 發送端選用信號,如果不使用,發送端可忽略 |

| DATA[7:0] | 數據信號 |

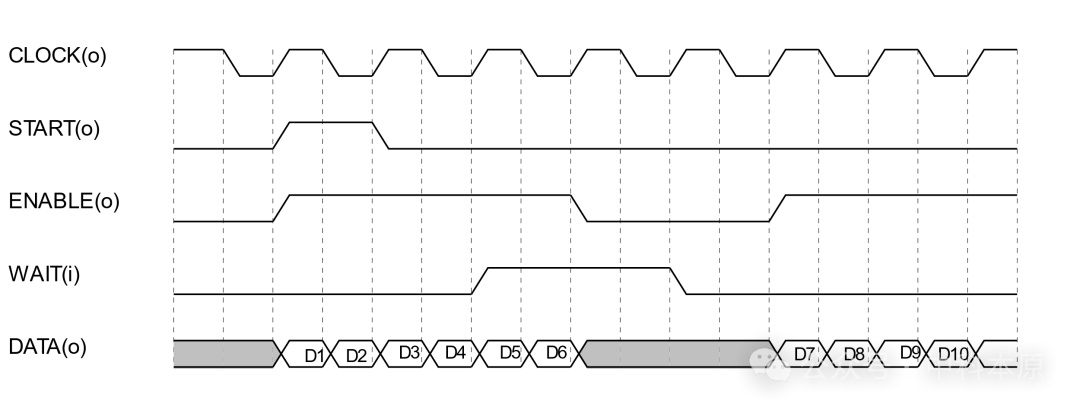

信號時序圖

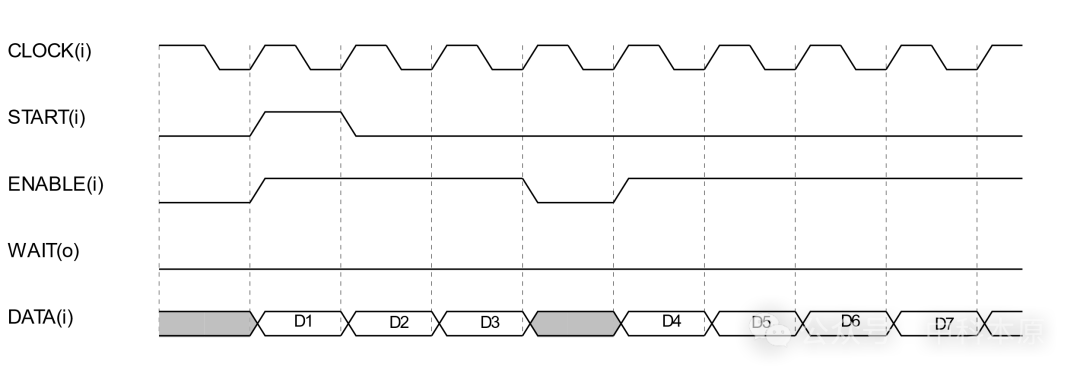

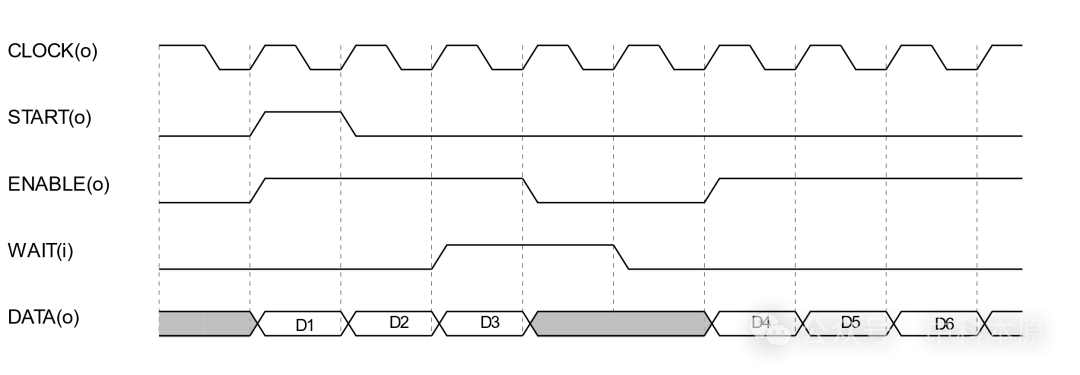

下圖中,標記(i)表示信號為輸入,標記(o)表示信號為輸出。時序圖中所有信號默認極性。

圖7 uPP在SDR模式下接收

圖8 uPP在SDR模式下發送

圖9 uPP在SDR交錯模式下發送

uPP在SDR交錯模式發送時,來自DMA通道I的每個數據字的START信號都有效。

圖10 uPP在DDR交錯模式下接收

圖11 uPP在DDR交錯模式下發送

圖12 uPP在DDR模式下接收

圖13 uPP在DDR模式下發送

初始化和操作

下面是初始化和配置uPP外設的分步說明。上電復位后:

1.配置管腳(如果有復用)

2.使能時鐘,配置時鐘分頻

3.進行外設復位

4.配置DMA通道控制,包括傳輸模式,傳輸方向,交錯模式和傳輸閾值

5.配置接口信號,控制信號使能,控制信號極性和數據信號空閑狀態

6.開啟中斷使能

7.使能uPP外設

8.配置通道參數,開始DMA傳輸

9.中斷事件查看與中斷處理

-

dsp

+關注

關注

555文章

8085瀏覽量

352732 -

控制器

+關注

關注

113文章

16630瀏覽量

180689 -

并行接口

+關注

關注

0文章

32瀏覽量

15399 -

并行端口

+關注

關注

0文章

13瀏覽量

10782

原文標題:DSP通用并行端口uPP技術詳解

文章出處:【微信號:中科本原,微信公眾號:中科本原】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于c6748的upp問題

uPP_B_TO_A庫Tronlong.DSP.C6000.C6748.Driver.uPP.lib是否有源代碼?

uPP數據出現誤碼

怎么使用DA模塊通過upp傳回dsp端?

FPGA與DSP通過upp通信參數設置對嗎?

FPGA與DSP如何進行通過UPP通信

dsp通過upp接收數據時出現問題的解決辦法?

C6748的UPP使用時,必須是帶著DSP/BIOS操作系統嗎?

PC機與DSP之間的并行通訊技術

TMS320C672x DSP通用主機端口接口(UHPI)參考指南

評論