日本東京工業大學(Tokyo Tech)的研究人員開發了一種用于處理單元(processing units)和內存堆疊的創新三維集成技術,可以實現目前“世界上最高的性能”,為更快、更高效的計算鋪平了道路。

這種創新的堆疊架構被命名為“Bumpless Build Cube 3D”(簡稱BBCube 3D),它實現了比最先進的內存技術更高的數據帶寬,同時還最大限度地降低了比特訪問所需的能量。

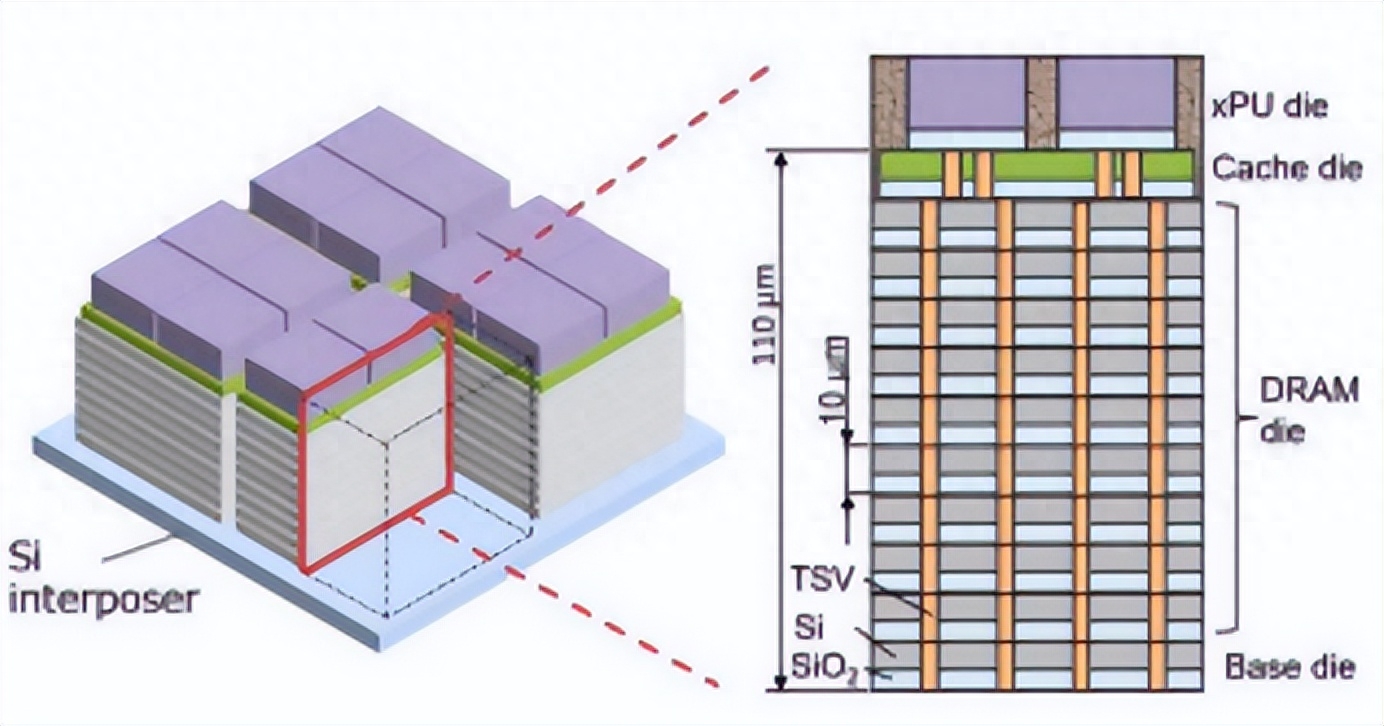

BBCube 3D技術采用了一種堆疊設計,其中處理單元(xPU)位于多個互連內存層(DRAM)之上。通過用硅通孔(TSV)代替電線,可以縮短連接長度,從而獲得更好的整體電氣性能。

在當今的數字時代,工程師和研究人員不斷提出新的計算機輔助技術,這些技術需要處理單元(即PU,例如GPU和CPU)與存儲芯片之間有更高的數據帶寬。現代帶寬密集型應用的一些例子包括人工智能、分子模擬、氣候預測和遺傳分析等。

然而,為了增加數據帶寬,必須在PU和存儲器之間添加更多線路,或者提高數據速率。第一種方法在實踐中很難實現,因為上述組件之間的傳輸通常發生在二維中,使得添加更多線路變得困難棘手。另一方面,提高數據速率則需要增加每次訪問一個比特數據所需的能量,稱為“比特訪問能量”(bit access energy),這也是具有挑戰性的。

幸運的是,日本東京工業大學的一組研究人員現在可能已經找到了解決這個問題的可行方案。在最近舉行的IEEE 2023 VLSI技術和電路研究研討會上,Takayuki Ohba教授及其同事報告了他們的關于BBCube3D技術的研究成果(論文題目:Bumpless Build Cube 3D:Heterogeneous 3D Integration Using WoW and CoW to Provide TB/s Bandwidth with Lowest Bit Access Energy)。該技術有望解決上述問題,從而實現更好的PU和動態隨機存取存儲器(DRAM)集成。

BBCube 3D最引人注目的方面是實現了PU和DRAM之間的三維連接,而不是二維連接。該團隊通過使用創新的堆疊結構實現了這一壯舉,其中PU芯片位于多層DRAM之上,所有層均通過硅通孔(TSV)互連。

BBCube3D的整體架構緊湊,沒有采用典型的焊料微凸塊,并且使用TSV代替較長的電線,這些都有助于實現低寄生電容和低電阻,也提高了整體設計在各個方面的電氣性能。

此外,研究人員實施了一項涉及四相屏蔽輸入/輸出(IO)的創新策略,以使BBCube 3D具有更強的抗噪聲能力。他們調整了相鄰的IO線的時序,使它們始終彼此不同步,這意味著它們永遠不會同時改變其值。這減少了線路之間的串擾噪聲,并使整體設計運行更加穩健。

該研究團隊評估了他們的BBCube 3D架構的速度,并將其與現有兩種最先進的內存技術:DDR5和HBM2E進行了比較。Ohba教授在解釋實驗結果時表示:“由于BBCube 3D 的低熱阻和低阻抗,可以緩解3D集成中典型的熱管理和電源問題。BBCube 3D有望實現每秒1.6TB的帶寬,比DDR5高30倍,比HBM2E高4倍。在比特訪問能量方面,BBCube 3D的比特訪問能量分別是HBM2E的1/20和DDR5的1/5。”

審核編輯:湯梓紅

-

半導體

+關注

關注

334文章

27687瀏覽量

221457 -

DRAM

+關注

關注

40文章

2325瀏覽量

183762 -

異構集成

+關注

關注

0文章

34瀏覽量

1914

發布評論請先 登錄

相關推薦

SciChart 3D for WPF圖表庫

騰訊混元3D AI創作引擎正式發布

騰訊混元3D AI創作引擎正式上線

裸眼3D筆記本電腦——先進的光場裸眼3D技術

西門子推出Innovator3D IC,用于 3D IC 設計、驗證和制造的多物理場集成環境

Stability AI推出Stable Video 3D模型,可制作多視角3D視頻

Adobe提出DMV3D:3D生成只需30秒!讓文本、圖像都動起來的新方法!

高分工作!Uni3D:3D基礎大模型,刷新多個SOTA!

BBCube3D以混合3D方法實現異構集成

BBCube3D以混合3D方法實現異構集成

評論