在過去的幾年里,數據領域陸續出現重大技術突破,特別是在數據傳輸和處理速度方面。AI(人工智能)、IoT(物聯網)、5G 等科技日益成熟且應用廣泛,其中PCI Express(PCIe)技術在這些產業中扮演著重要的角色。PCIe 5.0的出現引起數據領域的高度關注,因為它在性能和速度方面帶來重大改進。伴隨著最新的PCB模擬技術,PCIe 5.0可以徹底改變我們對數據處理的認知和使用方式。

究竟什么是PCIe?

PCIe 是?種高速串行計算機擴展總線標準,作為計算機系統不同組件之間的數據傳輸,例如CPU與GPU或其它加速處理器之間傳輸數據都依賴這條PCIe 主要干道。以目前開發主流的PCIe 5.0 為例,其傳輸速度可達32 GT/s,是PCIe 4.0的兩倍。由于在16個通道的配置中能夠傳輸128GB/s(每秒千兆字節),PCIe 5.0不僅可以提供高速、可靠的數據傳輸通道,同時還具備了靈活的擴展性以滿足大量信息的處理需求,包括人工智能、機器學習和信息分析。

延伸閱讀:服務器市場洞察,最為產業期待的下一個十年

PCIe 5.0的核心優勢

1.增強的速度和性能相較于PCIe 4.0,PCIe 5.0最顯著的優勢是增強的速度和性能。2倍速度的提升將轉化為更快的數據傳輸率,減少延遲,并提高整體系統性能。

2.更加擴大的帶寬PCIe 5.0具有更高的帶寬,可以實現更高的數據吞吐量。讓它成為需要實時處理大量數據的理想選擇,如:數據中心、高性能計算或電競游戲等。

3.向下兼容PCIe 5.0能夠向下兼容PCIe 4.0和PCIe 3.0,意味著它可以與既有接口的設備一起運作。確保用戶可以升級他們的系統,而不必更換所有的組件。

PCIe 5.0之PCB設計及挑戰

負責制定PCI Express的PCI-SIG組織(Peripheral Component Interconnect Special Interest Group),于2017年便啟動了PCIe 5.0規格制定的工作,并于2019年發布了該項標準。

PCIe 5.0的通道損耗設計在16GHz的頻率點應小于36 dB,在顧及通道損耗規范及訊號質量的同時,PCB的成本管控也必須一并考慮,搭配合適的PCB材料與銅箔等級,可有效地降低開發成本,并在訊號完整性與成本之間取得平衡點。

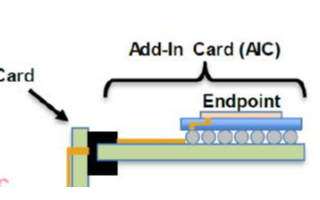

以典型只有一個連接通道的PCIe5為例,扣除掉前端CPU Chip約9 dB損耗、后端的PCIe標準卡(Add-in card)約9.5 dB損耗及保留10%設計余量約3.6 dB,其PCB板端能運用的損耗值只剩約13.9 dB。一般服務器主板的PCIe走線長度約落在8inch(203.2mm)左右,若采用標準的PCB板材及銅箔,其PCB損耗約在18.5 dB,遠遠大于設計規范,因此需要搭配更高階的PCB板材及銅箔,成本也將增加,因此準確的掌握高階PCB板材的損耗將有助于成本的優化。

什么是PCB電性模擬?

PCB電性模擬是指透過軟件來模擬和分析印刷電路板(PCB)行為的過程。透過多種軟件可以模擬出電路板的電性表現結果,在進入生產之前先找出潛在問題,進一步解決問題、優化設計。例如,模擬電路板對不同電壓、電流和頻率的反應。通過模擬PCB的行為,工程師可以發現問題并改善電路板的性能及可靠度。

PCB材料損耗驗證與檢測

PCIe 5.0電性損耗量測

綜觀整個業界,PCB電性損耗驗證具有多種不同方式,過往的主流驗證方法是采用SET2DIL (Single-Ended TDR to Differential insertion loss) 或SPP (Short Pulse Propagation)二者,但是這兩種方法,受到鉆孔(Via)和鉆孔殘斷(Via Stub)的寄生電容與電感的影響,在高頻時容易導致量測不準確。于是Intel 開發了Delta-L分析手法,省去繁雜的校正步驟并扣除前述的寄生效應 (Parasitic Effect),并偕同治具供貨商開發專屬的探針頭,建立一套標準的PCB材料損耗 (Loss Per Inch) 量測手法。USI已建立此量測流程,此舉將有助于在高速傳輸接口設計領域中,確保產品質量與最終產品的檢測。

USI環旭電子憑借在云端及存儲設備擁有多年的設計經驗,PCB設計期間提供完整的設計服務及電性模擬服務,利用3D電磁場模擬軟件進行PCB阻抗優化,可降低多重反射對訊號的影響,同時也運用時域電路分析工具,有效解決干擾、衰減、串音等相關問題,確保終端的訊號可符合PCI-SIG的標準規范。

延伸閱讀:鎖定邊緣運算領域,搶攻 AI 商機

PCB高速訊號設計檢查與模擬

由USI環旭電子自主開發的自動化設計模擬系統(Front-End Design Simulation) ,已成功應用在各大芯片廠商(Intel、AMD、Qualcomm、MTK…等)的設計規范(Design Guideline), 主要用于確保電源設計的完整性。此外,也開發自動檢查PCB布線Design Rule,除了有效取代人工繁瑣的檢查及大大縮短開發時程之外,自動化檢查帶來快速且優良的PCB布線質量。例如:多數服務器的訊號線有2000~5000條,難以人眼確認布線質量,經過自動化的檢查,更能加以確保并提升PCB布線質量。

PCIe現在即是未來

PCIe的重點向來都聚焦在提高帶寬和數據傳輸速度。PCI-SIG 在2021的開發者大會正式發布PCI 6.0的規范,調變技術由NRZ (Non-Return-to-Zero) 改為PAM4 (Pulse Amplitude Modulation),傳輸速率可到達64GT/s。此外,PCIe 6.0還引入一些新功能,如PAM4編碼,它可以實現四級信令以提高數據傳輸速率,以及低延遲的前向糾錯(FEC), 可以同步改善錯誤檢測和糾正,以實現更快和更可靠的數據傳輸。來年(2022) 隨即著手制定PCIe 7.0 標準,讓傳輸速率又再度翻倍至128GT/s的高性能。

另一個趨勢是PCIe在汽車和工業系統等新應用中的使用越來越多。這些系統需要高速數據傳輸和實時處理,使PCIe成為其通信和控制系統的理想選擇。PCIe 5.0和PCB模擬技術的結合可以為下一代技術提供更高的性能和更快的數據處理速度。

設計師可以利用這些技術來減少設計缺陷,提高系統性能,并在更短的時間內將新產品推向市場。雖說 PCIe 5.0要大規模投入到消費市場還需要一段時間,但USI 會持續精進高速接口相關技術的設計及優化以提供高競爭力的產品來滿足客戶的需求。

FAQs1.PCIe 5.0和PCIe 4.0之間有什么區別?

與PCIe 4.0相比,PCIe 5.0提供2倍的傳輸速度以及更擴大的帶寬。這使得PCIe 5.0更適合于處理海量數據和實時應用。

2.PCB模擬技術能夠幫助什么?

利用PCB模擬技術,你可以更好地了解設計中的潛在問題,并在實際生產前對其進行優化。這有助于提高系統性能,降低成本,并節省時間。

3.PCB損耗驗證是必要的嗎?

是的,藉由測量PCB的電性損耗結果,可以評估信號在PCB線路中的衰減情況,確定是否需要采取進一步的設計優化措施,如改變PCB材料、線路布局或采用增強信號傳輸技術等。當PCIe 5.0 傳輸速度達到了32 GT/s,損耗量測是重要且必要的步驟。

4.PCB模擬技術能否檢測出所有的設計缺陷?

PCB模擬技術可以檢測出大多數設計缺陷,但并不是萬無一失。重要的是,要結合使用模擬和物理測試,以確保你的設計在性能和可靠性方面得到優化。

5.PCB高速訊號設計自動化檢查與模擬與過去差異為何?

一般服務器多數使用Intel or AMD平臺,訊號線有2000~5000條,難以人眼確認布線品質。因此,透過開發并導入自動化檢查,更能加以提升PCB的布線質量。電源完整性模擬必須等PCB設計近乎完成才能開始執行,而模擬設定皆需一定人工時間,因此導入電源完整性模擬自動化,即能在有限時間內,達到優化電源設計進而符合設計目標,確保各芯片組可以正常工作。

編輯:黃飛

-

pcb

+關注

關注

4341文章

23336瀏覽量

404855 -

模擬技術

+關注

關注

17文章

469瀏覽量

40126 -

PCIe

+關注

關注

16文章

1300瀏覽量

84358

原文標題:【PCIe 5.0】深入PCB設計及驗證 掌握高速傳輸核心

文章出處:【微信號:環旭電子 USI,微信公眾號:環旭電子 USI】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

[討論]PCB設計面臨的新挑戰

【漢普觀點】PCB設計面臨的挑戰

PCB設計之電容

PCB設計軟件(Sprint Layout) 5.0 漢化版

什么是 PCIe 5.0? PCIe 5.0規范以及挑戰

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

評論