本文主要給大家分享一下PCIe5.0的發(fā)展歷程、以及在設(shè)計(jì)、仿真中一些挑戰(zhàn)和如何進(jìn)行仿真。--蔣修國(guó)

1、PCIE 發(fā)展歷程及PCIE 5.0的發(fā)布

作為PC系統(tǒng)中最重要的總線(xiàn), PCI Express由Intel于2001年提出,用于替代PCI總線(xiàn),以滿(mǎn)足更高的帶寬和吞吐量需求。

由上面的圖表可以看到,為了滿(mǎn)足日益增長(zhǎng)的信息傳遞速率,每一代PCIE標(biāo)準(zhǔn)在速度上都幾乎是成倍增長(zhǎng)。

目前,由于 PCIE 4.0擁有相較于前代PCIE 3.0兩倍的16GT/s傳輸速率,其被廣泛應(yīng)用于超算,企業(yè)級(jí)高速存儲(chǔ),網(wǎng)絡(luò)設(shè)備等產(chǎn)品中。而去年年中,AMD發(fā)布了支持PCIE4.0的7nm銳龍3000系列處理器,正式將PCIE4.0帶入了消費(fèi)級(jí)平臺(tái)。

隨著人工智能技術(shù)的飛速發(fā)展,對(duì)運(yùn)算能力的需求不斷提升,高速總線(xiàn)也面臨著更大的挑戰(zhàn)。因此,在PCIE 4.0發(fā)布僅僅兩年后,PCI-SIG便于2019年5月發(fā)布了PCIE 5.0規(guī)范。相比較之前PCIE 4.0的16GT/s,PCIE5.0 將信號(hào)速率翻倍到了32GT/s,x16雙工帶寬更是接近128GB/s。極高的信號(hào)速率,使得PCIE5.0能夠更好的支持對(duì)吞吐量要求高的高性能設(shè)備,如用于AI的GPU,網(wǎng)絡(luò)設(shè)備等等。

2019年底,Intel便出貨了支持PCIE 5.0的Agilex FPGA,也拉開(kāi)了PCIE 5.0時(shí)代的大幕。

2、PCIE 5.0主要指標(biāo)

由于速率的翻倍,PCIE 5.0在均衡,損耗等指標(biāo)上,與前代均有較大差別。

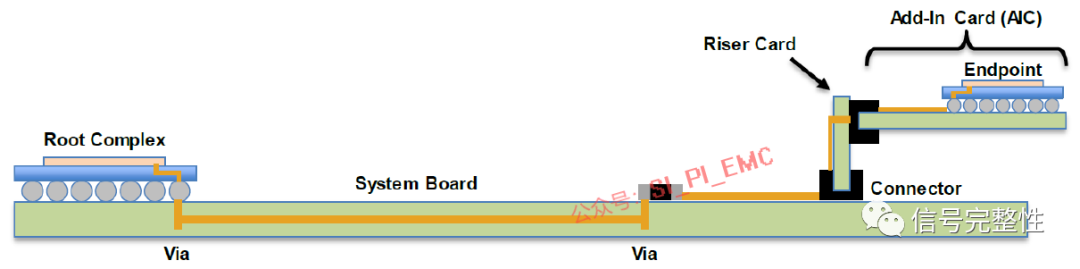

(1)、拓?fù)浣Y(jié)構(gòu)

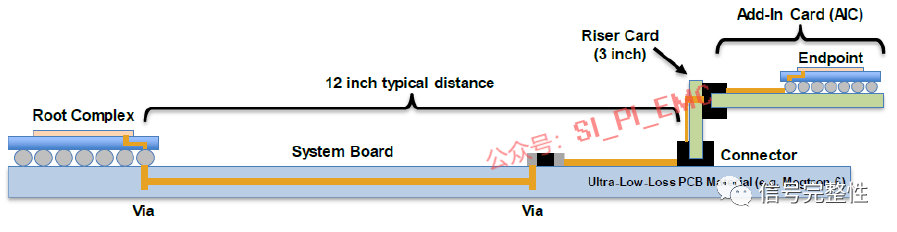

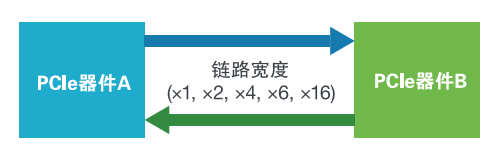

上圖展示了基本的雙連接器PCIE拓?fù)浣Y(jié)構(gòu),這種結(jié)構(gòu)被廣泛應(yīng)用于服務(wù)器、存儲(chǔ)和加速器系統(tǒng)。

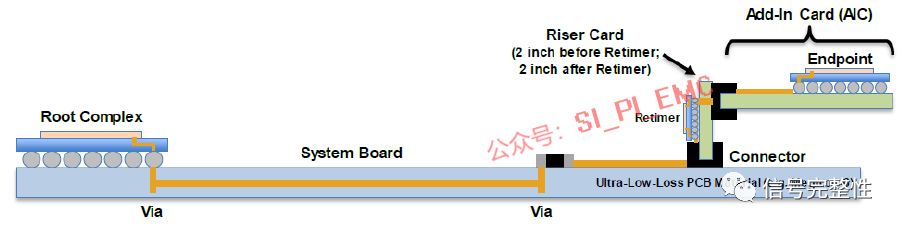

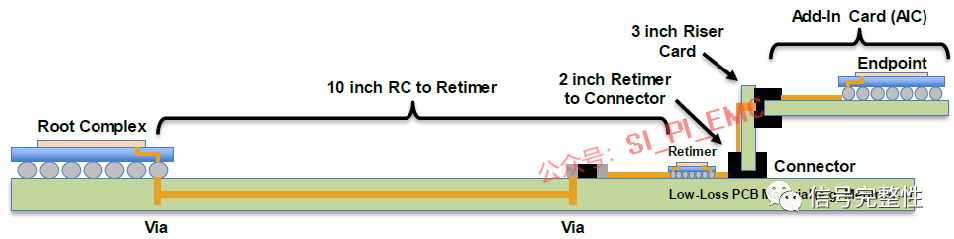

在PCIE 5.0中,當(dāng)線(xiàn)路損耗過(guò)大,或使用多個(gè)連接器時(shí),可以在信號(hào)拓?fù)渲屑尤隦e-timer以提高系統(tǒng)信號(hào)質(zhì)量。關(guān)于加入Re-timer后的拓?fù)浣Y(jié)構(gòu),在之后的章節(jié)會(huì)有具體的介紹。

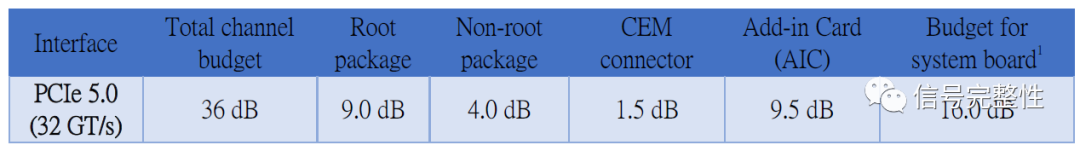

(2)、損耗

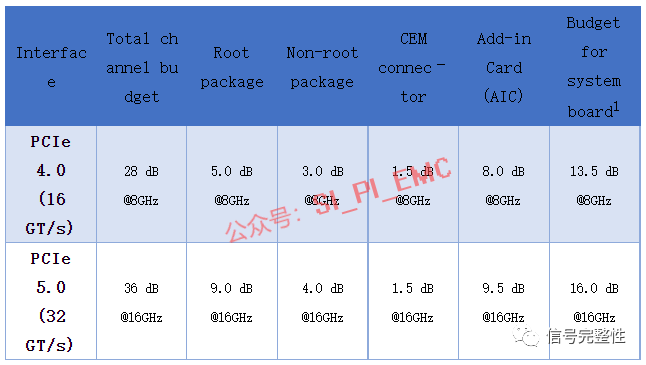

上述拓?fù)浣Y(jié)構(gòu)中包括各種損耗組件,而PCIe 5.0已經(jīng)為這些組件制定了如下的損耗預(yù)算。可以看到,整體通道的損耗在16GHz時(shí)不能高于36dB。

1System Board budget includes the baseboard,riser card, the baseboard-to-riser-card, and PCIe card electromechanical (CEM)form factor connectors.

(3)、均衡

PCIE 5.0在發(fā)射端和接收端都使用了均衡技術(shù)來(lái)提高信號(hào)質(zhì)量。

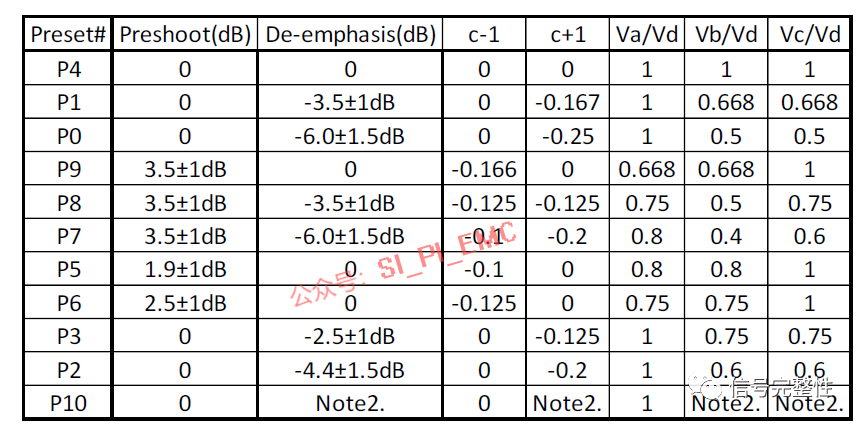

A.Tx EQ

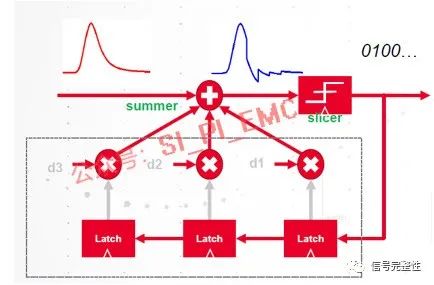

在發(fā)射機(jī)端,PCIE 5.0沿用了PCIE 4.0的三階FIR濾波器(如下圖所示),通過(guò)對(duì)信號(hào)高頻分量的抬高和低頻分量的減少來(lái)彌補(bǔ)這一影響。

B.RX EQ

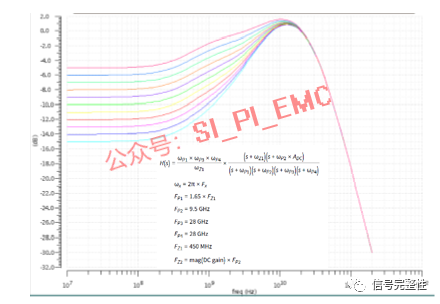

與Tx均衡不同,在接收端,PCIE 5.0對(duì)PCIE 4.0的均衡進(jìn)行了升級(jí),二階CTLE和三階DFE被用來(lái)替換前代的一階CTLE和二階DFE,以應(yīng)對(duì)更高的信號(hào)速率,使閉合的眼圖張開(kāi)。通過(guò)CTLE可以減小由更高頻通道損耗造成的影響。而DFE則可以進(jìn)一步減少I(mǎi)SI帶來(lái)的影響。

2-order CTLE

3-tap DFE

通過(guò)使用以上技術(shù),也促使PCIE 5.0在PCIE 4.0的基礎(chǔ)上實(shí)現(xiàn)了速度翻倍(這并不是是唯二的技術(shù)),同時(shí),其信號(hào)延遲和編碼開(kāi)銷(xiāo)也大幅優(yōu)化。

3、PCIE 5.0 設(shè)計(jì)面對(duì)的挑戰(zhàn)

(1)、無(wú)源通道設(shè)計(jì)

在2.2中介紹到PCIE 5.0對(duì)整體信道的損耗有嚴(yán)格的要求。下表中對(duì)比了PCIE4.0在16GT/s速率下,與PCIE 5.0在32GT/s速率下的損耗要求。

可以看到,雖然PCIE 5.0的速率提高了一倍,損耗要求卻沒(méi)有下降太多。這意味對(duì)設(shè)計(jì)的損耗控制要求提高了幾乎一倍。使用低損耗或超低損耗的材料的固然使減少損耗的一個(gè)方法,但其在降低了損耗的同時(shí),也大大提高了產(chǎn)品的成本。如果能夠在使用較低成本材料的同時(shí),通過(guò)對(duì)疊層,傳輸線(xiàn)結(jié)構(gòu)的調(diào)整,達(dá)到符合要求的通道性能,無(wú)疑能使產(chǎn)品獲得更大的競(jìng)爭(zhēng)力。平衡成本與性能之間的關(guān)系,將成為工程師們不得不面對(duì)的挑戰(zhàn)。

(2)、Repeater使用

PCIe 4.0對(duì)通道損耗的要求是8GHz小于28dB,而PCIE5.0則是16GHz小于36dB,若大于這些值,接收機(jī)不能保證可以正確地解出信號(hào)。控制損耗固然是解決方法之一,但對(duì)于損耗過(guò)大的設(shè)計(jì),受到產(chǎn)品結(jié)構(gòu),尺寸和成本的限制,留給工程師的優(yōu)化空間往往十分有限,因此Repeater被使用來(lái)給予看似絕望的設(shè)計(jì)一線(xiàn)生機(jī)。

Repeater的目的是為了避免抵達(dá)接收機(jī)的信號(hào)惡化太嚴(yán)重以至于無(wú)法被正確識(shí)別,在信道中提前對(duì)信號(hào)做處理。以PCIe 5.0為例,因成本的考慮不能用太貴的板材,若初步的通道設(shè)計(jì)差損48dB@16GHz,為了讓信號(hào)可以正確地傳送,可以選擇在通道中間加上Repeater,這樣就可以把通道的設(shè)計(jì)拆成兩半,Repeater和RX各分擔(dān)24dB@16GHz的差損。關(guān)于Repeater的使用我們會(huì)在后面作更深入的探討。

Repeater是由一個(gè)RX加上TX芯片所組成,而依信號(hào)處理方式的不同分為兩類(lèi),Retimer和Redriver。

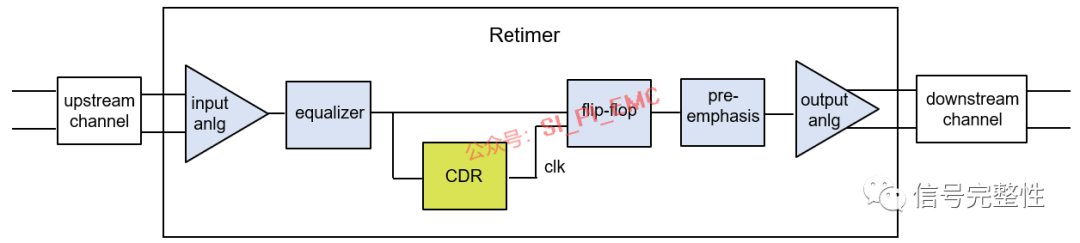

A.Retimer

有CDR(Clock Data Recovery,時(shí)鐘恢復(fù)),若TX到該Retimer之前的通道設(shè)計(jì)符合Retimer的規(guī)范,則信號(hào)可以被正確的還原,之前的通道損耗和抖動(dòng)都可以被Retimer消除,因此就像TX的位置被移動(dòng)到Retimer,對(duì)SI工程師來(lái)說(shuō),信號(hào)就可以走得更遠(yuǎn)了。

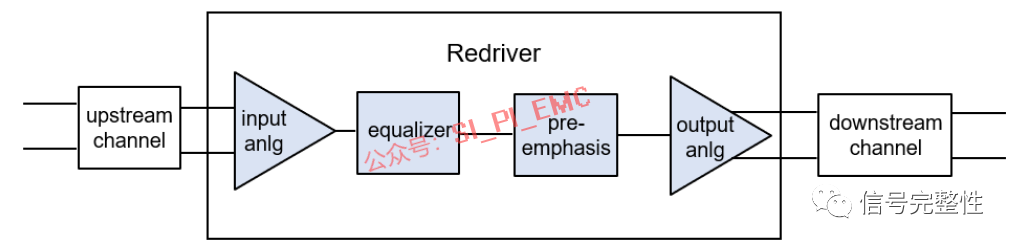

B. Redriver

沒(méi)有CDR,因此只能補(bǔ)償信號(hào)的衰減,無(wú)法去除抖動(dòng)。

4、應(yīng)對(duì)PCIE5.0設(shè)計(jì)挑戰(zhàn)

針對(duì)以上提到的設(shè)計(jì)難題,就需要一套非常完整的仿真方案來(lái)解決。

(1)、無(wú)源通道設(shè)計(jì)

在前面介紹到,無(wú)源通道的損耗是PCIE 5.0設(shè)計(jì)中的一大挑戰(zhàn)。為了平衡成本與性能,工程師需要進(jìn)行大量的預(yù)研,在layout之前評(píng)估出適合的PCB材料,傳輸線(xiàn)和疊層結(jié)構(gòu)等。在使設(shè)計(jì)符合協(xié)議要求的同時(shí),盡可能降低產(chǎn)品的成本。

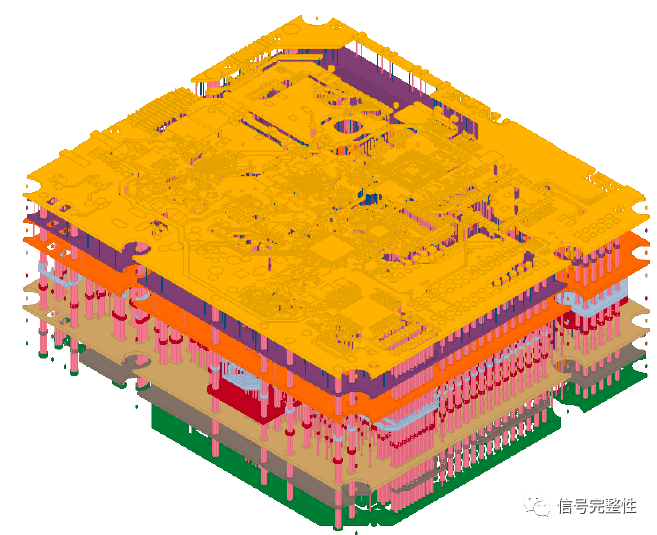

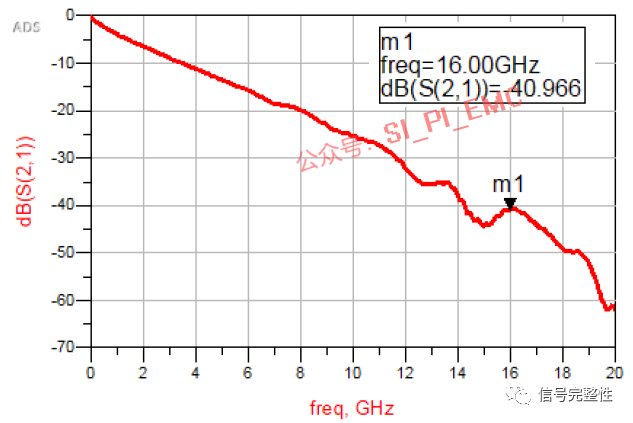

而針對(duì)設(shè)計(jì)完成的layout,工程師需要準(zhǔn)確的提取其中的S參數(shù),用于驗(yàn)證通道損耗是否符合設(shè)計(jì)要求。由于PCIE 5.0的奈奎斯特頻率高達(dá)16GHz,工程師需要一款能夠在高頻情況下準(zhǔn)確高效提取通道S參數(shù)的工具。

在ADS中,CILD和SIPro兩個(gè)工具,可以分別滿(mǎn)足layout前、后的設(shè)計(jì)驗(yàn)證要求。

A.傳輸線(xiàn)結(jié)構(gòu)設(shè)計(jì)(Pre-layout)

工程師在正式layout之前,需要預(yù)先確定設(shè)計(jì)的疊層,材料和走線(xiàn)結(jié)構(gòu)。為了控制產(chǎn)品的成本,超低損耗材料往往無(wú)法很普遍的被使用。受到材料的約束,工程師更需要通過(guò)合理的疊層和線(xiàn)寬,線(xiàn)間距設(shè)置,降低通道的損耗。

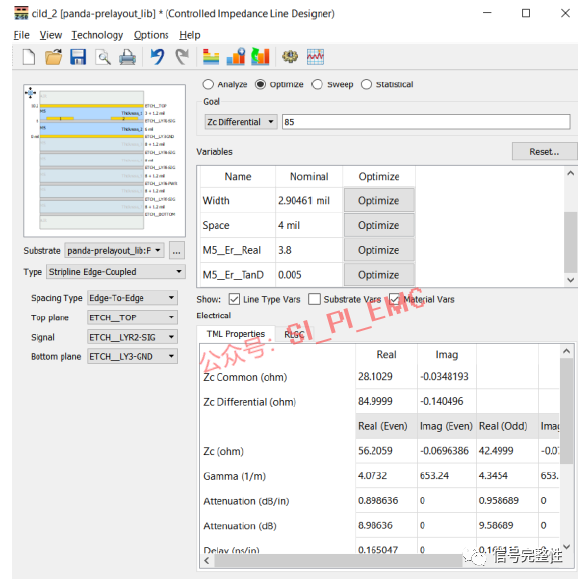

這里,以Dk=3.8, Df=0.005的低損耗材料,core/pp介質(zhì)厚度3/6mil,85ohm阻抗為例,對(duì)比不同的傳輸線(xiàn)線(xiàn)寬與線(xiàn)間距對(duì)損耗的影響。

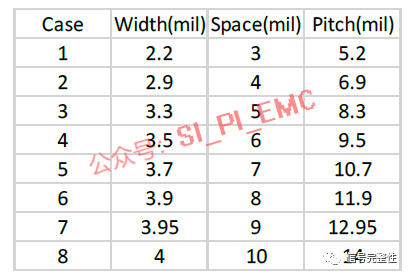

在ADS中,CILD是專(zhuān)門(mén)用于在layout前構(gòu)建傳輸線(xiàn)結(jié)構(gòu),并仿真其主要參數(shù)的工具。在CILD中,可以通過(guò)設(shè)定目標(biāo)阻抗,使用優(yōu)化模式自動(dòng)優(yōu)化出符合阻抗要求的線(xiàn)寬和線(xiàn)間距。如下圖中,統(tǒng)計(jì)出了8種不同的線(xiàn)寬及線(xiàn)間距組合。

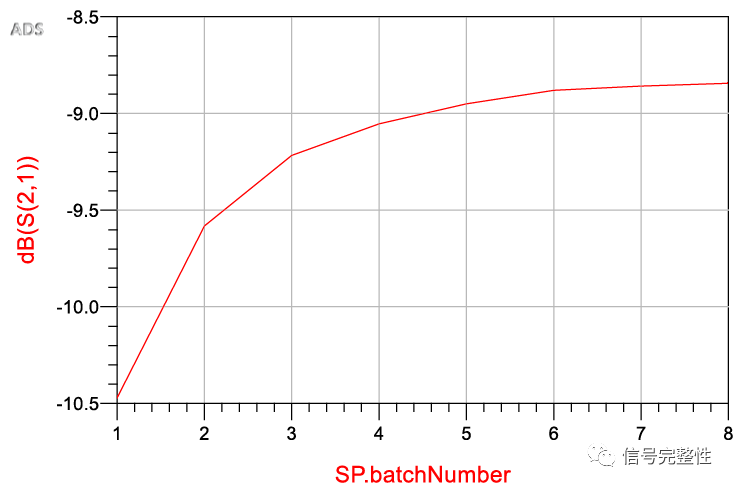

CILD的傳輸線(xiàn)模型還可以導(dǎo)入ADS原理圖中,通過(guò)Batch Simulation對(duì)各種線(xiàn)寬線(xiàn)間距的組合進(jìn)行掃描。如下圖所示,對(duì)8種傳輸線(xiàn)結(jié)構(gòu)都進(jìn)行了仿真,得到了16GHz時(shí)的損耗。可以發(fā)現(xiàn)隨著線(xiàn)寬的增寬,傳輸線(xiàn)的損耗逐步下降。4/10的情況下,相較2.2/3損耗下降了超過(guò)1.5dB。 考慮到case 4~7的pitch雖然增加了近50%,但是損耗僅減小了0.3dB。選擇Case4或Case5的情況進(jìn)行l(wèi)ayout,既減少了損耗,又可以保證足夠的走線(xiàn)空間。

除了線(xiàn)寬與線(xiàn)間距,CILD也可以考慮材料參數(shù)和疊層的變化。通過(guò)ADS CILD的使用,用戶(hù)可以對(duì)傳輸線(xiàn)結(jié)構(gòu)進(jìn)行快速評(píng)估,獲得設(shè)計(jì)參考。

B.Layout EM驗(yàn)證(Post-layout)

完成layout之后,工程師需要使用電磁仿真工具提取PCB的S參數(shù)對(duì)設(shè)計(jì)進(jìn)行驗(yàn)證。由于PCIE 5.0的高速率,工程師使用的電磁仿真工具需要能在高頻段也能快速準(zhǔn)確提取出S參數(shù)。同時(shí),設(shè)計(jì)中往往會(huì)使用背鉆來(lái)解決過(guò)孔stub的問(wèn)題,因此也要求電磁仿真器能準(zhǔn)確提取該部分信息。

ADS SIPro是一款專(zhuān)用于PCB仿真的電磁仿真工具。其使用獨(dú)有的混合算法,可以快速提取信號(hào)走線(xiàn)(包含過(guò)孔)的頻域模型,驗(yàn)證設(shè)計(jì)完成的layout性能。這一頻域模型可以直接轉(zhuǎn)換成ADS 的原理圖,用于電路仿真,如時(shí)域瞬態(tài)仿真,通道仿真等。同時(shí),ADS 提供了過(guò)孔設(shè)計(jì)工具ViaDesigner,使用FEM進(jìn)行過(guò)孔結(jié)構(gòu)的仿真設(shè)計(jì)。

(2)、Repeater應(yīng)用

前文提到過(guò)Repeater的工作原理,工程師往往需要判斷Repeater的使用時(shí)機(jī)和方式。通過(guò)ADS 通道仿真器,可以對(duì)是否使用Repeater以及Repeater的擺放位置進(jìn)行規(guī)劃與驗(yàn)證。

A.是否需要使用Repeater

這里提供兩種判斷方式,方法I比較簡(jiǎn)單但較粗糙,方法II適用于獲得芯片的AMI模型的情況,可以得到很接近真實(shí)的眼圖,建議初期先用方法I做系統(tǒng)規(guī)劃,再用方法II來(lái)驗(yàn)證。

I.損耗評(píng)估法

通過(guò)S參數(shù)仿真,比較通道損耗(包括封裝)和PCIe規(guī)范的損耗標(biāo)準(zhǔn),若通道損耗超過(guò)標(biāo)準(zhǔn),則建議使用Repeater。

II.統(tǒng)計(jì)眼圖法

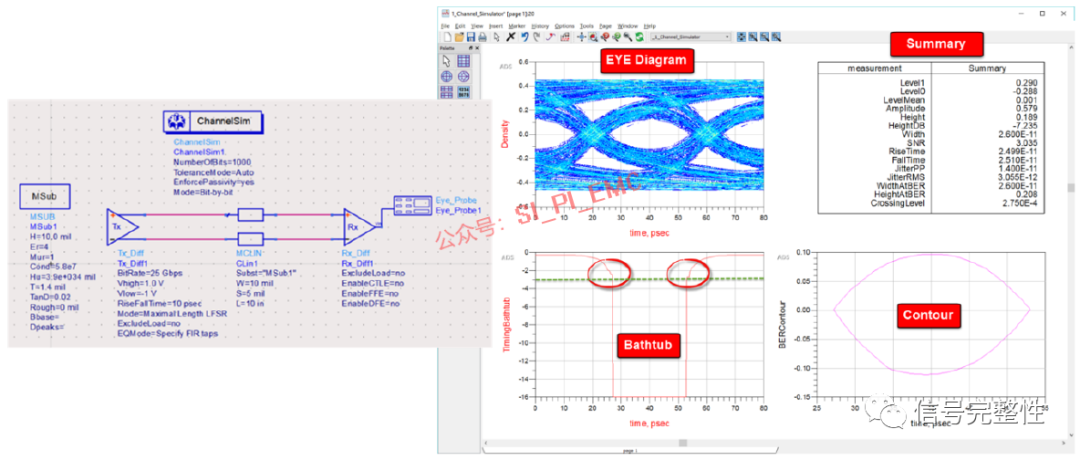

ADS通道仿真器(ChannelSim),用于分析經(jīng)過(guò)通道后的信號(hào)質(zhì)量。通道仿真器具有兩種模式,Bit-by-bit和Statistical,是目前串行接口鏈路的主流仿真工具。

以下探討是否有AMI模型的判斷方式。

-沒(méi)有AMI模型

把通道的S參數(shù)帶入通道仿真器(ChannelSim),并設(shè)定PCIe協(xié)會(huì)對(duì)芯片規(guī)范的Jitter和EQ(De-emphasis, CTLE, DFE),找出最好的EQ組合,若該組合不能符合協(xié)會(huì)訂定的眼圖張開(kāi)標(biāo)準(zhǔn)(5.0, 眼高15mV,眼寬0.3UI),建議使用Repeater。

-有AMI模型

不用自己設(shè)定Jitter和EQ,且眼圖張開(kāi)標(biāo)準(zhǔn)有可能會(huì)比協(xié)會(huì)訂定的還寬松(例如眼高10mV,眼寬0.2UI,比協(xié)會(huì)規(guī)范的EYE MASK還小),這取決于RX芯片的算法能力,建議參考RX AMI模型的應(yīng)用文件。若仿真得到的眼圖張開(kāi)不能符合該RX AMI建議的值,建議使用Repeater。

B.Repeater的擺放位置

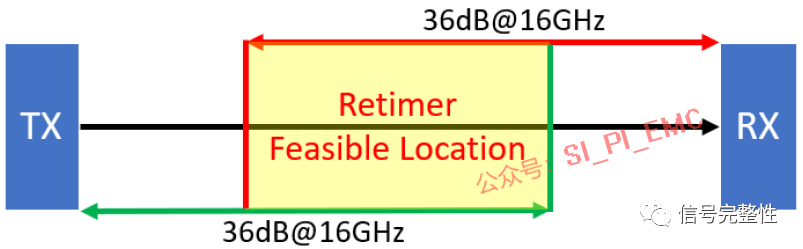

Retimer

由于Retimer送出的信號(hào)已經(jīng)將信號(hào)時(shí)鐘對(duì)準(zhǔn),可以把Retimer位置視為新的TX位置,并針對(duì)協(xié)會(huì)對(duì)損耗的規(guī)范來(lái)擺放Retimer。通過(guò)損耗評(píng)估法,得到以下的黃色區(qū)間是適合擺放Retimer的位置,在該區(qū)間符合TX to Retimer和Retimer to RX之間的通道差損小于36dB@16GHz。

一旦決定Retimer的位置后,可以將兩段S參數(shù)(TX to Retimer和Retimer to RX)連同Retimer AMI模型用通道仿真器來(lái)判斷最后RX的眼圖是否符合該RX的要求,若不符合要求,可以前后調(diào)整一下Retimer位置后,再用通道仿真驗(yàn)證,直到RX的眼圖符合該RX的要求為止。

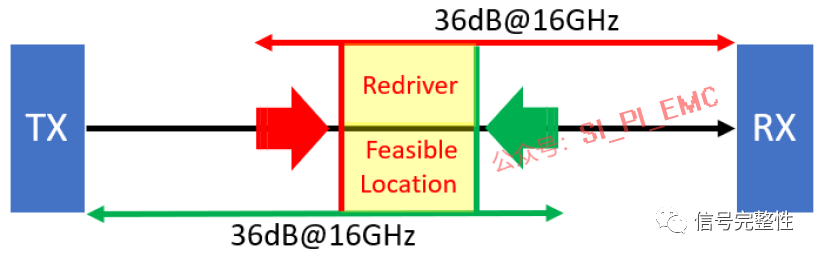

Redriver

由于沒(méi)有CDR,因此在評(píng)估時(shí)無(wú)法將Redriver的位置視為新的TX位置,因?yàn)閺腞edriver送出的信號(hào)會(huì)帶有之前信道累積的Jitter。有了這樣的認(rèn)知,我們?cè)谂袛郣edriver的位置就應(yīng)該更加保守,類(lèi)似下圖。

確定位置后,一樣也需要透過(guò)信道仿真器來(lái)判斷RX的眼圖是否符合RX規(guī)范。

Repeater加在Baseboard還是Riser Card上?

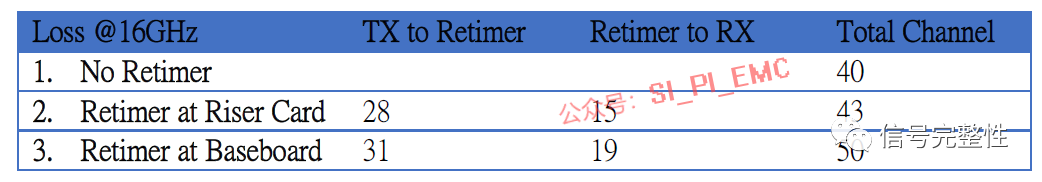

以下兩種常見(jiàn)的Repeater擺放位置(Topology 2 and 3),最后仿真結(jié)果也都遠(yuǎn)優(yōu)于協(xié)會(huì)規(guī)范,這表示在系統(tǒng)設(shè)計(jì)上還有許多優(yōu)化空間,例如可以選擇較低成本的板材,或是走線(xiàn)可以走得更長(zhǎng)。

Topology 1 - 無(wú)Retimer,Baseboard用Ultra-Low-Loss板材

Topology 2 - Retimer加在Riser card上,Baseboard用Ultra-Low-Loss板材

Topology 3 - Retimer加在Baseboard上,Baseboard用Low-Loss板材

(5)、PCIe 5.0仿真實(shí)例

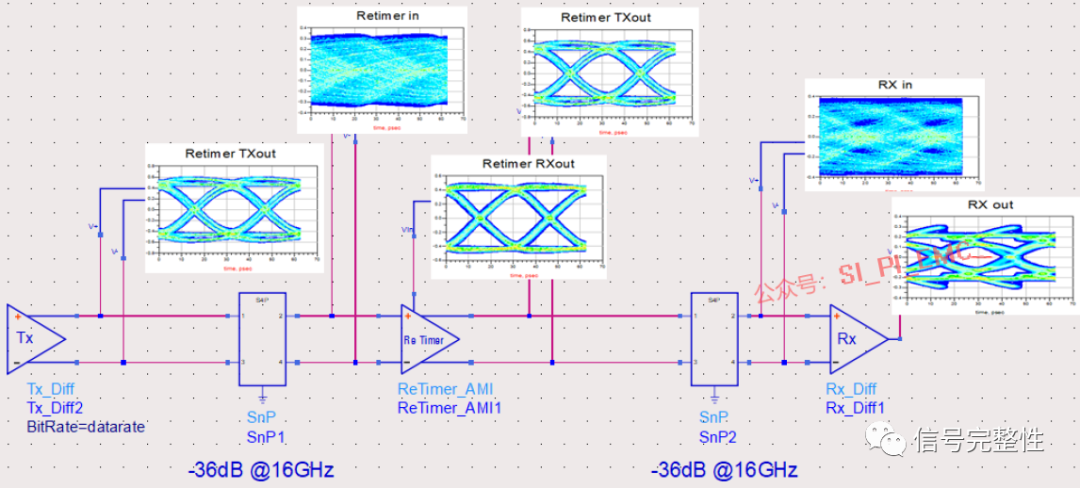

以下是我們基于PCIe 5.0的規(guī)范設(shè)定的Retimer測(cè)試模板。通過(guò)仿真結(jié)果我們可以看到,即使進(jìn)到Retimer前的眼圖已經(jīng)完全關(guān)閉(Retimer in),但通過(guò)CDR以及均衡器的處理,再次送出張開(kāi)的眼睛(Retimer TXout),來(lái)協(xié)助RX正確地顯示眼圖(RX out)。

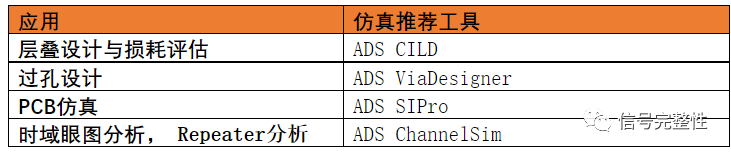

(6)、PCIe5.0仿真推薦配置

審核編輯:湯梓紅

-

仿真

+關(guān)注

關(guān)注

50文章

4097瀏覽量

133701 -

PCI

+關(guān)注

關(guān)注

4文章

669瀏覽量

130319 -

總線(xiàn)

+關(guān)注

關(guān)注

10文章

2890瀏覽量

88159 -

PCIe

+關(guān)注

關(guān)注

15文章

1241瀏覽量

82745 -

PCIe5.0

+關(guān)注

關(guān)注

0文章

17瀏覽量

1400

原文標(biāo)題:PCIe 5.0 設(shè)計(jì)面臨的挑戰(zhàn)以及仿真案例

文章出處:【微信號(hào):SI_PI_EMC,微信公眾號(hào):信號(hào)完整性】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

硬盤(pán)開(kāi)啟PCIe 5.0時(shí)代

移動(dòng)電視射頻技術(shù)面臨什么挑戰(zhàn)

PCIe 5.0的接口設(shè)計(jì)有多難?

機(jī)器開(kāi)發(fā)人員面臨哪些軟件挑戰(zhàn)以及硬件挑戰(zhàn)?如何去應(yīng)對(duì)這些挑戰(zhàn)?

PCIe 4.0 SSD尚未起飛,就要迎戰(zhàn)速度翻倍的5.0

PCIe 5.0時(shí)代正式拉開(kāi)序幕

什么是 PCIe 5.0? PCIe 5.0規(guī)范以及挑戰(zhàn)

microchip全新的PCIe 5.0交換芯片怎么樣

是德科技發(fā)布新款端到端的PCIe5.0/6.0測(cè)試解決方案

泰克PCIe Gen 5 Tx一致性測(cè)試解決方案

PCIe 5.0之PCB設(shè)計(jì)及挑戰(zhàn)

PCIe 5.0 SSD不用風(fēng)扇會(huì)怎么樣?

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

PCIe 5.0設(shè)計(jì)面臨的挑戰(zhàn)以及仿真案例

PCIe 5.0設(shè)計(jì)面臨的挑戰(zhàn)以及仿真案例

評(píng)論