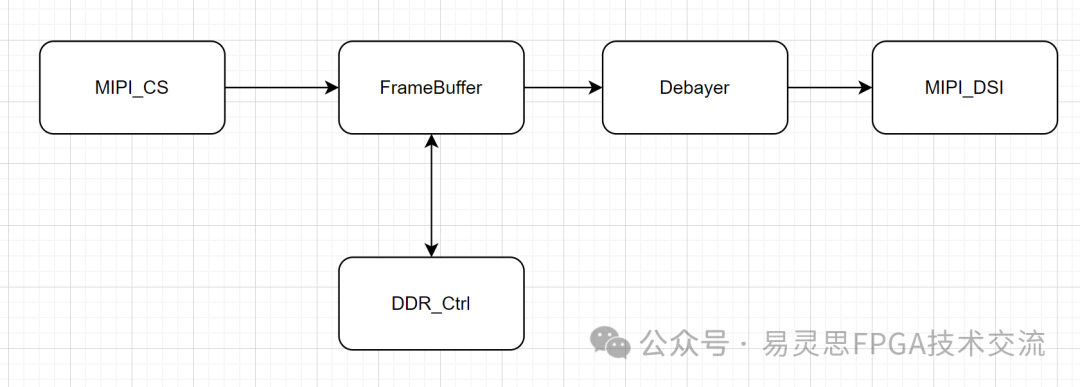

最近陸續有客戶在評估易靈思的Ti180。Ti180的MIPI 2.5G是硬核。今天做一個簡單的移植來試驗下MIPI DSI 驅屏。

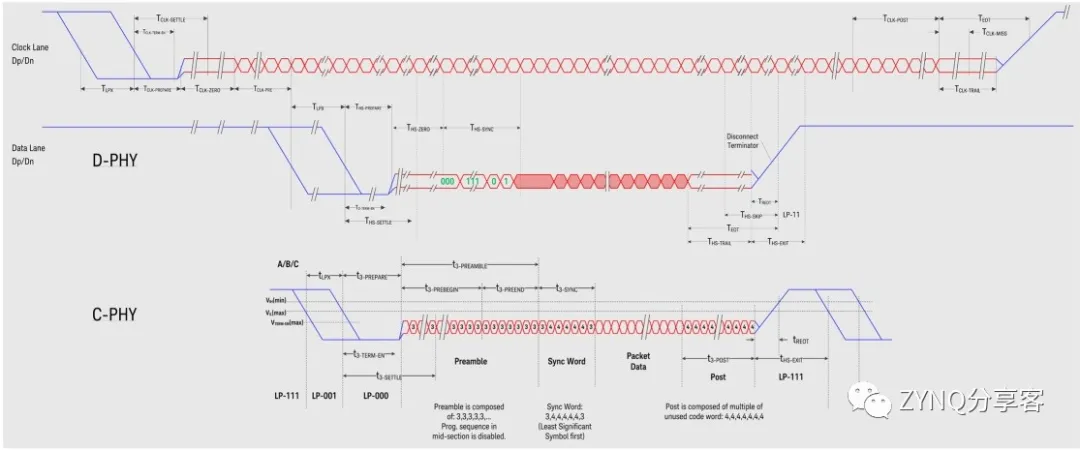

MIPI 2.5G DPHY簡介

Ti180有4組MIPI 2.5G DPHY,每組是4組數據和一個時鐘。

支持MIPI DPHY1.2版本協議

支持ULPS.

支持連續與非連續時鐘模式。

支持反向傳輸。

MIPI TX 參考時鐘來源?

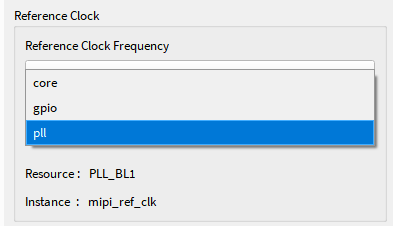

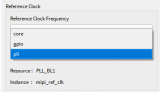

MIPI TX的參考有GPIO,PLL輸出和core三個來源。

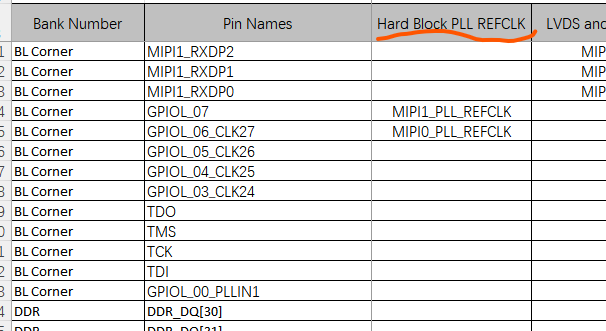

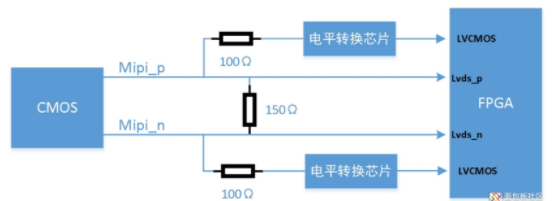

(1)如果是GPIO 輸入,請參考pinout設計文件里有一欄Hard Block PLL REFCLK.就是指如果硬件如果參考時鐘從外部供給時指定的管腳。這是在硬件設計時需要注意的,需要提前規劃好時鐘的來源。

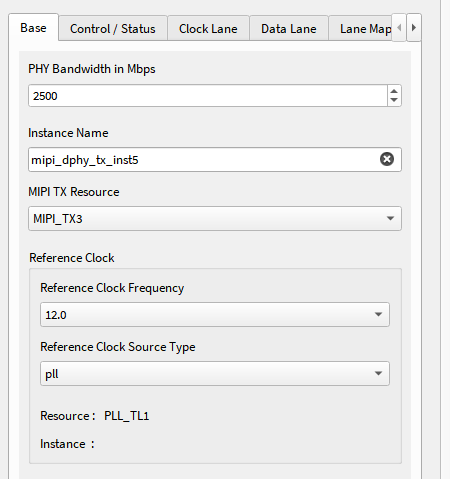

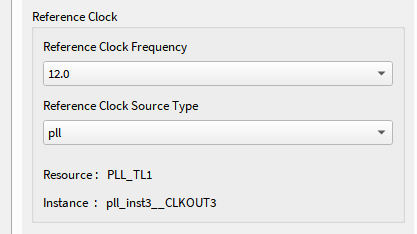

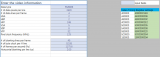

(2)如果把時鐘參考設置為PLL又應該怎么使用,明顯IP核上并沒有給出任何設置PLL參考源的選項。PLL的參考只能是固定的。當我們選擇PLL的時候,下圖的Resource會指定需要用那個PLL,如下圖的PLL_TL1,這時我們就必須要使用PLL_TL1,但是選擇的是PLL_TL1的輸出的那個時鐘呢?在下圖的Instance后面還是空白的。

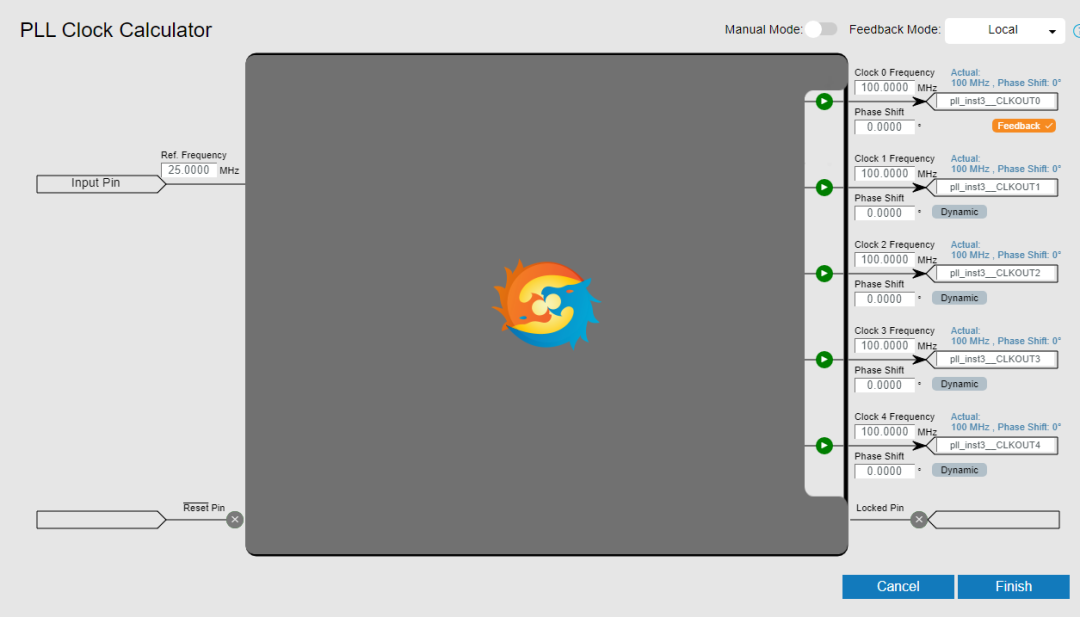

于是我們新建一個PLL_TL1,并把所有的輸出時鐘都打開。

當我們再次查看DPHY的參考時,發現Instance已經不再為空,為是指定了pll_inst__CLKOUT3.說明用的是PLL_TL1的clk_out3,所以在設計時也要注意對該時鐘的規劃。

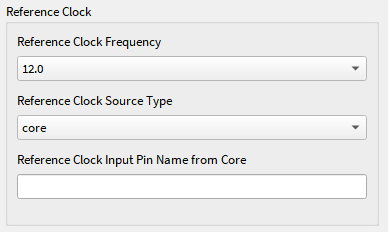

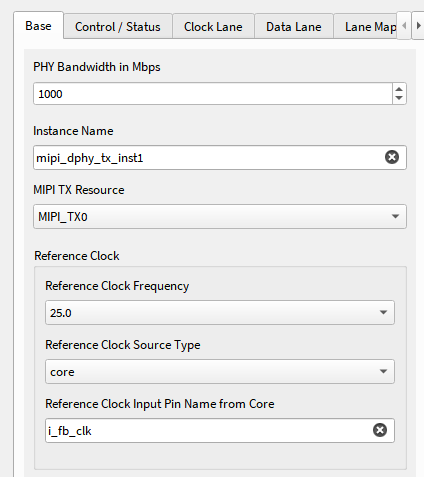

(3)如果時鐘選擇Core呢?這時時鐘可以手動輸入想選擇的時鐘,無論是從GCLK輸入的還是PLL輸出的。

另外需要提醒要注意時鐘頻率的選擇哦。

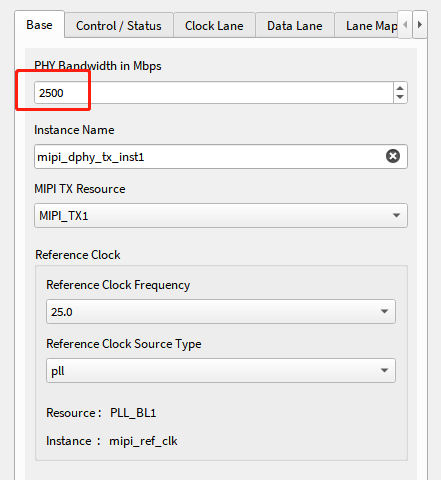

如果要修改速率DPHY部分應該做什么呢?

(1)修改PHY Bandwidth參數。

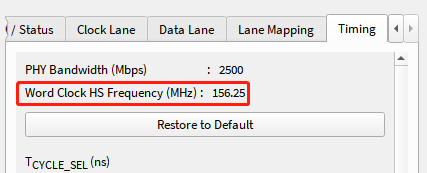

(2)在Timing中也可以確認

(2)修改clk_byte_HS ,該時鐘要求為phy_clk_byte_HS的兩倍。

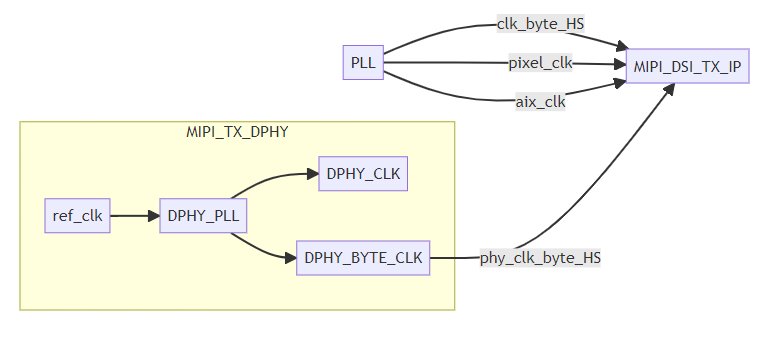

時鐘方案

該demo中MIPI DSI TX的IP部分時鐘主要如下,

(1)在DPHY中會生成一個phy_clk_byte_HS給DSI TX IP。

(2)同時還會通過PLL輸出一個clk_byte_HS 給DSI TX IP,該時鐘要求是phy_clk_HS的兩倍,demo上這兩個時鐘并不同源。

(3)另外PLL還提供了MIPI TX IP需要的pixel_clk和axi_clk。

移植說明:

該demo是MIPI DPHY 4lane 1G輸出。內部產生了一個彩條。

(1)MIPI屏速率是1Gbps4 lane.

(2)分辨率是1920x1080

(3) demo來自易靈思提供的DSI TX demo。

(4)目前demo板沒有預留MIPI的GPIO參考,為了方便就直接通過Core時鐘來驅動(PLL輸入還是要指定位置的),實際這個時鐘也是從PLL輸出的。

(5)屏使用的是易靈demo板中提供的手機屏。

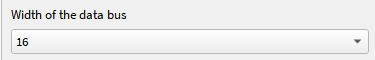

(3)目前MIPI DSI TX IP里面有兩個參數,clk_byte_HS和phy_clk_byte_HS,而且文檔明確說明clk_byte_HS是phy_clk_byte_HS的2倍。如果在DPHY中把數據總線位寬修改成16位,還必須是2倍關系嗎?

.clk_byte_HS (dphy_byte_clk ), .clk_pixel(i_sysclk), .phy_clk_byte_HS(mipi_dphy_tx_pclk),

注意:

(1)如果使用易靈思原廠提供的demo板評估,要連接R171,這個是LCD屏的復位信號 。

(2)屏的參數與IP的參數目前共用。

審核編輯:湯梓紅

-

pll

+關注

關注

6文章

781瀏覽量

135275 -

移植

+關注

關注

1文章

382瀏覽量

28158 -

時鐘

+關注

關注

11文章

1746瀏覽量

131669 -

MIPI

+關注

關注

11文章

312瀏覽量

48721 -

GPIO

+關注

關注

16文章

1216瀏覽量

52268

原文標題:MIPI2.5G DPHY TX demo移植 -v1

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于Xilinx FPGA實現MIPI DPHY接口案例分析

1.5G MIPI dsi TX移植注意事項及demo - update8

MIPI2.5G DPHY CSI2DSI demo移植 -v1

【Combat FPGA開發板】配套視頻教程——MIPI的IP CORE的使用

Gowin MIPI DPHY RX TX用戶使用指南

請問RK3568 MIPI RX DPHY接收MIPI協議的是否同時支持CSI與DSI兩種協議?

SN75DPHY440SS MIPI? CSI-2/DSI DPHY 重定時器

為何要選擇比DPHY復雜多的物理層CPHY呢?

MIPI dsi TX移植注意事項

MIPI2.5G DPHY TX demo移植教程

MIPI2.5G DPHY TX demo移植教程

評論