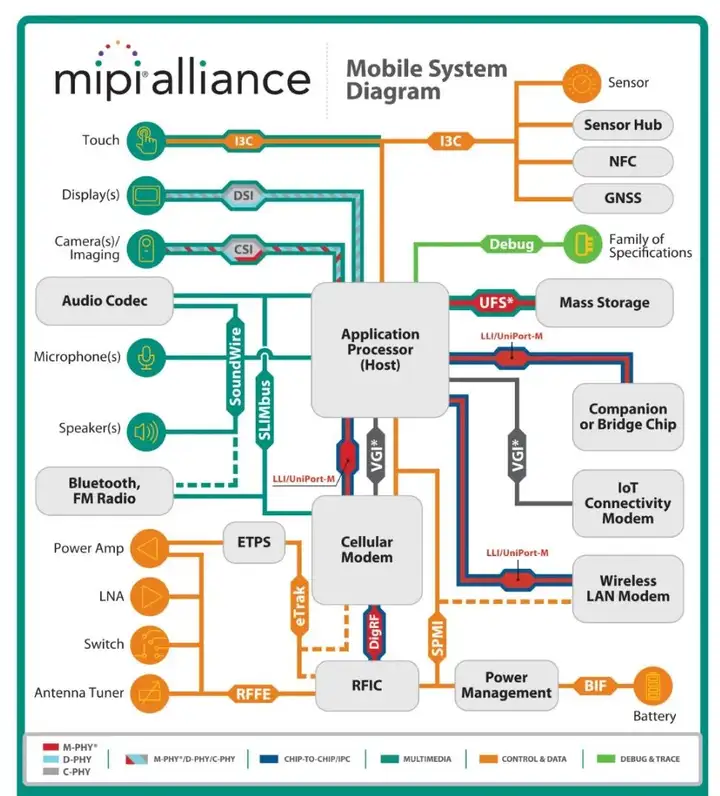

MIPI是移動領域最主流的視頻傳輸接口規范,沒有之一,目前應用最廣泛的是MIPIDPHY和MIPI CPHY兩組協議簇(另外還有MIPI MPHY,屬于高速Serdes范疇,應用不那么廣泛),其中CSI-2主要用于圖像接入(一般是接Sensor),DSI-2主要用于圖像輸出(一般是輸出到顯示屏)。

本文主要以CSI-2為例進行仔細說明,DSI-2雷同,舉一反三即可。

1 接口協議比較

關于MIPI DPHY和MIPI CPHY的詳細物理層協議和CSI-2/DSI-2協議咱們自己下載官方英文版細細品讀即可,這里主要講關鍵點。

1.1 物理層

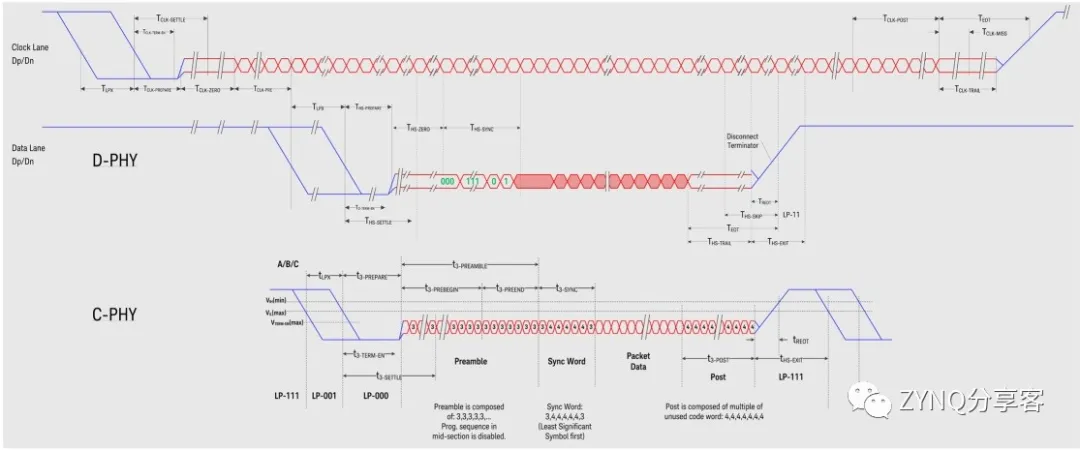

開局一張圖(見下圖1),內容是干貨,MIPI CPHY和DPHY物理層之間的差異全在這張圖里面了。

圖1 MIPI DPHY和CPHY物理層直觀比較圖

從圖1可以看出,最直觀的差異是DPHY是源同步系統,有專門的同步時鐘通道,但是CPHY沒有同步時鐘,時鐘是嵌入到數據中的。顯然的,實現嵌入時鐘的目的是為了增加帶寬,肯定會涉及到編碼,物理層的結構必然是完全不同,單從線路上看,CPHY是一個A/B/C三線系統。

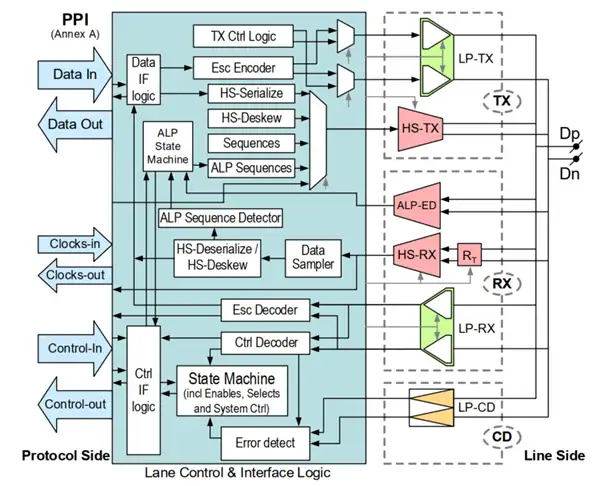

MIPI DPHY的物理層,咱們大家都很清楚,一對時鐘,幾對數據,接收端根據時鐘邊沿采樣數據,找到0xB8的同步頭,物理層實現就算是齊活了,但MIPI CPHY不同,因為它不傳輸時鐘,那么要接收CPHY的數據,必須先恢復時鐘,然后再用恢復的時鐘采樣數據并尋找同步頭,最后還需要進行數據解碼恢復出最初的發送的內容(發送端的過程相反)。

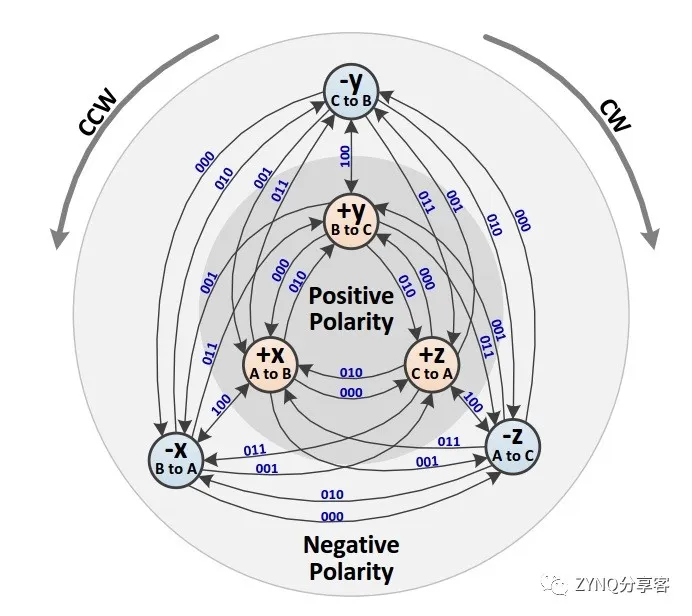

那么,CPHY物理層到底是怎么實現嵌入時鐘這一關鍵步驟的呢?請看下圖2和圖3。

圖2 CPHY“線態”變化圖

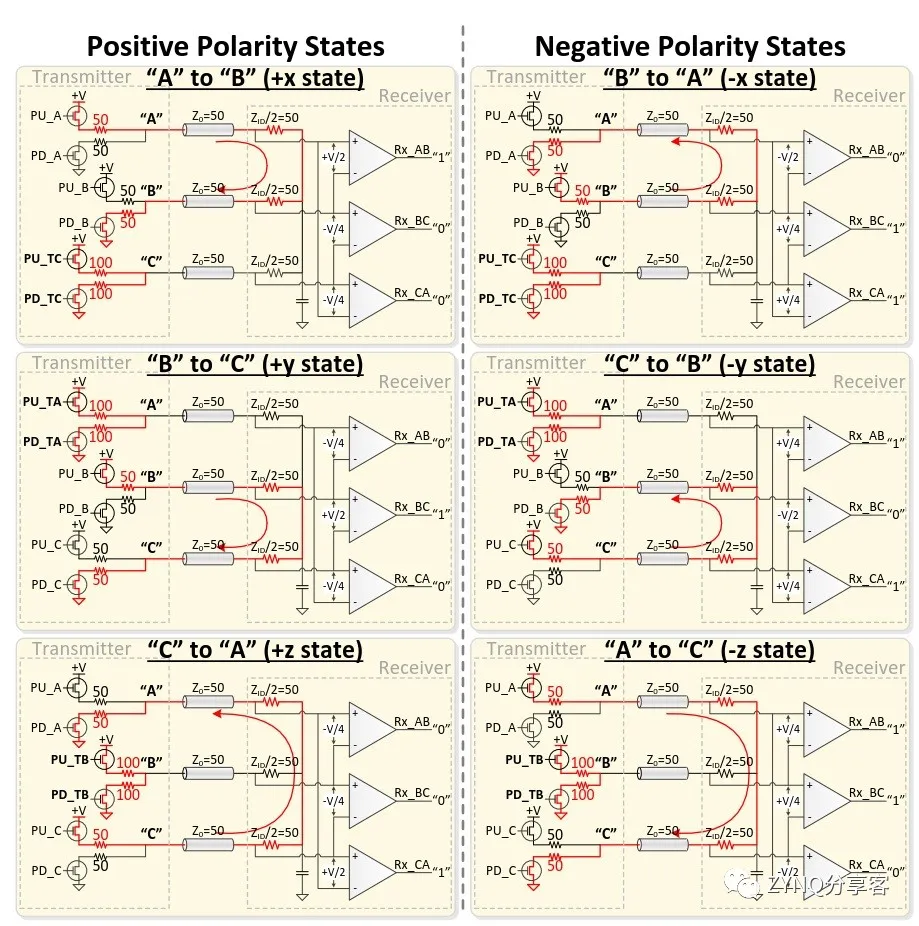

圖3 CPHY接口等效電路圖

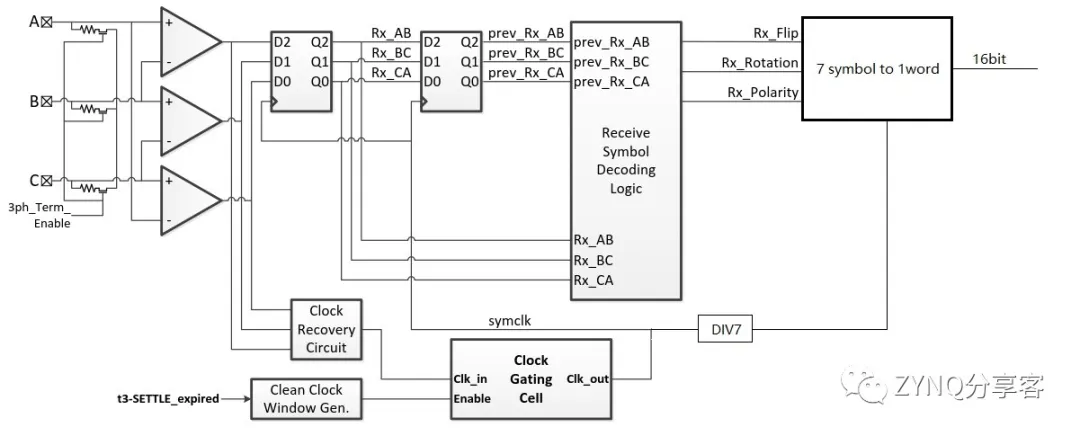

結合圖2和圖3,CPHY物理鏈路(A/B/C線)上傳輸的是不同的電平,通過A-B,B-C,C-A的電平運算,恢復出+x,-x,+y,-y,+z,-z六種不同的線態,通過前后線態的旋轉方向,相位和極性恢復出編碼符號,再通過連續7組符號解碼出16bit的數據,整個過程見下圖4。

圖4 數據恢復過程圖

為何要選擇這比DPHY復雜多的物理層呢?一切都是為了提升帶寬,從圖2可以看出,某種線態的可能有5種不同的變化,那么它每個符號可編碼的數據為log2(5) = 2.3219,理論帶寬為DPHY的2.3219倍,每16bit數據編碼成7個符號,帶寬優勢明顯。

1.2 CSI-2層

MIPI CPHY和MIPI DPHY的CSI-2層協議大致相同,細節上的差異如下:

(1) DPHY以Byte為單位進行數據組織;CPHY以16bit Word為單位進行數據組織;

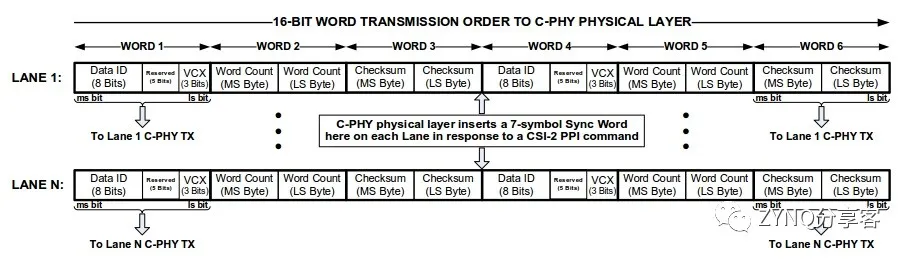

(2) DPHY 的短幀和長幀的幀頭信息與數據的組織方式相同;CPHY則是固定每個通道為6×16bit的幀頭信息(短幀信息),見下圖5。

圖5 CPHY CSI-2數據組織

因此,在CSI-2解包邏輯尚無法完全共用。

2 FPGA實現

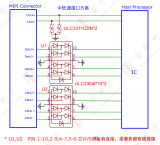

MIPI接口電平比較特殊,LP模式下為1.2V的LVCMOS電平,DPHY在HS模式下為SLVS-400電平,CPHY在HS模式下需要做電平減法運算。

2.1 硬件電路

就目前而言,直接支持MIPI DPHY的FPGA主要有Xilinx UltraScale+系列(1.5Gbps/Lane Max)Lattice Crosslink(1.5Gbps/Lane Max)及Lattice Crosslink NX(2.5Gbps/lane Max),其它型號的PFGA均需添加額外的電平轉換電路將信號轉換為LVDS。

(1) DPHY,低于800Mbps/lane速率,使用電阻網絡即可;高速率的需選用專門的電平轉換芯片,如MC20901、LT89101L等;

(2) CPHY,因為需要做減法運算,故可用專門的告訴比較器(或Repeater),結果以LVDS電平輸出。

2.2 邏輯實現

邏輯實現的差異主要在物理層,CPHY和DPHY完全不同。

2.2.1 MIPI DPHY

MIPI DPHY屬于源同步系統,轉換為LVDS電平后就是一個通用的ISERDES邏輯,主要是時鐘方案有兩種考慮:

第一種:使用PLL、MMCM或DLL,此種方案對PLL的鎖定時間有較高的要求,通常要求us級才能保證在時鐘不連續模式下正常鎖定,當然具有專用DPHY邏輯的器件有專門的PLL電路實現。這種方案的好處是不易受時鐘毛刺的影響,接收較為穩定。

第二種:在源同步時鐘基礎上使用專門的時鐘buffer分頻(如Xilinx 7系列的BUFR),這種方案可適應任意速率,不需要預先設定速率來配置鎖相環電路,缺點是易受時鐘毛刺影響,出錯率稍高。

2.2.2 MIPI CPHY

MIPI CPHY的難點是時鐘恢復,在FPGA系統中,沒有針對MIPI CPHY的專用時鐘恢復電路(CDR),因此,需要充分利用CPHY的線態編碼均衡和FPGA可編程延時電路的特點來實現CDR,這種方案理論上要求FPGA內部延時邏輯約精確越好,LUT時鐘性能越高,這樣會把時鐘恢復誤碼和抖動降到最低。時鐘恢復完成后,線態解碼、符號解碼和數據恢復流程見圖4。

總之,MIPI CPHY在MIPI DPHY的基礎上成倍增加了帶寬,減少了線對數量,在高速大靶面傳感器和高分高刷新移動設備OLED應用上越來越普及。

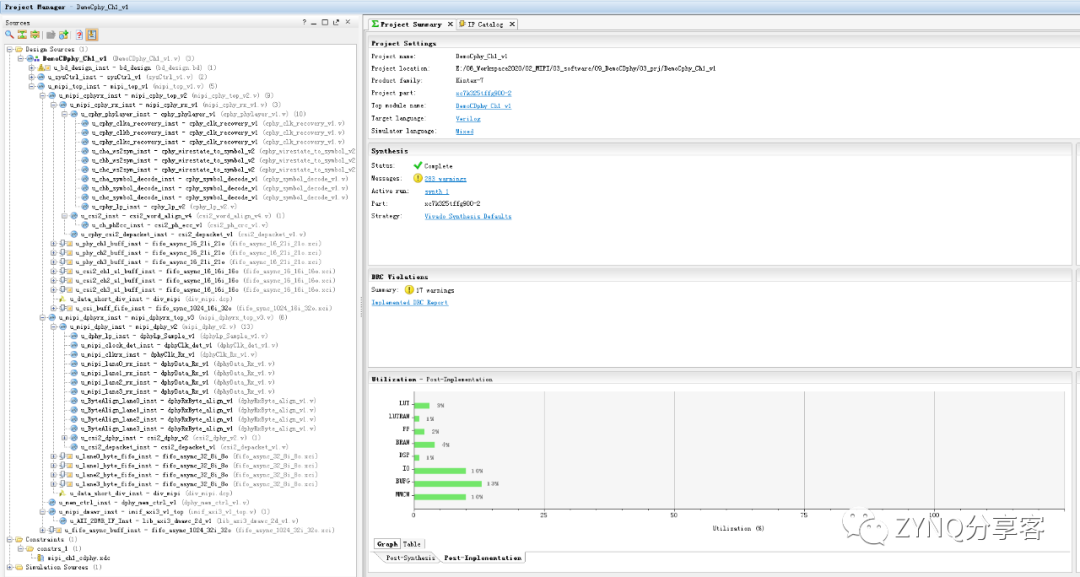

2.2.3 資源占用

Panda君在Xilinx kintex-7系列FPGA對MIPI DPHY+CPHY 接收IP進行了驗證,占用資源SliceLUTs為2352個,Slice Registers 3401個。本方案亦可在紫光同創、高云等國產FPGA上降速實現。

圖5 MIPI DPHY+CPHY Vivado工程圖

編輯:hfy

-

FPGA

+關注

關注

1630文章

21791瀏覽量

605094 -

MIPI

+關注

關注

11文章

312瀏覽量

48721

發布評論請先 登錄

相關推薦

MIPI2.5G DPHY CSI2DSI demo移植 -v1

DS90UB954A偶發MIPI信號異常,從mipi信號上看是mipi振幅突然變大,為什么?

基于RK3588J的6路MIPI CSI視頻采集案例分享,多路視頻系統必看!

聚焦MIPI 系列之四:一文盤點D-PHY/C-PHY/M-PHY之架構與測試解決方案

【技術分享專欄】MIPI接口與LVDS接口有何區別?

如何通過RK3576配置MIPI-CSI攝像頭的不同輸出格式

mipi顯示器接口多少引腳

mipi接口和edp接口可以轉換嗎?

LM8335帶MIPI?RFFE主機接口的通用輸出擴展器數據表

具有 MIPI?RFFE 接口的 降壓-升壓轉換器LM3279數據表

關于MIPI DPHY和MIPI CPHY接口比較及FPGA實現方案

關于MIPI DPHY和MIPI CPHY接口比較及FPGA實現方案

評論