門控時鐘

當寄存器組的輸出端沒有驅動或沒有變化時,可以關掉寄存器組的時鐘來減少動態功耗,此謂門控時鐘 (Clock Gating, CG) 技術。

最簡單的一個帶 EN 端的 D 觸發器的 Verilog 邏輯描述如下:

always @(posedge CLK)

if (EN)

Q <= D ;

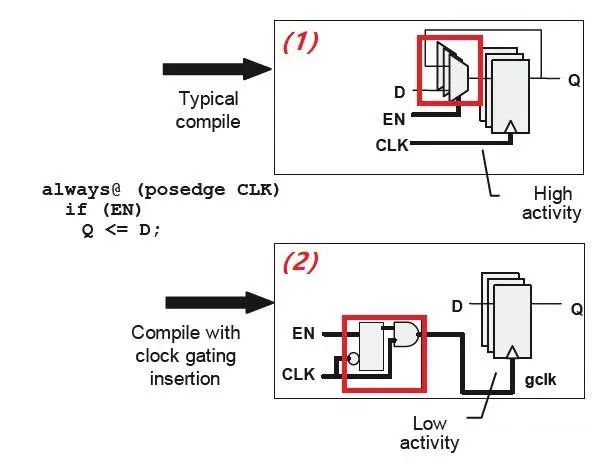

當不采用門控時鐘結構時,DC 綜合時會在觸發器的輸入端增加為帶反饋端的多路選擇器電路,如下圖 (1) 所示。

當采用門控時鐘結構時,DC 綜合時僅會在觸發器的時鐘端增加一個時鐘門控單元 (CG cell),而沒有多路選擇器結構,如下圖 (2) 所示。

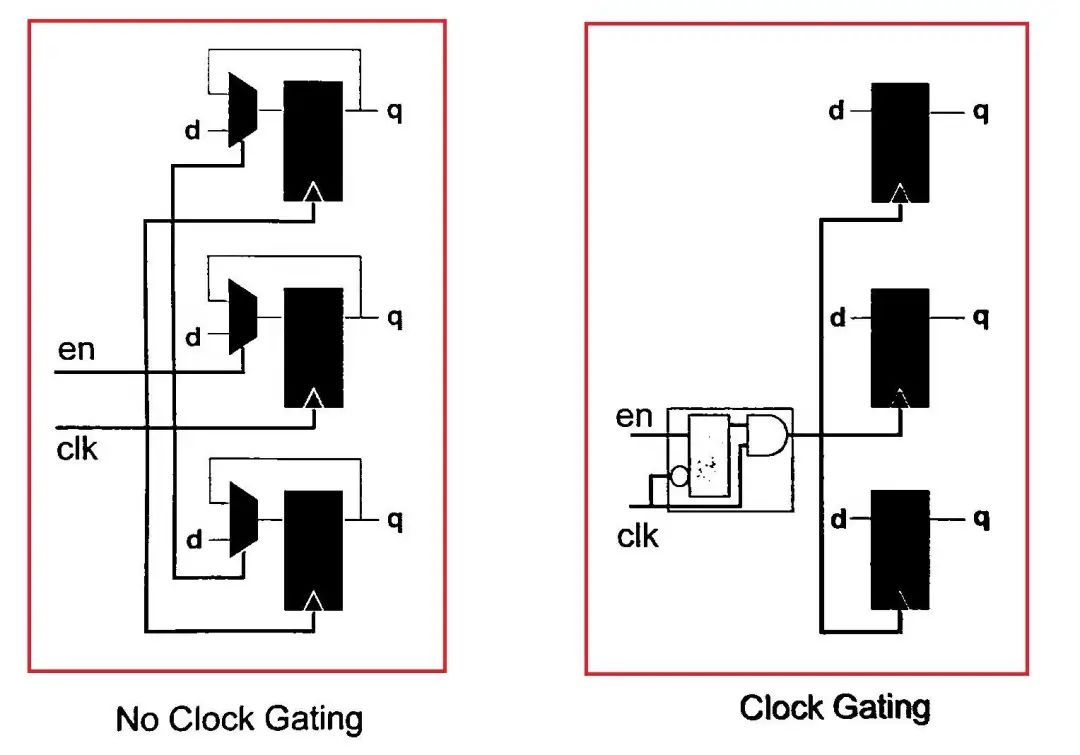

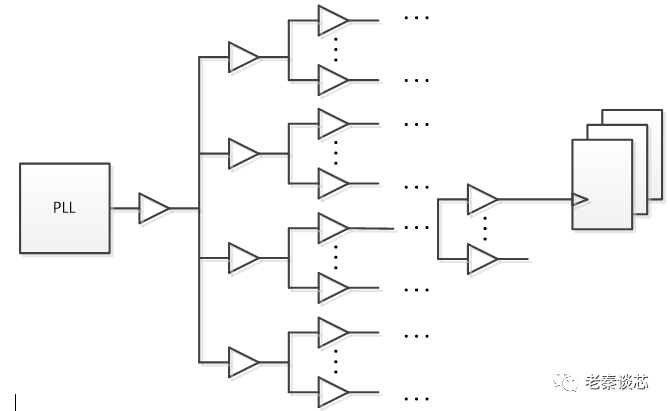

當多個寄存器組共用一個控制端時,結構上的優化尤為明顯,如下圖所示:

綜上所述,門控時鐘的優點有:

(1) 寄存器時鐘端翻轉率降低,動態功耗降低。

(2) 時鐘樹網絡開關率降低,動態功耗降低。

(3) CG 扇出越大,結構上節省的選擇器越多,硬件資源消耗越少。

(4) 相比于 PG (Power Gating),CG 結構相對簡單,在綜合時可自動插入。

產生門控時鐘

產生門控時鐘的條件為:

寄存器組共用同一個時鐘;

寄存器組的控制端都是同步的;

寄存器組都是由同一個變量中推斷而來的。

自動插入 CG

DC 綜合時,使用以下命令與參數,設計中符合要求的寄存器便會被綜合成帶 CG 結構的觸發器。

compile_ultra -gate_clk

DC 綜合時插入的 CG 又分為離散的 CG cell 與集成的 CG cell (ICG)。離散的 CG cell 使用 Latch 與基本邏輯門單元組合而成,集成的 CG cell 是工藝廠家提供的一個帶有時鐘門控功能的特殊單元。

DC 中插入離散的 CG 命令為:

# 使用帶 latch 結構的離散的 CG

set_clock_gating_style -sequential_cell latch

# 離散的 CG 中指定具體的 latch cell "lib_cell"

set_clock_gating_style -sequential_cell latch:lib_cell

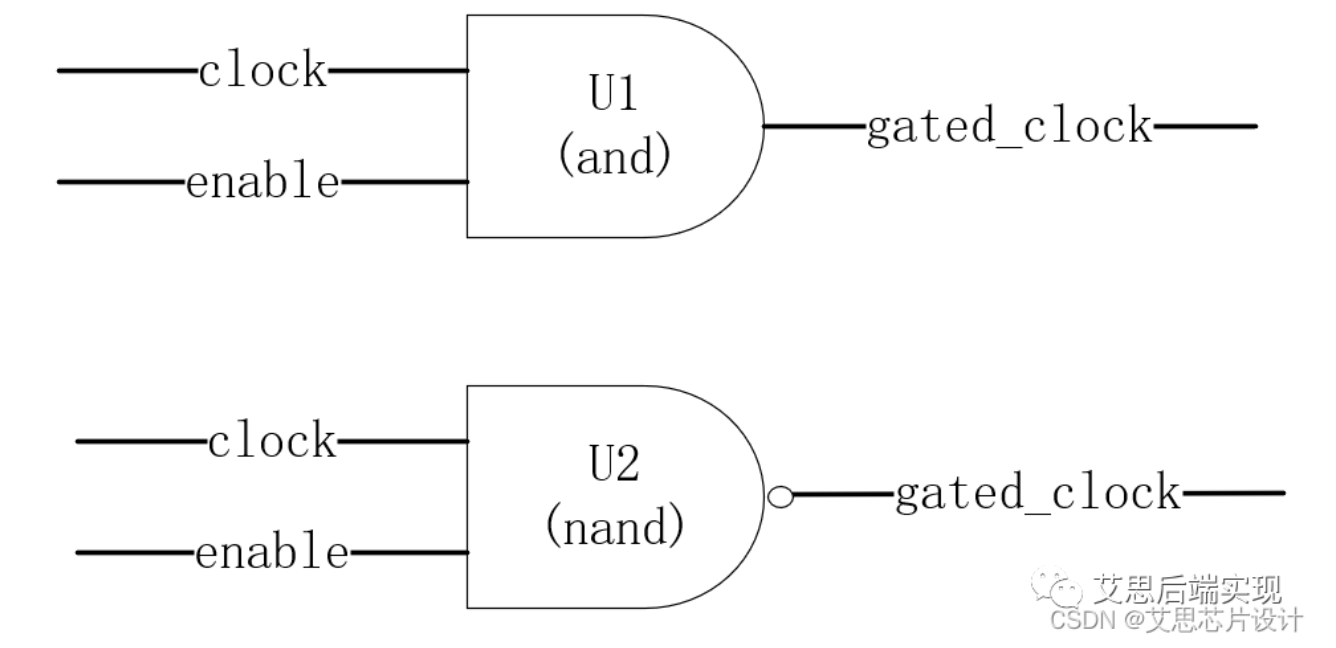

DC 中插入沒有 Latch 結構的離散 CG 時,命令如下:

# 使用或門邏輯,生成上升沿工作的寄存器的時鐘門控

set_clock_gating_style -sequential_cell none -pos {or}

因為使用與門生成 CG 時在時鐘上升沿容易出現毛刺,使用或門生成 CG 時在時鐘下降沿容易出現毛刺,所以參數 -pos 一般配合 {or} 使用,-neg 一般配合 {and} 使用。

# 使用與門邏輯,生成下升沿工作的寄存器的時鐘門控

set_clock_gating_style -sequential_cell none -neg {and}

假如 -sequential_cell 與 -pos/-neg 選項同時使用,那么兩個選項指定的 CG 電路結構應該保持一致,例如:

set_clock_gating_style -sequential_cell latch -neg {latch and}

set_clock_gating_style -sequential_cell none -neg {and}

DC 中插入 ICG 時,命令如下:

# 使用集成的 CG cell

set_clock_gating_style -negative_edge_logic {integrated}

# 指定使用具體的集成 CG cell "lib_cell"

set_clock_gating_style -negative_edge_logic {integrated:lib_cell}

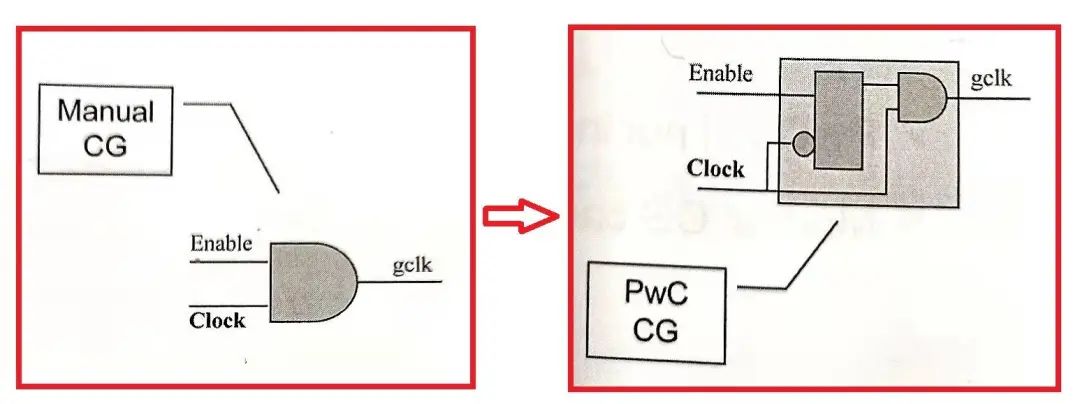

手動插入 CG

如果設置了自動產生時鐘門控(-gate_clk),DC 綜合時會對 RTL 設計中符合要求的寄存器進行時鐘門控。但如果在 RTL 設計中,人為的編寫時鐘門控邏輯,DC 對此不會插入 CG ,如以下 Verilog 描述。

assign gated_clk = clk & en ;

always @(posedge gated_clk or negedge rstn) begin

if (!rstn)

data_out <= 8'b0 ;

else

data_out <= data_out + 1'b1;

end

人為編寫的時鐘門控邏輯中,時鐘很容易出現毛刺,增加了設計的不穩定性。

為了消除人為編寫時鐘門控邏輯帶來的隱患,DC 中需要使用以下命令對手動編寫的 CG 進行識別與替換。

replace_clock_gates

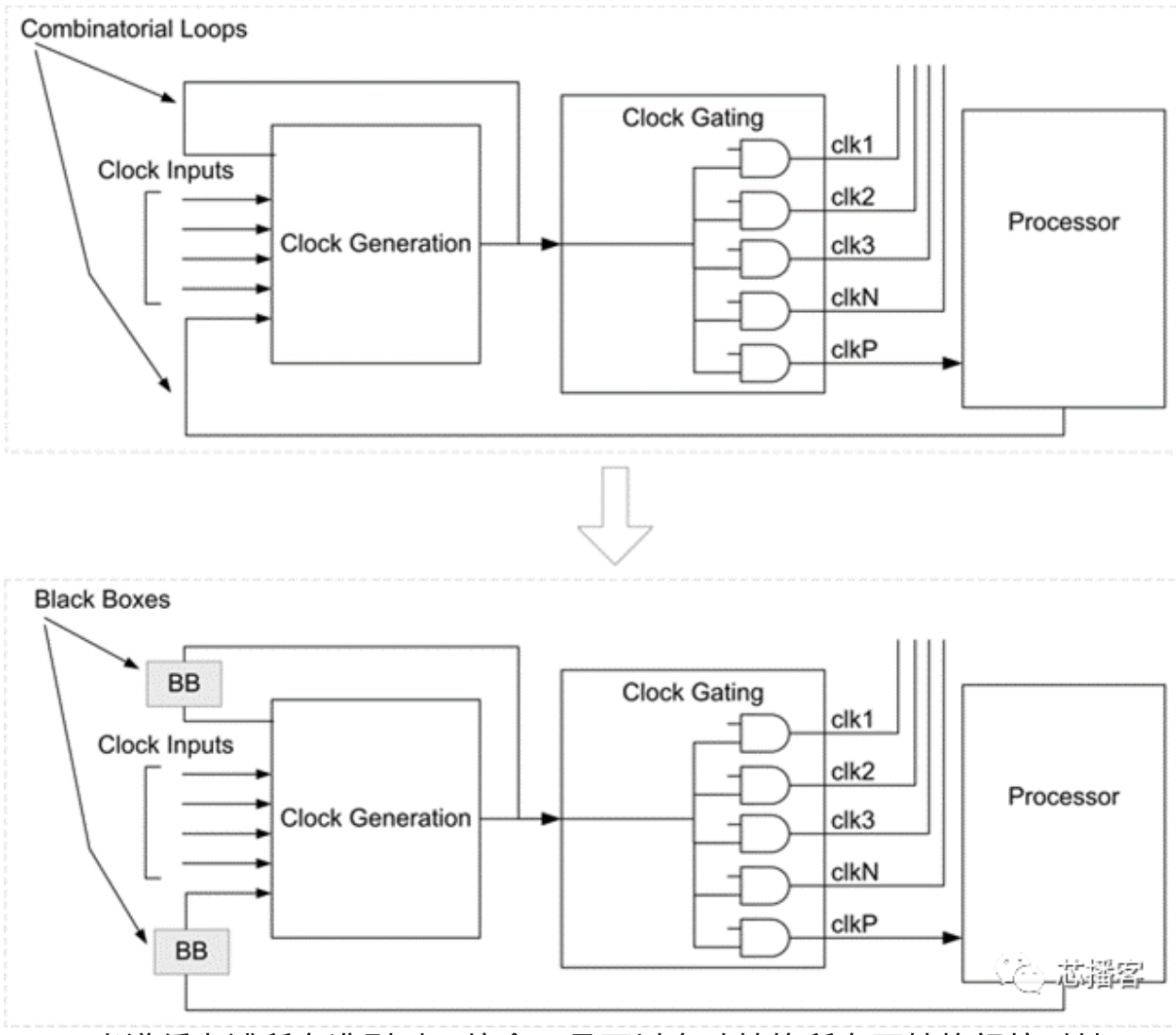

此命令實現的優化結果示意圖如下:

禁止使用 CG

由于面積、時序等原因,需要禁止使用 lib 中的某一種 CG cell 時,可以使用以下命令:

#禁止使用指定的 CG cell:"lib_cell",

set_dont_use -power {lib_cell}

其中,-power 選項不可或缺,否則 ICG cell 的 dont_use 屬性會被忽略。

門控時鐘報告

可以使用以下命令,查看時鐘門控單元的插入情況,以便確認是否需要對電路進行修改。

report_clock_gating

但是如果 RTL 設計中,存在人為例化的 CG cell,命令 report_clock_gating 是不能識別的,需要設置以下命令:

set power_cg_auto_identify true

-

寄存器

+關注

關注

31文章

5363瀏覽量

120939 -

Verilog

+關注

關注

28文章

1351瀏覽量

110260 -

功耗

+關注

關注

1文章

828瀏覽量

32016 -

觸發器

+關注

關注

14文章

2003瀏覽量

61286 -

門控時鐘

+關注

關注

0文章

27瀏覽量

8963

發布評論請先 登錄

相關推薦

什么是時鐘門控?如何去實線時鐘門控的設計呢

門控時鐘與時鐘偏移研究

一文詳解門控時鐘

一文詳解門控時鐘

評論