時(shí)鐘門控(Clock Gating)是一種在數(shù)字IC設(shè)計(jì)中某些部分不需要時(shí)關(guān)閉時(shí)鐘的技術(shù)。這里的“部分”可以是單個(gè)寄存器、模塊、子系統(tǒng)甚至整個(gè)SoC。

為什么需要時(shí)鐘門控:大多數(shù)SoC都是power constrained,mobile端不能夠充更多的電就只能盡可能地降低功耗了(無法開源只能節(jié)流呀),也因?yàn)闀r(shí)鐘門控是降低芯片動(dòng)態(tài)功耗最簡(jiǎn)單,最常用的方法之一。

時(shí)鐘門控技術(shù)分類:通常,有兩種不同的時(shí)鐘門控實(shí)現(xiàn)技術(shù)。

combinational clock gating–這種類型的時(shí)鐘門控由工具在綜合時(shí)自動(dòng)識(shí)別引入。

sequential clock gating–這種類型的時(shí)鐘門控作為功能的一部分引入RTL設(shè)計(jì)中。通常時(shí)鐘門控策略在系統(tǒng)架構(gòu)中定義,然后由設(shè)計(jì)人員進(jìn)行實(shí)現(xiàn)。

combinational clock gating

最簡(jiǎn)單的combinational clock gating可以通過AND門實(shí)現(xiàn),如下圖所示

當(dāng)enable為1時(shí),時(shí)鐘會(huì)傳給寄存器FF;當(dāng)enable為0時(shí),時(shí)鐘將被關(guān)閉, FF將不起作用。這種最簡(jiǎn)單的時(shí)鐘門控技術(shù)形式存在一些問題,即在提供給FF的時(shí)鐘中產(chǎn)生毛刺。

可以通過在時(shí)鐘使能信號(hào)的輸出端引入一個(gè)低電平敏感的鎖存器來解決這個(gè)問題。

鎖存器輸出僅在時(shí)鐘低電平內(nèi)更新,因此與門的輸入將穩(wěn)定為高。

Integrated Gated Clock Cells(ICG Cell)

要實(shí)現(xiàn)這種時(shí)鐘門控可以實(shí)例化標(biāo)準(zhǔn)單元庫中的兩個(gè)Cell(Latch和AND門),秉著不重復(fù)造輪子的思想以及方便工具進(jìn)行后續(xù)的時(shí)序分析更建議使用庫中的ICG Cell并且由工具自動(dòng)綜合插入。

時(shí)鐘使能信號(hào)可以由軟件控制和硬件同時(shí)控制,即由軟件控制是否需要啟動(dòng)時(shí)鐘門控,硬件動(dòng)態(tài)控制時(shí)鐘使能。

軟件控制示例如下:

軟件控制這個(gè)全局時(shí)鐘使能信號(hào),為低電平時(shí)不打開時(shí)鐘門控,這種全局時(shí)鐘門控使能策略可以進(jìn)行層次化的設(shè)計(jì),從系統(tǒng)級(jí)到最終的單個(gè)寄存器。

硬件控制示例如下:

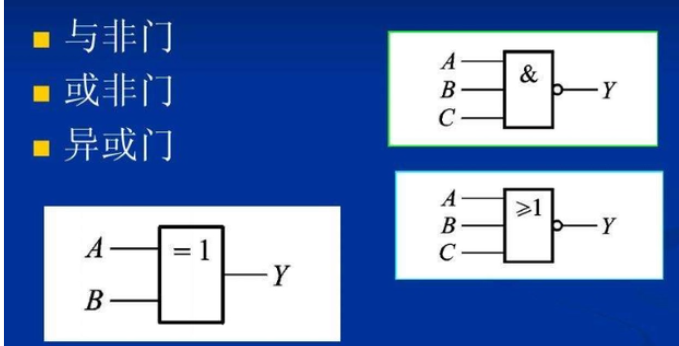

XOR門的輸入連接到FF的輸入和輸出。如果FF的輸入和輸出相同,則無需觸發(fā)FF,此時(shí)可對(duì)時(shí)鐘進(jìn)行門控。

在前端RTL級(jí)引入combinational clock gating很簡(jiǎn)單,沒有對(duì)邏輯功能產(chǎn)生影響,可以由EDA工具自動(dòng)插入。但是在物理設(shè)計(jì)的視角,這可能是一個(gè)更大的課題,因?yàn)槲覀円肓艘粋€(gè)實(shí)實(shí)在在的物理cell,更何況還是在時(shí)鐘路徑上。

從時(shí)序功耗上, clock gating應(yīng)該離寄存器時(shí)鐘端遠(yuǎn)還是近?

從面積功耗上,只有一個(gè)寄存器是否應(yīng)該被門控?

sequential clock gating

除了上述combinational clock gating外,還有sequential clock gating,這涉及對(duì)RTL設(shè)計(jì)中多個(gè)時(shí)鐘周期進(jìn)行深入分析。當(dāng)然基本思想也很簡(jiǎn)單,如果寄存器X在周期C中未更新,并且在時(shí)鐘周期C + 1中輸入給寄存器Y的D端,則無需在周期C + 1中使能寄存器Y的時(shí)鐘。

原文標(biāo)題:時(shí)鐘門控終極指南

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

寄存器

+關(guān)注

關(guān)注

31文章

5343瀏覽量

120426 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1734瀏覽量

131510

原文標(biāo)題:時(shí)鐘門控終極指南

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AMC1204有兩種封裝,SOIC-8和SOIC-16,功能一樣嗎?為什么要推出兩種封裝?

ADS1292R有 \"1 ch ECG + 1 ch呼吸偵測(cè)\" 或 \"2 ch ECG\" 兩種模式,是否可以在產(chǎn)品上實(shí)現(xiàn)自行切換兩種使用模式?

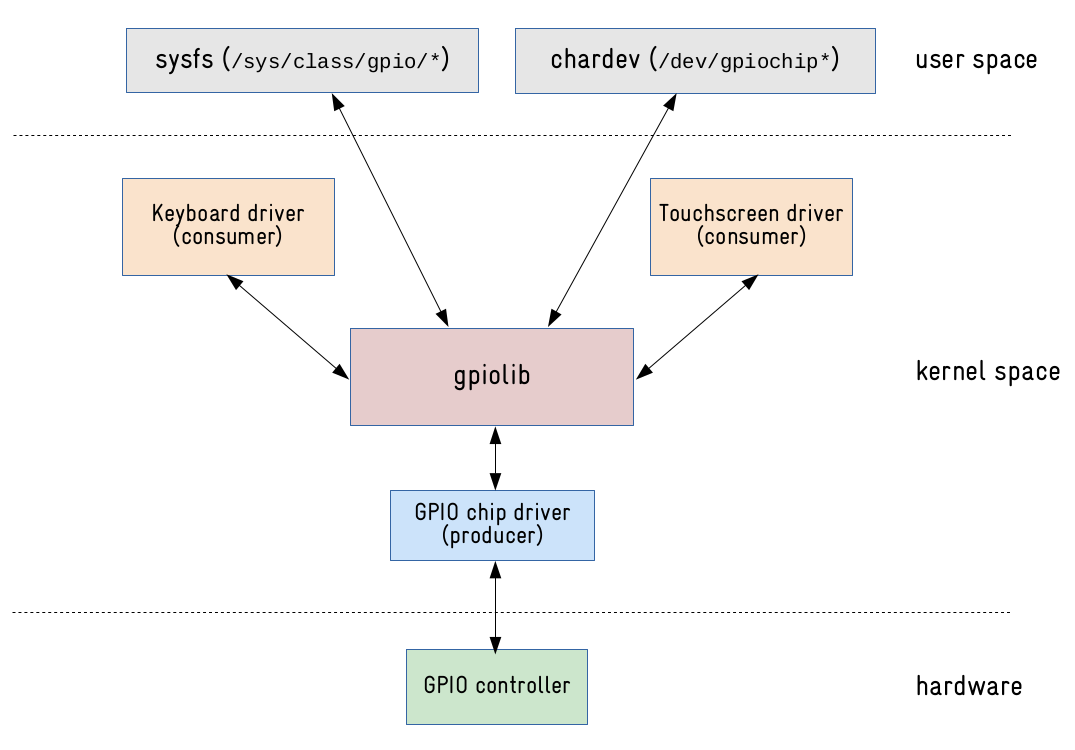

Linux應(yīng)用層控制外設(shè)的兩種不同的方式

門控rs鎖存器和觸發(fā)器的區(qū)別是什么

晶閘管的阻斷狀態(tài)有兩種是什么

示波器兩種衰減方式的區(qū)別是什么

wdm設(shè)備的兩種傳輸方式

控制器有哪兩種實(shí)現(xiàn)方式?各有何優(yōu)缺點(diǎn)?

過電壓破壞絕緣通常有哪兩種情況

異或門兩種常見的實(shí)現(xiàn)方式

怎么根據(jù)外圍電路配置單片機(jī)gpio的時(shí)鐘

OpenCV兩種不同方法實(shí)現(xiàn)粘連大米分割計(jì)數(shù)

什么是浪涌電流,關(guān)于浪涌抑制的兩種方案

XOR自門控與時(shí)鐘門控的不同之處

通常有兩種不同的時(shí)鐘門控實(shí)現(xiàn)技術(shù)

通常有兩種不同的時(shí)鐘門控實(shí)現(xiàn)技術(shù)

評(píng)論