開始之前,我們首先來看一下什么是時鐘門控(clock gating)技術,顧名思義就是利用邏輯門技術控制時鐘的通斷。

那么為什么需要控制時鐘的通斷呢?主要基于以下幾個原因。首先,隨著工藝的發展和設計規模的增大,時鐘樹上產生的功耗占整個SoC功耗的比例越來越高,有時幾乎能占到50%左右。關于時鐘樹,可能前端的同學不熟悉,簡單說幾句,SoC的時鐘一般是參考時鐘經過PLL和數字分頻器輸出的,后面可能要連接驅動成千上萬的寄存器clock端。

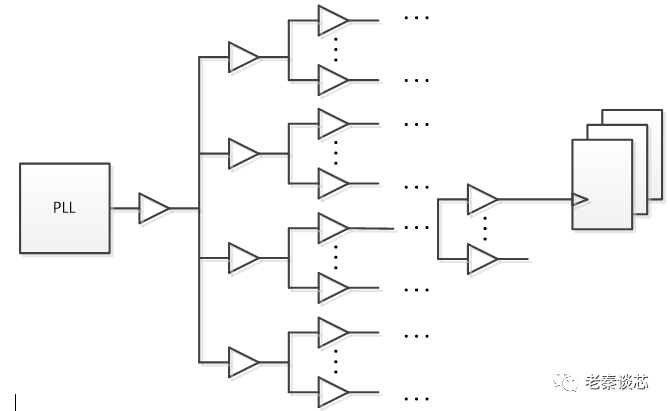

這時候任何一個單一的cell都不可能有這么大的驅動能力,因此要插入大量的buffer,而且為了保證到每個寄存器的延時一樣,clock tree還要做balance。整個的時鐘樹大概長成下圖這樣,第一級buffer叫root,中間的buffer叫branch,最后一級的buffer叫leaf:

圖1 時鐘樹示意圖

如果我們的芯片在不工作時,PLL依然有clock輸出的話,那整個時鐘樹依然產生很大的功耗。

接下來我們再看一下邊沿觸發器的結構圖。從圖上我們能看出即使D端保持不動,clock端變化也會消耗一些能量。想深入研究的同學可自行推導(可以忽略兩個復位信號)。

圖2 邊沿D觸發器

那么當D端長時間不變時,是不是可以把CP端的變化隔離掉以降低功耗呢?答案是肯定的。

最簡單的辦法就是把clock信號和一個EN信號做“與”操作,如下圖:

圖3 簡單的時鐘門控邏輯

這個方法雖然簡單,但是如果我們不能保證EN信號相對clock的到來時間和保持時間,那么就很可能不能產生門控時鐘或者產生毛刺(glitch)。為了解決這個問題,人們提出了基于鎖存器的時鐘門控邏輯。由于鎖存器能捕捉到EN信號并使它保持到產生完整的時鐘脈沖,因此EN信號只需要在時鐘活躍沿附近保持穩定即可。使用這種技術,每次只需要改變門的一個輸入端來打開或關閉時鐘就能保證電路的輸出不含有任何毛刺或者尖峰脈沖了。

圖4 基于鎖存器的時鐘門控

現在的芯片生產商會提供時鐘門控的標準單元,為了DFT測試的需要,標準門控單元還會帶著test_en這種輸入信號,今天為了不跑題就不介紹相關內容了。

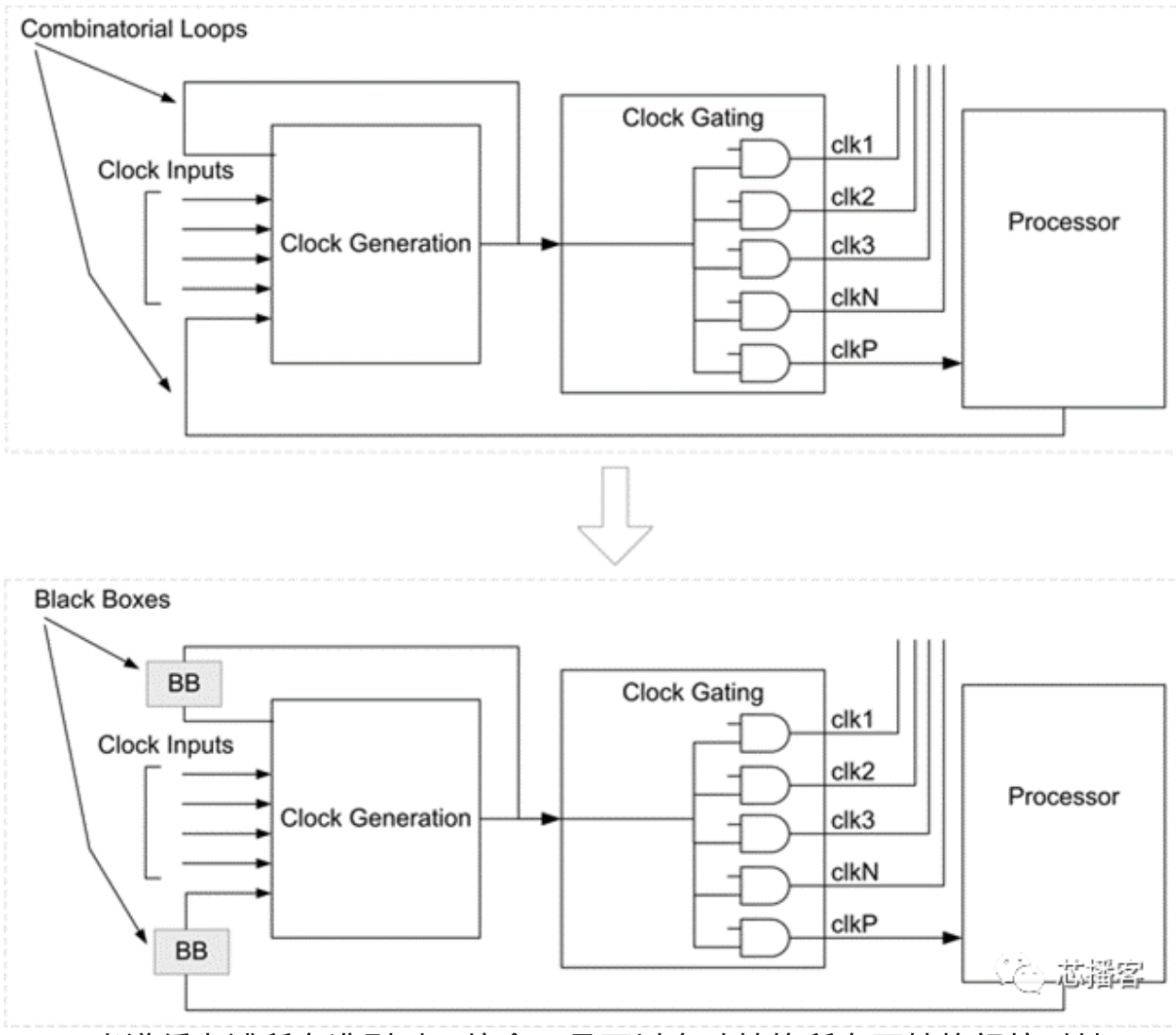

接下來就是架構師和邏輯設計工程師關心的問題了,怎么設計門控邏輯。在SoC設計中,可以實現三種粒度的時鐘門控設計,首先是粗粒度的設計,架構師要決定如何在時鐘產生單元增加門控邏輯,根據SoC工作情況來判決是否關斷某個時鐘輸出。這里提供一個思路,先根據功能劃分出clock domain,然后再根據每個模塊/IP之間的關系制定一張表,用于決定每個時鐘域的開啟和關閉狀態。

有了這張表就相當于有了一個狀態機,根據狀態機的當前狀態決定時鐘是否關閉。至于狀態跳轉的判決,可以是硬判決也可以是軟判決。硬判決的好處是相對速度快;缺點是靈活性較差,而且設計相對復雜,往往需要模塊/IP有接口信號可用。軟判決剛好相反,優點是靈活性高;缺點是延遲比較大,不適于頻繁開關,對于某些設計來說,實現軟判決還要增加處理器,畢竟不是所有SoC都有CPU/MCU/DSP的。

其次是中等粒度的設計,模塊設計師來決定是否關斷內部子模塊的時鐘輸入。這里沒啥好說的,完全取決于模塊的功能和實現方案了。

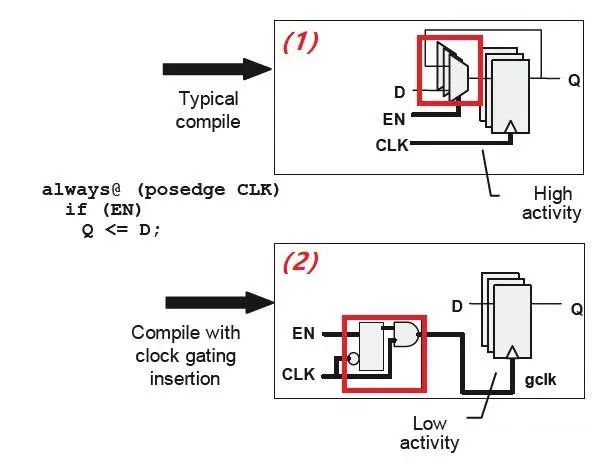

最后,可以在邏輯綜合階段,由綜合工具自動插入門控單元。前面兩條依賴具體設計,最后一條不完全依賴設計,再多說幾句。如果RTL代碼寫成下圖左邊的樣子,在邏輯綜合時不打開插CG的選項,綜合出的電路如中圖所示;而打開插入CG的選項,就會綜合出下圖右邊的電路。由于CG單元本身也會產生功耗,一般一個CG單元后面要接多個寄存器才能達到節省功耗的效果。一般在綜合時會通過選項選擇3或4個。

圖5 綜合插入CG的示意圖

對于綜合工具,其插入CG的判定很簡單,就是看有沒有上圖代碼中的enbale邏輯。如果沒有就不插。所以如果邏輯設計師想要寫出滿足低功耗需求的RTL代碼,就要盡量在代碼中使用類似上圖的enable邏輯。可能有喜歡刨根問底的同學要提問了“如果我的某段邏輯就沒有enable怎么辦?”這種情況下,可以試著向前或者向后找一找,有沒有哪些邏輯可以借用過來。比如下圖例子,綠色虛線代表可以增加的邏輯。RTL低功耗設計方法有很多,大家可以百度一下,或者等我以后寫(此處有坑)。

圖6 前向借用邏輯產生時鐘門控信號

最后,要說明一個關于clock gating的誤區。時鐘門控固然可以節省功耗,但并不是越多越好。當CG cell達到一定數量時,再增加CG cell對功耗節省的效果就不明顯了。而且如前面所說,CG cell本身也是要產生功耗的,數量太多的話肯定要消耗不少,而且還會占用大量的面積,過猶不及。(再一次體現出做SoC的balance藝術,還是那句話,沒有完美的SoC,只有完美的tradeoff)

圖7 CG數量與節省功耗的關系

結束前總結一下,clock gating技術對整體SoC設計的影響。

表1 低功耗技術總結

-

寄存器

+關注

關注

31文章

5343瀏覽量

120426 -

分頻器

+關注

關注

43文章

447瀏覽量

49943 -

SoC設計

+關注

關注

1文章

148瀏覽量

18774 -

時鐘門控

+關注

關注

0文章

7瀏覽量

6836 -

PLL電路

+關注

關注

0文章

92瀏覽量

6413

發布評論請先 登錄

相關推薦

什么是時鐘門控?如何去實線時鐘門控的設計呢

門控時鐘與時鐘偏移研究

什么是時鐘門控技術?為什么需要控制時鐘的通斷呢?

什么是時鐘門控技術?為什么需要控制時鐘的通斷呢?

評論