本文主要介紹DRAM的存儲原理、存儲電容、存儲結(jié)構(gòu)等內(nèi)容,后續(xù)會針對SDRAM和DDR等具體類型進(jìn)行詳細(xì)介紹。

1、概述

DRAM包括:SDRAM、DDRx、SDR、LPDDRx、LPSDR、GDDR、RLDRAMx(Reduced Latency DRAM)、EDO DRAM、FPM DRAM、Mobile DRAM等等。

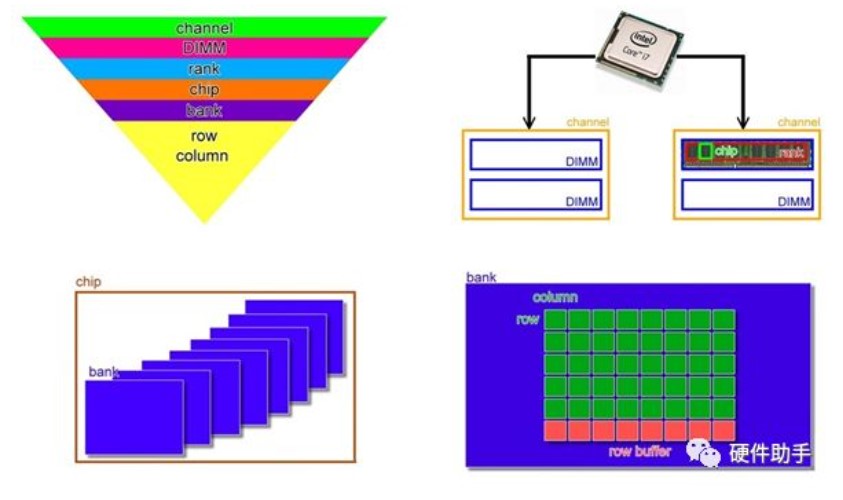

主存DRAM由大至小,由上往下可做以下拆分:channel→DIMM→rank→chip→bank→row/column。

2、DRAM存儲原理

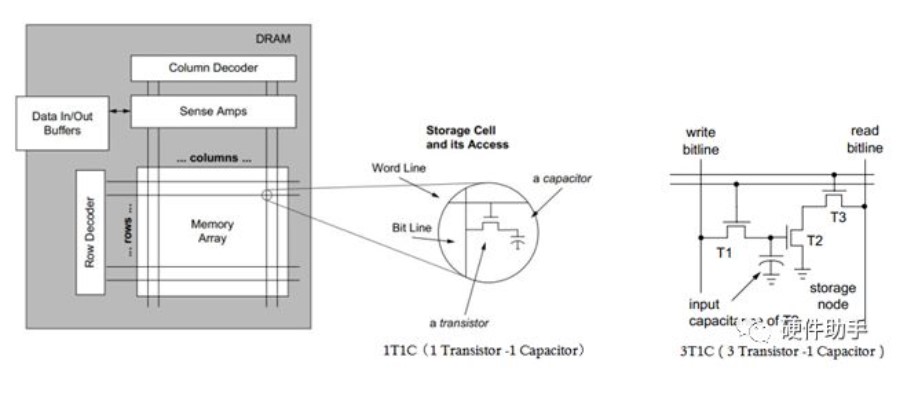

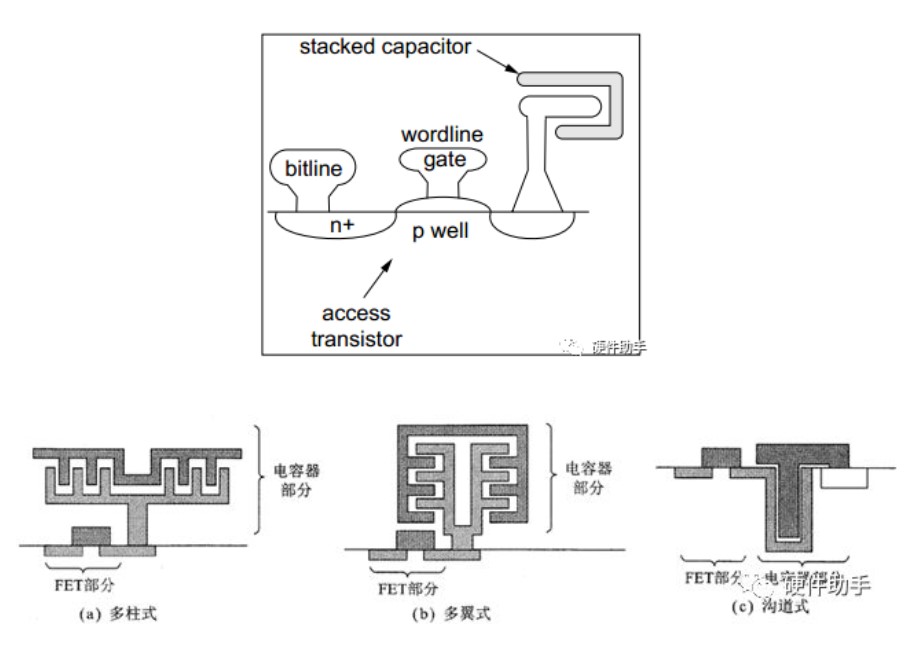

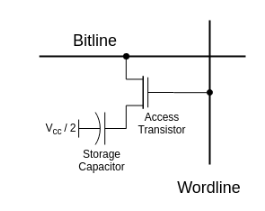

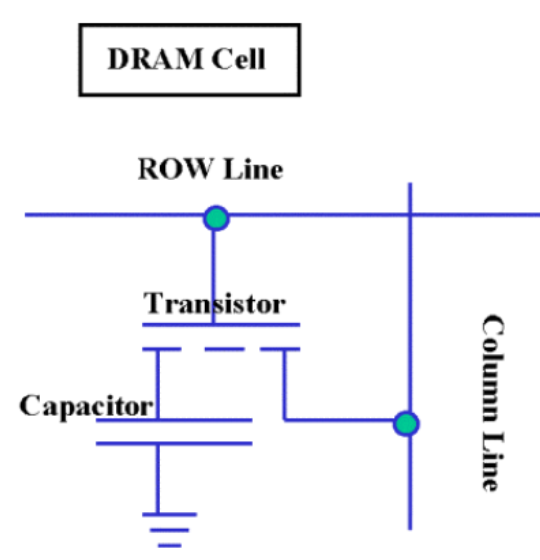

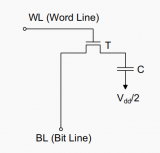

DRAM的結(jié)構(gòu)大致分為兩種:1T1C和3T1C,詳見下圖。

1T1C(1 Transistor -1 Capacitor)的大致原理是:當(dāng)Word Line選通時(shí),晶體管導(dǎo)通,從而可以從Bit Line上讀取存儲在電容上的位信息。

3T1C(3 Transistor -1 Capacitor)使用三個(gè)晶體管作為開關(guān),這樣設(shè)計(jì)的優(yōu)點(diǎn)是:當(dāng)讀取存儲在電容上的位信息時(shí),不會影響電容上的電荷,從而讀后不需要對單元進(jìn)行precharge。但是由于1T1C的結(jié)構(gòu)比3T1C的結(jié)構(gòu)面積節(jié)省很多,因此現(xiàn)代DRAM中常用的還是1T1C結(jié)構(gòu)。

DRAM的信息是存儲在電容當(dāng)中的,而電容中的電荷會因?yàn)槁╇娏鞯拇嬖诙饾u漏掉,因此需要不斷refresh(刷新),這也是DRAM稱為動態(tài)的原因。例如,90nm工藝下,DRAM的cell單元的電容量是30pF,它的漏電流是1fA,漏光的時(shí)間是隨著溫度的變化而變化的。現(xiàn)在的DRAM的刷新時(shí)間一般是32ms或者64ms。

3、DRAM存儲電容

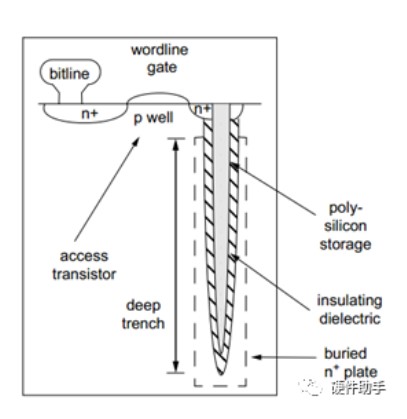

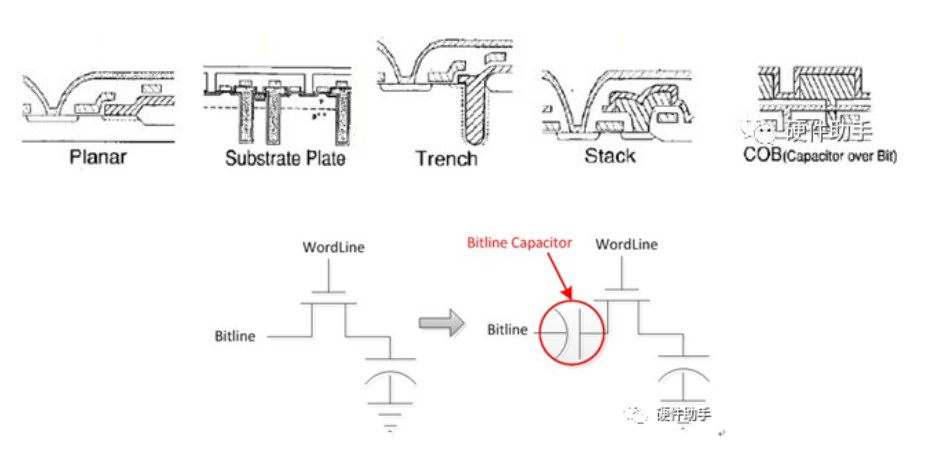

關(guān)于存儲電容在現(xiàn)代業(yè)界也沒有統(tǒng)一,存在兩大陣營,分別是堆電容(Stacked Capacitor)與溝電容(Trench Capacitor),像三星這樣的公司使用前者。因?yàn)檫@兩種電容在任何DRAM中都是存在的而且是需要考慮到的。trench電容是存在于深入到硅下面的,而stacked電容是存在于不同的多晶硅層中間。這兩種電容分別有自己的優(yōu)缺點(diǎn):

trench電容是深入到硅下面的,相當(dāng)于從二維到三維的拓展,可以保證在相同的電荷容量下,面積小,成本低,由于其表面平坦更易制造,使它更易集成到邏輯優(yōu)化工藝技術(shù)里。由于深入到硅下面的,在上層的邏輯電路結(jié)構(gòu)形成之前就存在,與上層電路無關(guān),有利于電路優(yōu)化。

堆電容是在硅表面形成像高層建筑那樣的結(jié)構(gòu),可以有效地利用芯片面積,但工藝復(fù)雜,成本較高。關(guān)于stacked電容,由于是存在不同的多晶硅層之間的,因此bitline與多晶硅之間也會存在電容,且這種電容屬于stacked電容。

溝電容(Trench Capacitor)的示意如下圖所示:

堆電容(Stacked Capacitor)的示意如下圖所示:

平面型、襯底基板深槽型、深槽型、堆疊型、電容器在位線上方堆疊型的具體示意如下圖所示:

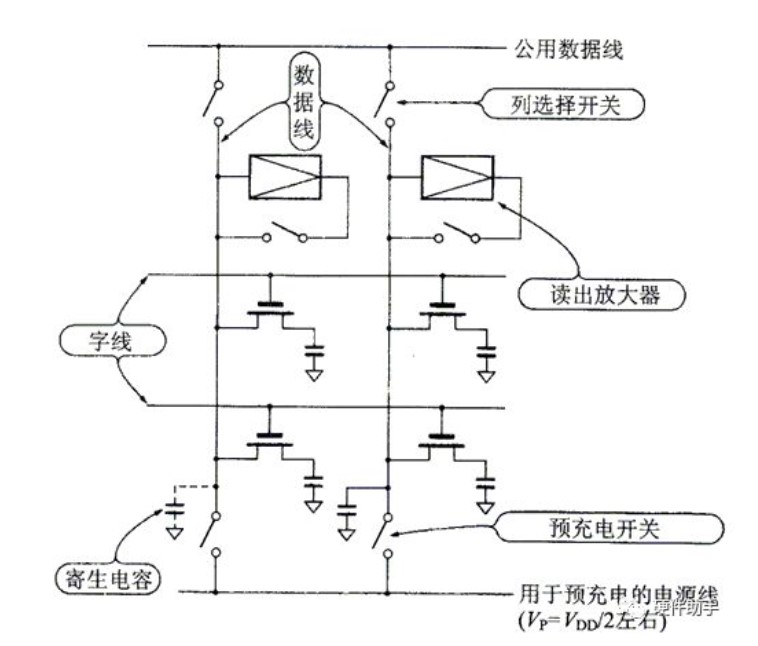

由于每個(gè)Bitline上連著很多并聯(lián)的Bitline Capacitor,因此存儲電容大小遠(yuǎn)比Bitline電容小,大約只有1/10。所以當(dāng)transistor選通時(shí),存儲在存儲電容上的電荷傳輸?shù)紹itline時(shí),Bitline上的電壓變化很小,需要使用差分比較放大器(此差分比較放大器非模擬集成電路中的差放,而是通過跟參考電壓作對比)。

DRAM的行選通和列選通信號將使存儲電容與外界間的傳輸電路導(dǎo)通,從而可進(jìn)行放電(讀取)和充電(寫入)。

在高密度的DRAM中,存儲器的單元電容決定了讀出信號電壓、讀出速度、數(shù)據(jù)保持時(shí)間和抗軟錯(cuò)誤容限。每一個(gè)存儲單元堆電容或溝電容容量為fF級(一般認(rèn)為必須大于25fF)。增加單元電容的一個(gè)主要策略是增加存儲器單元電容器的面積和降低介質(zhì)薄膜厚度(單位為F:FeatureLength,F(xiàn)2:Feature Dimension)。

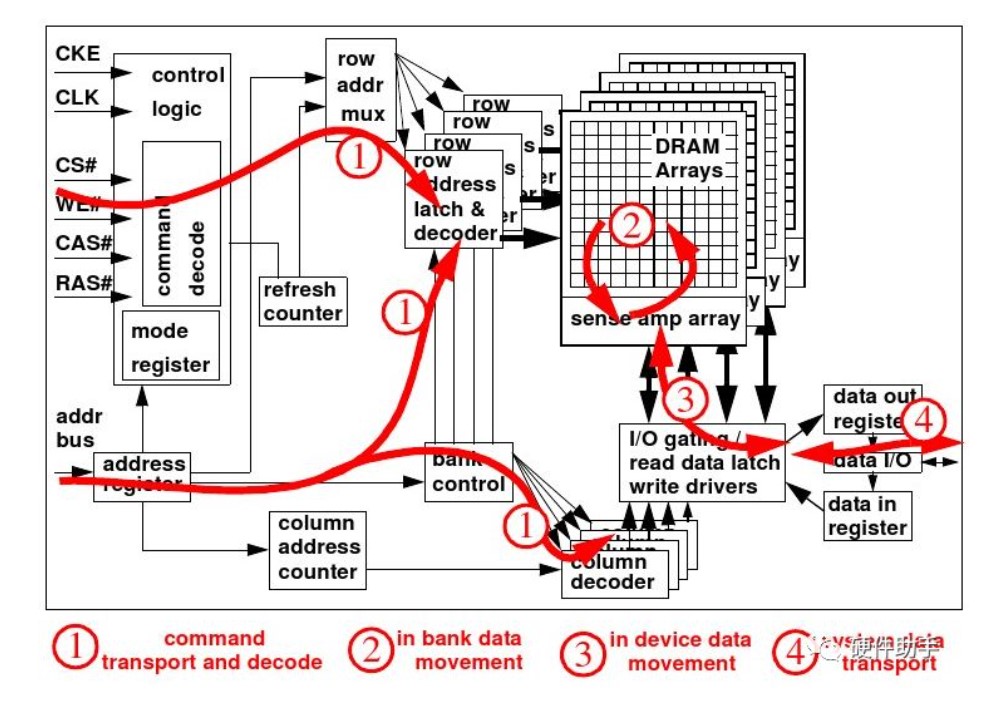

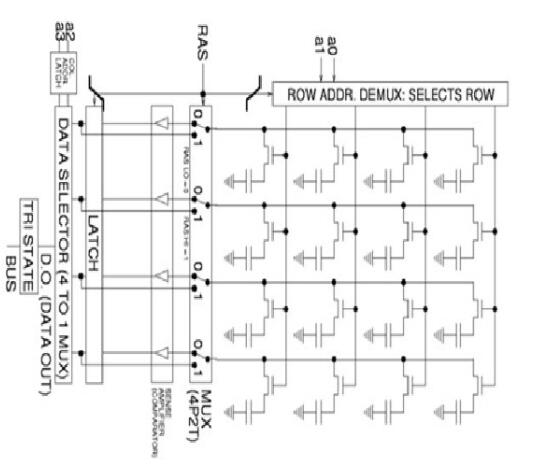

DRAM內(nèi)部結(jié)構(gòu)如下圖所示:

4、L-Bank&P-Bank

4.1、邏輯BANK

在芯片的內(nèi)部,DRAM的數(shù)據(jù)是以bit為單位寫入一張大的矩陣中,每個(gè)單元我們稱為CELL,只要指定一個(gè)行(Row),再指定一個(gè)列(Column),就可以準(zhǔn)確地定位到某個(gè)CELL,這就是內(nèi)存芯片尋址的基本原理。這個(gè)陣列我們就稱為內(nèi)存芯片的BANK,也稱之為邏輯BANK(Logical BANK)。由于工藝上的原因,這個(gè)陣列不可能做得太大,所以一般內(nèi)存芯片中都是將內(nèi)存容量分成幾個(gè)陣列來制造,也就是說內(nèi)存芯片中存在多個(gè)邏輯BANK,隨著芯片容量的不斷增加,邏輯BANK數(shù)量也在不斷增加,目前從32MB到1GB的芯片基本都是4個(gè),只有早期的16Mbit和32Mbit的芯片采用的還是2個(gè)邏輯BANK的設(shè)計(jì),譬如三星的兩種16MB芯片:K4S161622D(512K×16Bit×2 BANK)和K4S160822DT(1M×8bit×2 BANK)。芯片組本身設(shè)計(jì)時(shí)在一個(gè)時(shí)鐘周期內(nèi)只允許對一個(gè)邏輯BANK進(jìn)行操作(實(shí)際上芯片的位寬就是邏輯BANK的位寬),而不是芯片組對內(nèi)存芯片內(nèi)所有邏輯BANK同時(shí)操作。邏輯BANK的地址線是通用的,只要再有一個(gè)邏輯BANK編號加以區(qū)別就可以了(BANK0到BANK3)。但是這個(gè)芯片的位寬決定了一次能從芯片內(nèi)部讀出多少數(shù)據(jù),并不是內(nèi)存芯片里所有單元的數(shù)據(jù)一次全部能夠讀出。

每個(gè)邏輯BANK有8M個(gè)單元格(CELL),一些廠商(比如現(xiàn)代/三星)就把每個(gè)邏輯BANK的單元格數(shù)稱為數(shù)據(jù)深度(Data Depth),每個(gè)單元由8bit組成,那么一個(gè)邏輯BANK的總?cè)萘烤褪?4Mbit(8M×8bit),4個(gè)邏輯BANK就是256Mbit,因此這顆芯片的總?cè)萘烤褪?56Mbit(32MB)。

內(nèi)存芯片的容量是一般以bit為單位的。可以根據(jù)芯片上的標(biāo)識知道,這個(gè)芯片有幾個(gè)邏輯BANK,每個(gè)邏輯bank的位寬是多少,每個(gè)邏輯BANK內(nèi)有多少單元格(CELL),比如64MB和128MB內(nèi)存條常用的64Mbit的芯片就有如下三種結(jié)構(gòu)形式:

16M×4bit=4M×4bit×4banks

8M×8bit=2M×8bit×4banks

4M×16bit=1M×16bit×4banks

存儲單元數(shù)量=行數(shù)×列數(shù)(一個(gè)L-Bank的存儲單元數(shù)量)×L-Bank的數(shù)量。芯片邏輯BANK位寬目前的工藝水平只能最多做到16位,因此大家看到幾乎所有的芯片邏輯BANK位寬只可能4/8/16三者之一。以前16Mbit的芯片基本采用的單個(gè)芯片兩個(gè)邏輯BANK,但是到了64Mbit基本就都是4個(gè)邏輯BANK設(shè)計(jì)了。

4.2、物理BANK

內(nèi)存系統(tǒng)為了保證CPU正常工作,必須一次傳輸完CPU在一個(gè)傳輸周期內(nèi)所需要的數(shù)據(jù),而CPU在一個(gè)傳輸周期能接收的數(shù)據(jù)容量就是CPU數(shù)據(jù)總線的位寬,這個(gè)位寬就稱為物理BANK的位寬。

本文主要介紹DRAM的存儲原理、存儲電容、存儲結(jié)構(gòu)等內(nèi)容。后續(xù)會針對SDRAM和DDR等具體類型進(jìn)行詳細(xì)介紹。

審核編輯:劉清

-

DRAM

+關(guān)注

關(guān)注

40文章

2325瀏覽量

183766 -

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42679 -

GDDR

+關(guān)注

關(guān)注

0文章

27瀏覽量

4673

原文標(biāo)題:MEMORY系列之“DRAM概述”

文章出處:【微信號:半導(dǎo)體設(shè)備與材料,微信公眾號:半導(dǎo)體設(shè)備與材料】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

DRAM設(shè)計(jì)原理:DRAM Storage Cell 的結(jié)構(gòu)分析

淺析DRAM和Nand flash

DRAM存儲原理和特點(diǎn)

DRAM與NAND概述及差別

易失性存儲DRAM是什么,它的主要原理是怎樣的

DRAM存儲電容概述

DRAM存儲電容概述

評論