之前我們跟隨金譽半導體有了解過,CP測試和FT測試是芯片測試中的兩個模塊。

CP是Chip Probe的縮寫,指的是芯片在wafer的階段,就通過探針卡扎到芯片管腳上對芯片進行性能及功能測試,有時候這道工序也被稱作WS(Wafer Sort)。

FT是Final Test的縮寫,指的是芯片在封裝完成以后進行的最終測試,只有通過測試的芯片才會被出貨。

從工序角度上看,似乎非常容易區分cp測試和ft測試,沒有必要再做區分,而且有人會問,封裝前已經做過測試把壞的芯片篩選出來了,封裝后為什么還要進行一次測試呢?難道是封裝完成度不高影響了芯片的動能嗎?不是的,因為從測試內容上看,cp測試和ft測試有著非常明顯的不同。

首先受測試治具的限制,在絕大多數情況下,特別是國內,在CP測試上選用的探針基本屬于懸臂針(也有叫環氧針的,因為針是用環氧樹脂固定的緣故)。這種類型的針比較長,而且是懸空的,因此信號完整性控制非常困難,數據的最高傳輸率只有100~400Mbps,高速信號的測試幾乎不可能完成。

而且,探針和pad的直接接觸在電氣性能上也有局限,容易產生漏電和接觸電阻,這對于高精度的信號測量也會帶來巨大的影響。所以,通常CP測試僅僅用于基本的連接測試和低速的數字電路測試。

雖然理論上在CP階段也可以進行高速信號和高精度信號的測試,但這往往需要采用專業的高速探針方案,如垂直針/MEMS探針等技術,這會大大增加硬件的成本。多數情況下,這在經濟角度上來說是不劃算,因此在CP測試階段只能選擇傳輸率不太高,對良率影響較大的測試項目。

于是,一些測試難度大,成本高但信號率不高的測試項目,完全可以放到FT階段再測試。也是因為一些芯片的部分模組的管腳在封裝之前都不會引出來,在FT階段很難甚至無法測量,如芯片的封裝是SIP之類的特殊形式。在這樣的情況下,有些測試就必須在CP階段進行,這也是在封裝前還需要進行CP測試的一個重要原因。

因此,cp測試和ft測試的區別就是

1) 因為封裝本身可能影響芯片的良率和特性,所以芯片所有可測測試項目都是必須在FT階段測試一遍的,而CP階段則是可選。

2) CP階段原則上只測一些基本的DC,低速數字電路的功能,以及其它一些容易測試或者必須測試的項目。凡是在FT階段可以測試,在CP階段難于測試的項目,能不測就盡量不測。一些類似ADC的測試,在CP階段可以只給幾個DC電平,確認ADC能夠基本工作。在FT階段再確認具體的SNR/THD等指標。

3) 由于CP階段的測試精度往往不夠準確,可以適當放寬測試判斷標準,只做初步篩選。精細嚴格的測試放到FT階段。

4) 如果封裝成本不大,且芯片本身良率已經比較高。可以考慮不做CP測試,或者CP階段只做抽樣測試,監督工藝。

5) 新的產品導入量產,應該先完成FT測試程序的開發核導入。在產品量產初期,FT遠遠比CP重要。等產品逐漸上量以后,可以再根據FT的實際情況,制定和開發CP測試。

了解了它們之間的不同,我們還可以根據測試項目的不同和重復內容等因素,在具體測試項目中進行判斷和取舍了。畢竟增加一個復雜的高速或高精度模擬測試,不僅僅會增加治具的成本,還會增加測試機臺的費率和延長測試時間,影響出產成果。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

51140瀏覽量

426150 -

半導體

+關注

關注

334文章

27673瀏覽量

221366

發布評論請先 登錄

相關推薦

Advantest CEO:先進芯片測試需求大增

芯片極限能力、封裝成品及系統級測試

季豐電子完成自研Acco8200_CP_Generic_Board公板測試驗證

CP測試與FT測試有什么區別

IC測試基本原理與ATE測試向量生成

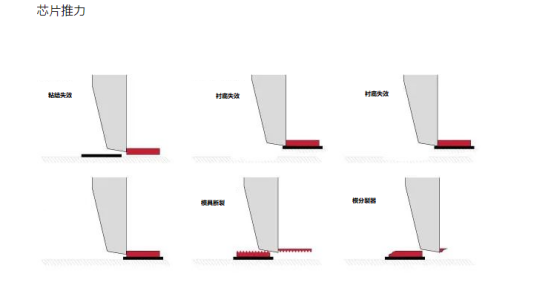

想了解芯片推力測試?點擊這里,了解最新測試方法!

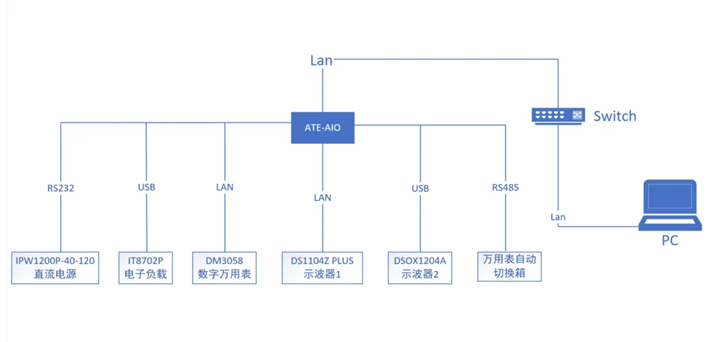

怎么測試4644電源管理芯片?需要哪些測試設備?

半導體制造的關鍵環節:芯片測試

芯片的出廠測試與ATE測試的實施方法

為什么要進行芯片測試?芯片測試在什么環節進行?

如何區分芯片CP測試和FT測試

如何區分芯片CP測試和FT測試

評論