本文就芯片測(cè)試做一個(gè)詳細(xì)介紹。

芯片的測(cè)試大致可以分成兩大部分。CP(chip probering)和FT(final test)。某些芯片還會(huì)進(jìn)行SLT(system leve test)。還有一些特定要求的芯片,需要一些可靠性測(cè)試。

CP測(cè)試

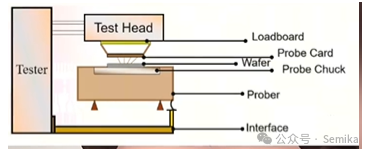

CP(Chip Probing)測(cè)試也叫晶圓測(cè)試(wafer test),也就是在芯片未封裝之前對(duì)wafer進(jìn)行測(cè)試,這樣就可以把有問題的芯片在封裝之前剔除出來,節(jié)約封裝FT的成本。CP測(cè)試在整個(gè)芯片制作流程中處于晶圓制造和封裝之間。晶圓(Wafer)制作完成之后,成千上萬的裸DIE(未封裝的芯片)規(guī)則地布滿整個(gè)Wafer。由于尚未進(jìn)行劃片封裝,芯片的管腳全部裸露在外,這些極微小的管腳需要通過更細(xì)的探針(Probe)來與測(cè)試機(jī)臺(tái)(Tester)連接。

下圖為CP自動(dòng)化測(cè)試系統(tǒng)示意圖。

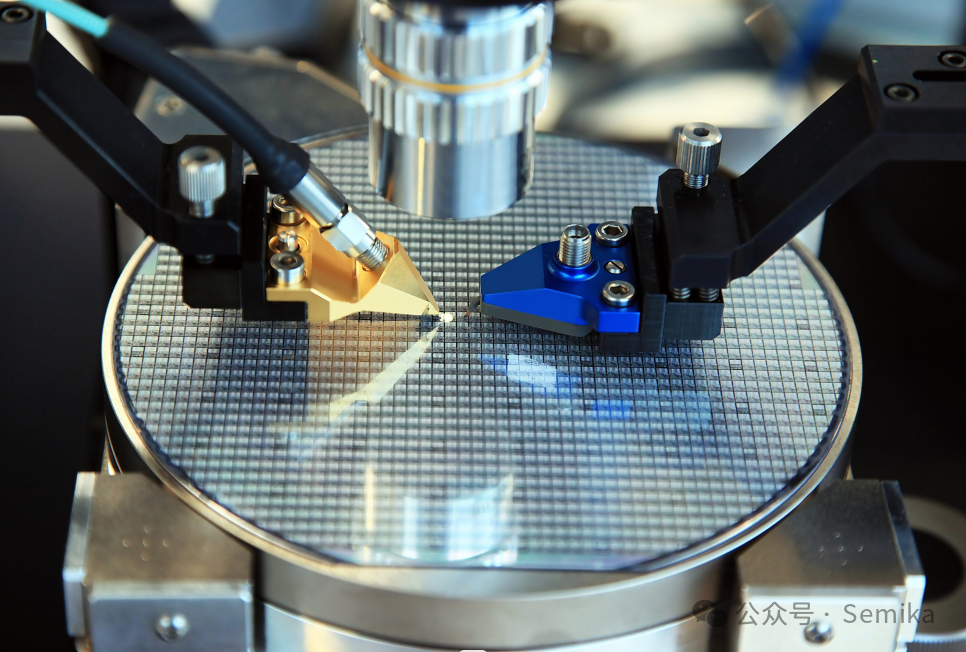

可以把CP想成下圖的測(cè)試樣子,用探針Probe來進(jìn)行測(cè)試晶圓:

但應(yīng)用中,探針的數(shù)量非常的多,會(huì)使用幾千上萬個(gè)探針做的探針臺(tái)。探針臺(tái),是用來承載wafer的平臺(tái),讓wafer內(nèi)的每顆die每個(gè)bond pads 都能連接到Probe card的探針上,同時(shí)能夠精確地移位,每次測(cè)試之后,換另外的die再一次連接到Probe card的探針上,從而保證wafer上的每一個(gè)die都被測(cè)試到。高端探針臺(tái)目前大部分為國外品牌壟斷,中低端市場(chǎng)基本由國內(nèi)探針臺(tái)廠家占據(jù),也有部分中高端市場(chǎng)逐漸被國產(chǎn)替代。

CP測(cè)試主要測(cè)以下幾方面的內(nèi)容:

- SCAN。SCAN用于檢測(cè)芯片邏輯功能是否正確。

- Boundary SCAN。Boundary SCAN用于檢測(cè)芯片管腳功能是否正確。

- 存儲(chǔ)器。芯片往往集成著各種類型的存儲(chǔ)器(例如ROM/RAM/Flash),為了測(cè)試存儲(chǔ)器讀寫和存儲(chǔ)功能,通常在設(shè)計(jì)時(shí)提前加入BIST(Built-In SelfTest)邏輯,用于存儲(chǔ)器自測(cè)。芯片通過特殊的管腳配置進(jìn)入各類BIST功能,完成自測(cè)試后BIST模塊將測(cè)試結(jié)果反饋給Tester。

- DC/AC Test。DC測(cè)試包括芯片Signal PIN的Open/Short測(cè)試,電源PIN的PowerShort測(cè)試,以及檢測(cè)芯片直流電流和電壓參數(shù)是否符合設(shè)計(jì)規(guī)格

- RF Test。對(duì)于無線通信芯片,RF的功能和性能至關(guān)重要。CP中對(duì)RF測(cè)試來檢測(cè)RF模塊邏輯功能是否正確。FT時(shí)還要對(duì)RF進(jìn)行更進(jìn)一步的性能測(cè)試。

其他Function Test。芯片其他功能測(cè)試,用于檢測(cè)芯片其他重要的功能和性能是否符合設(shè)計(jì)規(guī)格。

測(cè)試機(jī)需要根據(jù)測(cè)試的內(nèi)容進(jìn)行選擇,有很多品牌和產(chǎn)品系列:例如存儲(chǔ)器芯片Advantest T55xx 系列等、數(shù)字混合信號(hào)或SoC芯片Teradyne J750 系列等,RF射頻芯片Credence ASL-3000 系列等。

FT(final test)測(cè)試

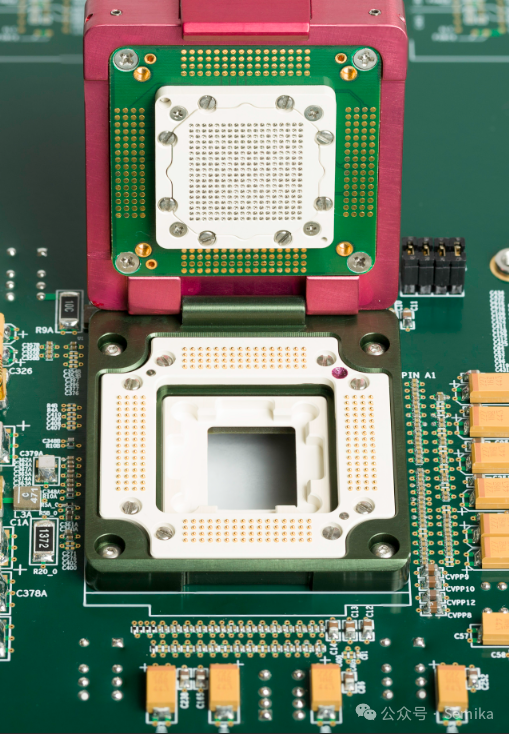

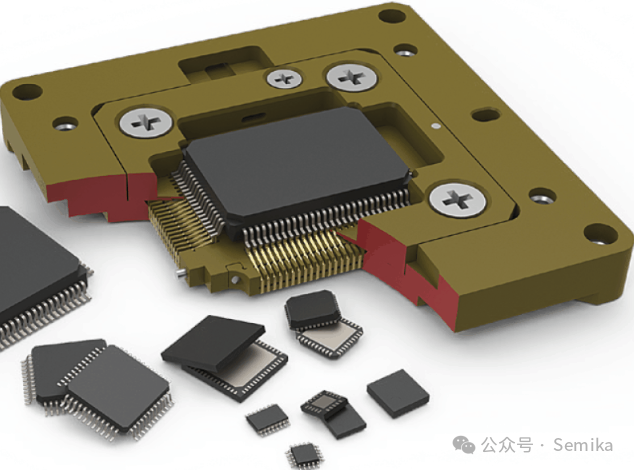

FT(final test)測(cè)試就是最終測(cè)試,在芯片完成封裝之后進(jìn)行的測(cè)試。FT測(cè)試屬于芯片級(jí)測(cè)試,是通過測(cè)試板(Loadboard)和測(cè)試插座(Socket)使自動(dòng)化測(cè)試設(shè)備(ATE)到封裝后的芯片之間建立電氣連接。FT測(cè)試的目的是篩選出滿足設(shè)計(jì)規(guī)格的產(chǎn)品賣給客戶。

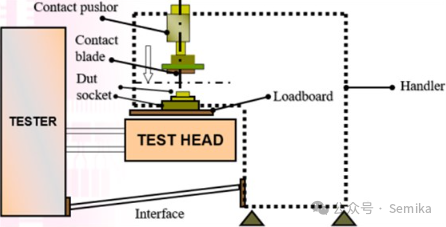

FT的測(cè)試系統(tǒng)結(jié)構(gòu)如下圖:

FT測(cè)試需要的硬件設(shè)備包括測(cè)試板、測(cè)試插座、ATE(Automation Test Equi[pment)測(cè)試機(jī)臺(tái)、Handler。其中Handler也稱為自動(dòng)化分類機(jī),是用來實(shí)現(xiàn)FT測(cè)試自動(dòng)化的設(shè)備。

handler與tester相結(jié)合以及連上了interface之后才能測(cè)試。動(dòng)作就是handler的手臂將芯片放進(jìn)socket,然后contact pusher下壓。使芯片的引腳正確的和socket的接觸送出start信號(hào),透過interface 給tester,測(cè)試完成之后tester送回binning及EOT(end of test)訊號(hào)。handler再做出分類的動(dòng)作。

? ?

? ? ?

?

FT測(cè)試項(xiàng)目也是根據(jù)芯片的功能和特性決定的。常見的FT測(cè)試項(xiàng)一般有:

Open/short test,也就是檢查芯片引腳是否有開路或者短路,

DC test也就是檢查器件直流的電流和電壓的參數(shù)。

Eflash test也就是檢查內(nèi)嵌的flash功能和性能,包含讀寫參數(shù)動(dòng)作功耗和速度等各種參數(shù)。

Function test就是測(cè)試芯片的邏輯功能,

AC test就是驗(yàn)證交流的規(guī)格,包括交流輸出信號(hào)的質(zhì)量和信號(hào)的實(shí)際參數(shù)。

RF test這個(gè)就是針對(duì)有射頻模塊的芯片,主要驗(yàn)證射頻模塊的功能和性能參數(shù)。

還有就是DFT test,DFT(Design forTest) test主要包括scan掃描設(shè)計(jì)和內(nèi)件的自測(cè),也就是BIST(Build In Self Test)。

SLT測(cè)試

SLT是System Level Test的縮寫。SLT一種是在其他測(cè)試覆蓋率無法滿足時(shí)使用。還有一種就是為了控制成本,因?yàn)锳TE的測(cè)試成本比較高。SLT的測(cè)試把芯片放在測(cè)試板上,測(cè)試板可以用于驗(yàn)證芯片的各個(gè)功能。因?yàn)樗麄兛刂贫嗯_(tái)測(cè)試機(jī),這樣可以實(shí)現(xiàn)批量的測(cè)試。

SLT測(cè)試需要的硬件設(shè)備包括測(cè)試板、測(cè)試插座、Handler、Change Kit以及測(cè)試主機(jī)與連接線等。SLT測(cè)試屬于定制化測(cè)試,軟件部分靈活度比較高,不需要基于自動(dòng)化測(cè)試平臺(tái)開發(fā),完全由測(cè)試工程師自主開發(fā)。SLT測(cè)試內(nèi)容通常包括芯片功能測(cè)試、高速接口測(cè)試以及DDR內(nèi)存相關(guān)的測(cè)試等。與FT測(cè)試相同,程序會(huì)根據(jù)測(cè)試結(jié)果Pass或者Fail對(duì)芯片進(jìn)行物理分Bin。

以上三種主要測(cè)試之外 ,有的芯片可能還要進(jìn)行一些可靠性測(cè)試,包括以下內(nèi)容:

ESD,也就是靜電抗擾度測(cè)試

Lateh up就是閂鎖測(cè)試

HTOL就是高溫工作壽命測(cè)試

LTOL就是低溫工作壽命測(cè)試

TCT溫度循環(huán)測(cè)試

HAST高加速溫度溫濕度應(yīng)力測(cè)試

其他特殊要求的測(cè)試

-

晶圓

+關(guān)注

關(guān)注

52文章

4957瀏覽量

128185 -

芯片測(cè)試

+關(guān)注

關(guān)注

6文章

134瀏覽量

20167 -

可靠性測(cè)試

+關(guān)注

關(guān)注

1文章

90瀏覽量

14203

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

IC測(cè)試原理——芯片測(cè)試原理

芯片測(cè)試及測(cè)試方法有哪些?

芯片測(cè)試的功能介紹

芯片測(cè)試座在IC芯片測(cè)試中的作用

芯片封裝測(cè)試有技術(shù)含量嗎?封裝測(cè)試是干嘛的?

芯片電學(xué)測(cè)試是什么?都有哪些測(cè)試參數(shù)?

IC芯片測(cè)試基本原理是什么?

如何測(cè)試電源芯片負(fù)載調(diào)整率呢?有哪些測(cè)試規(guī)范呢?

如何用集成電路芯片測(cè)試系統(tǒng)測(cè)試芯片老化?

電源芯片測(cè)試指標(biāo)大全

芯片的出廠測(cè)試與ATE測(cè)試的實(shí)施方法

芯片測(cè)試有哪些 芯片測(cè)試介紹

芯片測(cè)試有哪些 芯片測(cè)試介紹

評(píng)論