今天介紹幾個和圖像處理的項目,廢話不多說,我們開始吧~

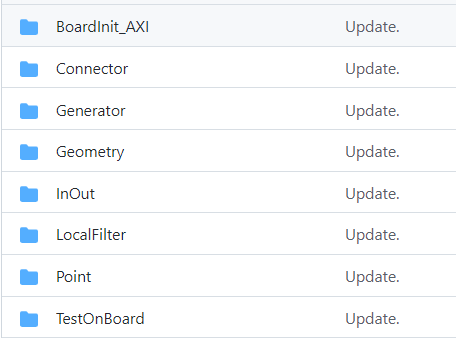

FPGA-Imaging-Library

https://github.com/dtysky/FPGA-Imaging-Library

介紹

一個開源的FPGA圖像處理庫。

F-I-L是一個FPGA平臺的開源的圖像處理庫,已經(jīng)擁有了許多常用操作,并在不斷更新中。這些操作被以IP核的形式進行了封裝,遵循同一種規(guī)范化的接口,同時具有流水線和請求響應(yīng)兩種使用模式。

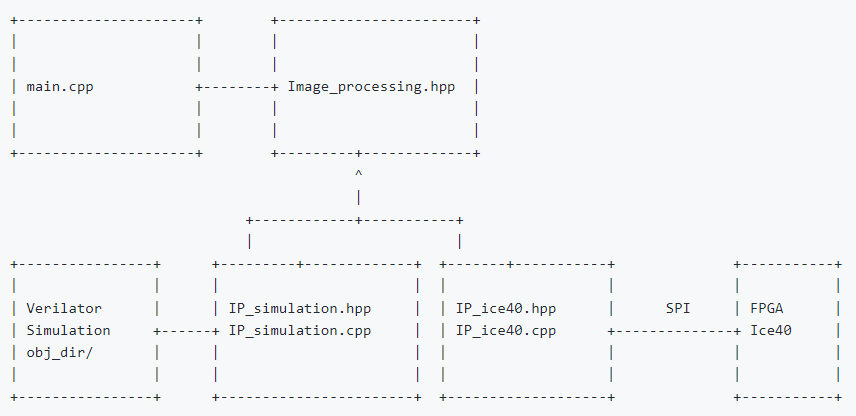

fpga_image_processing

https://github.com/damdoy/fpga_image_processing

介紹

少邏輯量FPGA圖像處理庫。在verilog中實現(xiàn)簡單的圖像處理操作,該項目圍繞一個中央圖像處理模塊展開image_processing.v,該模塊使用 verilator 仿真。在ICE40 FPGA上實現(xiàn)。

因為它針對的是低端 fpga 設(shè)備(無論是價格還是功耗),例如 ice40 ultraplus。它使用 1Mbit 的 ram 將圖像存儲到兩個緩沖區(qū)中,即輸入緩沖區(qū)和存儲緩沖區(qū)。圖像在輸入緩沖區(qū)中加載和讀取,計算在存儲緩沖區(qū)中完成。這兩個緩沖區(qū)可以交換。大多數(shù)操作將在存儲緩沖區(qū)中完成,如果對兩個圖像應(yīng)用操作(例如 binary_add),則生成的圖像將寫入存儲緩沖區(qū)。

架構(gòu)

ImageStitchBasedOnFPGA

https://github.com/mhhai/ImageStitchBasedOnFPGA

七路攝像頭拼接

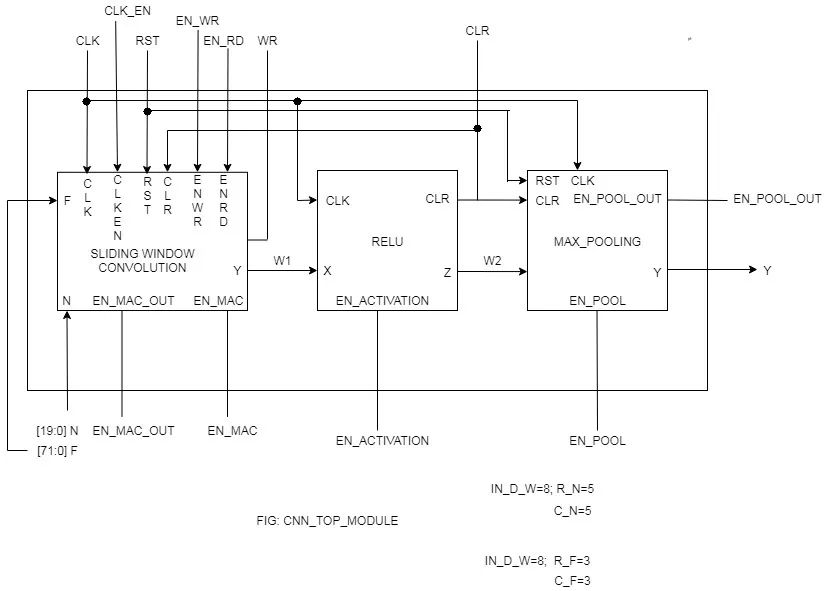

Image-Classification-using-CNN-on-FPGA

https://github.com/padhi499/Image-Classification-using-CNN-on-FPGA

項目是關(guān)于在 FPGA 上設(shè)計一個經(jīng)過訓練的神經(jīng) n/w(CIFAR-10 數(shù)據(jù)集),以使用深度學習概念(CNN-卷積神經(jīng)網(wǎng)絡(luò))對圖像 I/P 進行分類。

有 6 層(滑動窗口卷積、ReLU 激活、最大池化、扁平化、完全連接和 Softmax 激活)決定了我們的 I/P 圖像的類別。Kernels/Filters用于從圖像 I/P 進行特征檢測。圖像 I/P 可以是灰度/彩色的。

使用的工具

賽靈思 Vivado v17.4

使用的語言

Verilog HDL

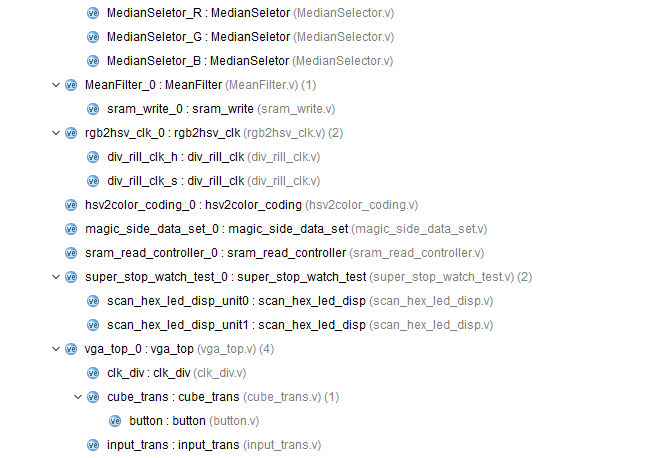

Image_sim

https://github.com/Bestduan/Image_sim

介紹

基于FPGA的圖像處理模塊(出自于crazybingo)(將里面的Intel的shift_RAM以及altsqrt的IP核換為Verilog來實現(xiàn),方便實現(xiàn)跨平臺移植)

含有圖像的仿真模塊

文件結(jié)構(gòu)基于vscode下FPGA_Develop_Support插件

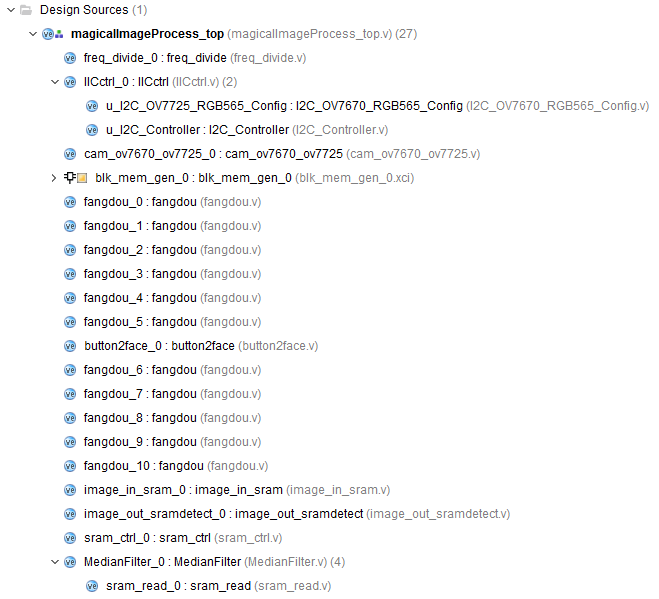

魔方圖像處理

https://github.com/IdlessChaye/magicalcubeImageProcess

功能

使用ov7725獲取magiccube表面正確位置的像素,通過hsv編碼轉(zhuǎn)換為3位顏色編碼。

輸出

6 個魔方表面 * 9 個正方形 * 3 位顏色編碼。

板卡

Xilinx FPGA EGO1 xc7a35tcsg324

microshift_compression

https://github.com/zhangmozhe/microshift_compression

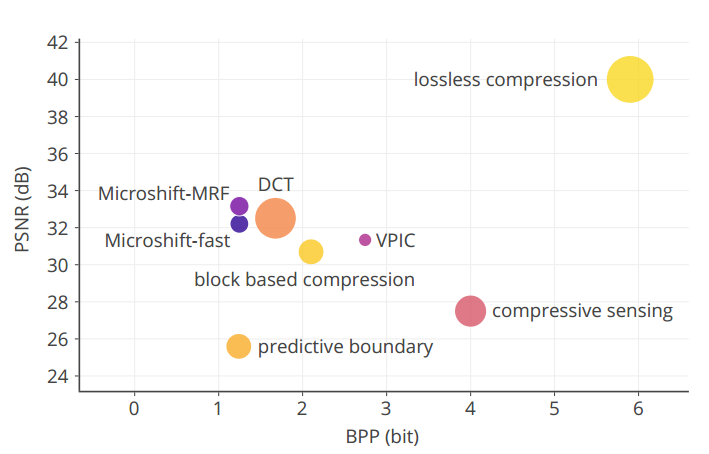

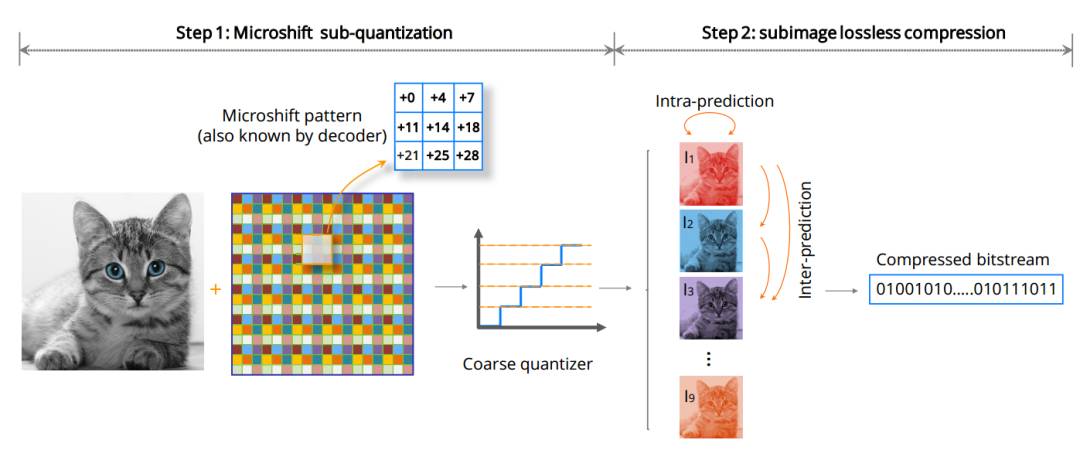

Microshift:一種高效的硬件圖像壓縮算法

這是 TCSVT 論文“Microshift: An Efficient Image Compression Algorithm for Hardware”的 Matlab 和 Verilog 實現(xiàn)

-

Arxiv 論文:https ://arxiv.org/abs/2104.09820

-

IEEE 鏈接:https ://ieeexplore.ieee.org/document/8529272

-

Github 代碼:https ://github.com/zhangmozhe/microshift_compression

-

綜合教程:https ://github.com/zhangmozhe/microshift_compression/tree/master/VLSI%20design%20flow

描述

Microshift是一種有損圖像壓縮算法,可以在硬件上以極低的功耗高效實現(xiàn)。

- 在數(shù)據(jù)集上進行測試時,它可以將圖像壓縮到1.25 BPP,其結(jié)果質(zhì)量優(yōu)于最先進的片上壓縮算法 ( PSNR=33.16, SSIM=0.90 )。

- 提出了一種高效的 VLSI 架構(gòu),并在 FPGA 上實現(xiàn)。

- ASIC 設(shè)計的結(jié)果進一步驗證了低硬件復雜性和高功率效率。

- 我們的方法有望用于低功耗無線視覺傳感器網(wǎng)絡(luò)(WVSN)。

論文

https://github.com/zhangmozhe/microshift_compression/blob/master/paper.pdf

HDR

https://github.com/markos-stefanidis/FPGA-Based-HDR-algorithm

https://github.com/sh-vlad/FPGA_rtime_HDR_video

matlab-imageprocess

https://github.com/LiaoYuxuan/matlab-imageprocess

最后就是一些資料了,主要是圖像處理算法,核心是岡薩雷斯數(shù)字圖像處理MATLAB版本。

總結(jié)

終于介紹完了SNN、TPU、CNN和DNN,今天推薦幾個視頻/圖像處理的項目,說實話其實這方面內(nèi)容比較少,項目也是比較老舊,因為這方面內(nèi)容太多,已經(jīng)發(fā)展了幾十年了,ASIC在這方面基本都滿足了常規(guī)應(yīng)用,所以在FPGA方面基本停滯不前了。但是國內(nèi)像CrazyBingo等大佬還在這方面繼續(xù)耕耘。后續(xù)我也準備追隨大佬們的腳步出系列教程(圍繞ISP)。

最后,還是感謝各個大佬開源的項目,讓我們受益匪淺。后面有什么感興趣方面的項目,大家可以在后臺留言或者加微信留言,今天就到這,我是爆肝的碎碎思,期待下期文章與你相見。

審核編輯 :李倩

-

圖像處理

+關(guān)注

關(guān)注

27文章

1299瀏覽量

56837 -

算法

+關(guān)注

關(guān)注

23文章

4627瀏覽量

93166 -

開源

+關(guān)注

關(guān)注

3文章

3394瀏覽量

42629

原文標題:優(yōu)秀的 Verilog/FPGA開源項目介紹(二十五)- FPGA圖像處理庫

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

EE-276:Blackfin處理器上圖像處理的視頻框架注意事項

DFT在圖像處理中的作用 DFT在音頻信號處理中的應(yīng)用

傅立葉變換在圖像處理中的作用

LED視頻處理器對顯示質(zhì)量的影響

FPGA在圖像處理領(lǐng)域的優(yōu)勢有哪些?

ALINX FPGA+GPU異架構(gòu)視頻圖像處理開發(fā)平臺介紹

圖像處理器是什么意思

TMS320DM642視頻/圖像定點數(shù)字信號處理器數(shù)據(jù)表

SM320DM642-HiRel視頻/圖像定點數(shù)字信號處理器數(shù)據(jù)表

計算機視覺和圖像處理的區(qū)別和聯(lián)系

FPGA設(shè)計經(jīng)驗之圖像處理

Workshop!圖像處理和識別入門培訓

幾個視頻/圖像處理的項目分享

幾個視頻/圖像處理的項目分享

評論