1.1 VESA 視頻標準

VESA 視頻標準同步信號產生器,是從事FPGA圖像領域工程師經常使用到的模塊。首先,它的標準時序來自 VESA 視頻標準文件。

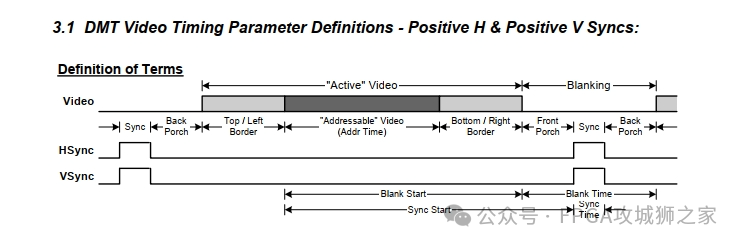

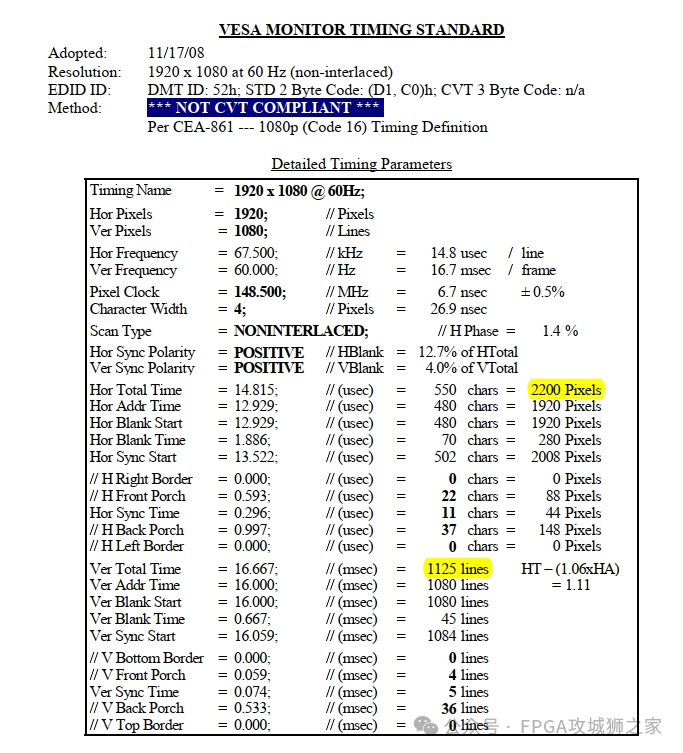

里面規定了VESA視頻流同步信號的時序,以1080p為例可以查詢到具體情況如下圖

1.2 產生視頻流同步信號

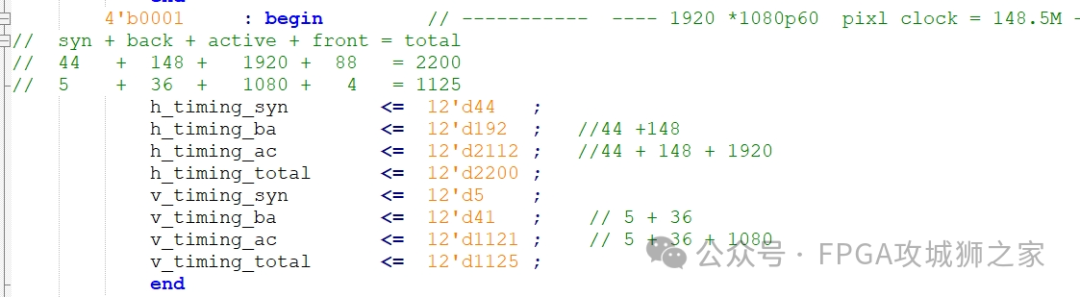

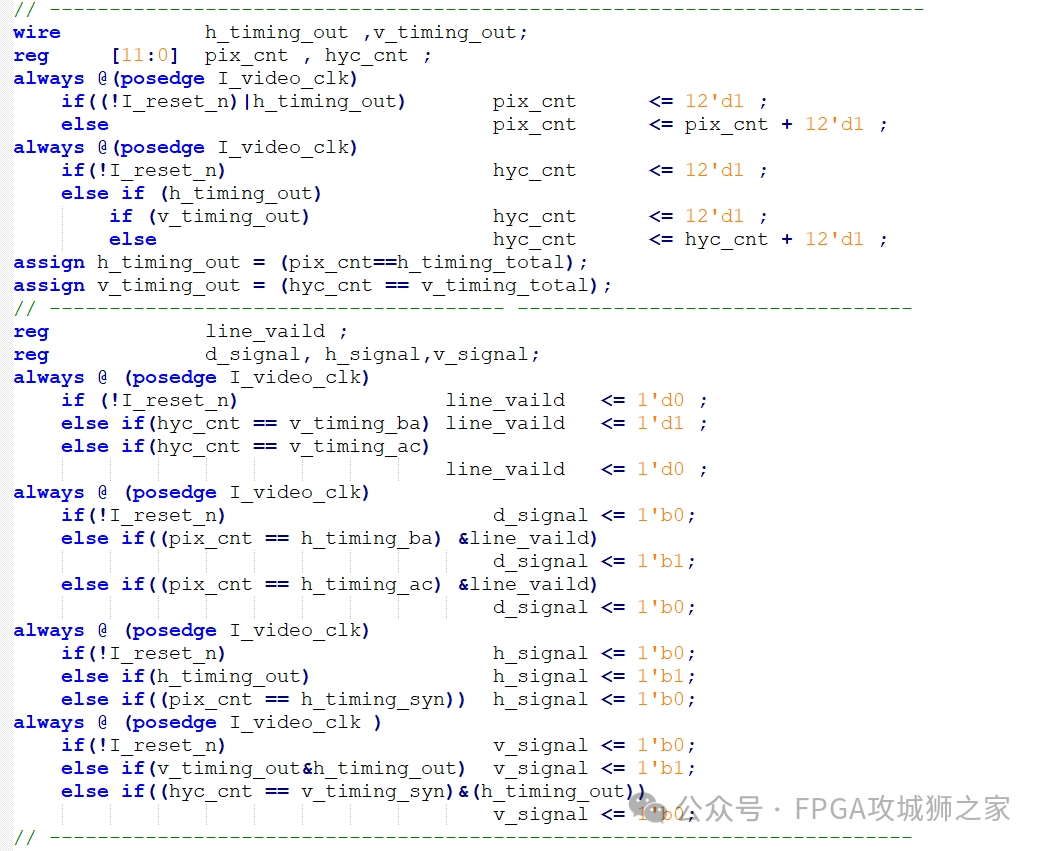

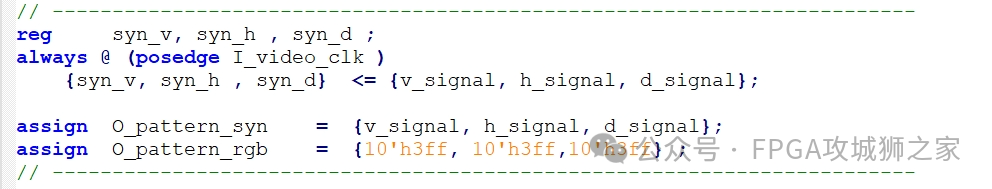

那么依照這個視頻流可以在FPGA中產生標準時序,首先將這些參數添加進去,看注釋中數據,就知道怎么填了。這樣任意的分辨率都可以產生了。

然后利用這個參數產生同步信號,自此任意同步信號產品器就完成了。有人會說,這個東西,不就是xilinx官方的IP VTC 嘛,干嘛要重復造輪子。嘿嘿,那是因為,一,我們在做圖像處理的時候要盡量的避免使用vivado這個仿真器,因為它實在是太墨跡了。二,如果是1080p以上的分辨率,比如4k,8k,的視頻流,它在FPGA里面是雙點,四點模式的,VTC沒有這個功能,這個就要靠自己去實現了。

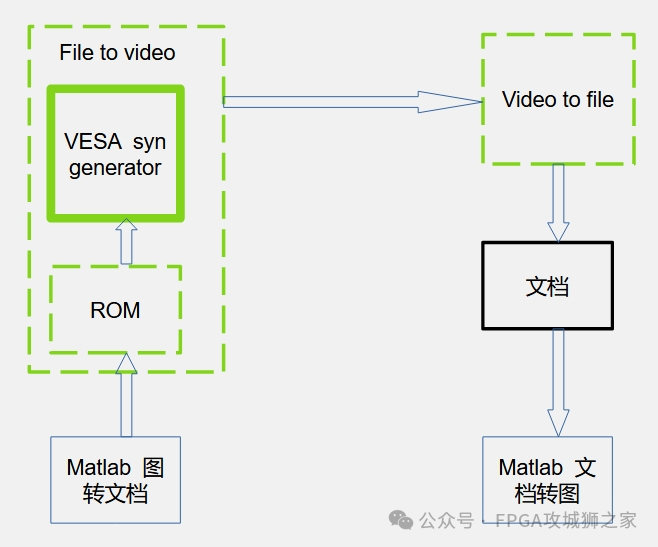

1.3 圖導入FPGA

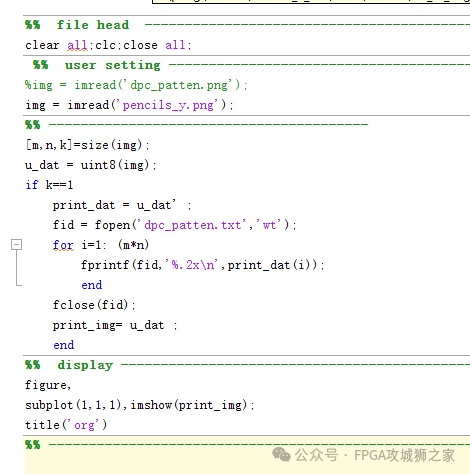

首先需要把圖轉換成txt,這個可以利用matlab

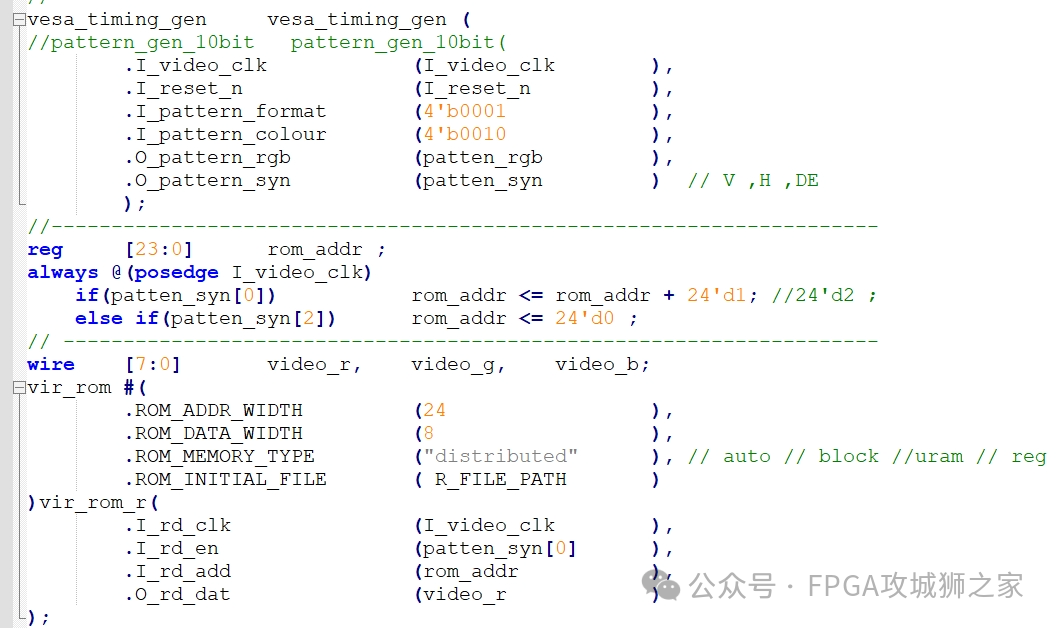

這是一張黑白圖導入到matlab中,然后再保存到txt中的程序。然后在FPGA中將txt導入到rom,利用VESA視頻流同步信號產生器,虛擬一條視頻輸入到代碼中。

vir_rom 就是一個虛擬的rom。利用VESA視頻流同步信號產生rom讀地址,從而把rom中的圖像數據導出來。

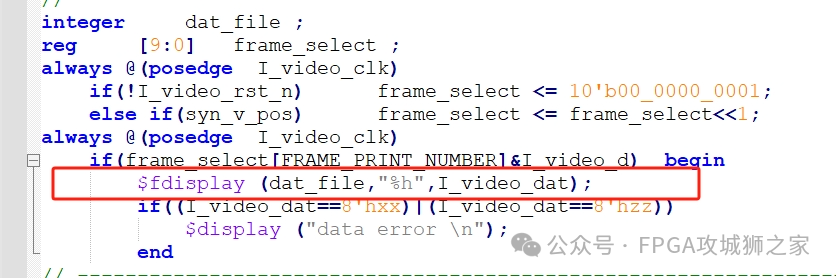

1.4 視頻到文件

仿真的下半場,就是將視頻流存入到文件中,這里需要寫一個視頻保存文件,選擇其中一幀保存下來。此時modelsim會產生一個txt文件,保存我們所需要的數據。

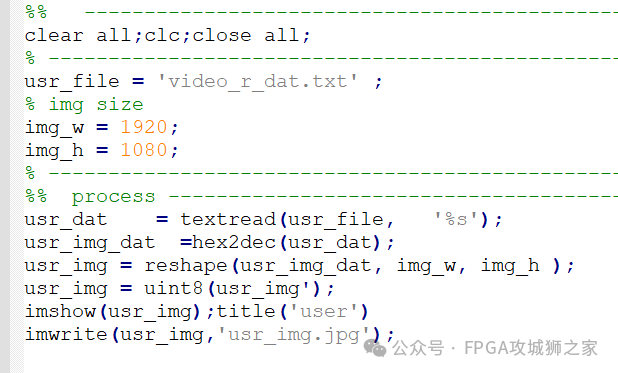

1.5 txt到圖像。

當我們拿到了modelsim里面的仿真視頻流一幀的文件txt,直接讀入到matlab里面去就好了。幾行代碼就完成了華麗的轉換。

自此,測試圖產生器就完成了。既可以放到可綜合項目中,也可以放到仿真工程中使用。自此,這個結構圖里面的內容就完成了。

審核編輯:劉清

-

FPGA

+關注

關注

1629文章

21744瀏覽量

603601 -

VESA

+關注

關注

0文章

15瀏覽量

12143 -

matlab

+關注

關注

185文章

2976瀏覽量

230526 -

圖像處理

+關注

關注

27文章

1292瀏覽量

56760 -

仿真器

+關注

關注

14文章

1018瀏覽量

83764

原文標題:FPGA圖像處理_VESA標準與視頻流

文章出處:【微信號:gh_99a29eb83412,微信公眾號:FPGA攻城獅之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種基于FPGA的實時視頻圖像處理算法研究與實現

FPGA實時視頻圖像處理系統的原理是什么?

基于FPGA的小型微光視頻圖像增強處理系統

一種基于DSP+FPGA視頻圖像采集處理系統的設計與實現

FPGA圖像處理—VESA標準與視頻流介紹

FPGA圖像處理—VESA標準與視頻流介紹

評論