近日,在日本東京舉辦的ITF論壇上,與ASML合作研發光刻機的比利時半導體研究機構IMEC公布了3nm及以下制程在微縮層面技術細節。

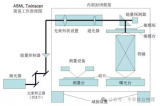

目前,ASML在3nm、2nm、1nm甚至Sub?1nm都已經做出了清晰的路徑規劃,據了解,1nm時代的光刻機在體積方面將會增加不少。

體積增加的主要原因是光學器件增大所致,潔凈室指數也達到天花板。

據悉,在臺積電、三星的7nm、5nm制造中已經引入了NA=0.33的EUV曝光設備,而在2nm后就需要更高分辨率的曝光設備,也就是NA=0.55。

現在,ASML已經完成了0.55NA曝光設備的基本設計(NXE:5000系列),預計將會在2022年實現商業化。

ASML目前在售的兩款極紫外光刻機分別是TWINSCAN?NXE:3400B和TWINSCAN?NXE:3400C,預計3600D計劃在明年年中出貨,其生產效率將會提升18%。

責任編輯:pj

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

三星電子

+關注

關注

34文章

15869瀏覽量

181177 -

光刻機

+關注

關注

31文章

1156瀏覽量

47516 -

ASML

+關注

關注

7文章

720瀏覽量

41288

發布評論請先 登錄

相關推薦

三星電子1c nm內存開發良率里程碑推遲

據韓媒報道,三星電子已將其1c nm DRAM內存開發的良率里程碑時間推遲了半年。原本,三星計劃在2024年底將

三星1c nm DRAM開發良率里程碑延期

(High Bandwidth Memory 4)內存規劃方面產生影響。 原本,三星電子計劃在2024年12月前將1c nm制程DRAM的良率提升至70%,這是結束開發工作并進入量產階

三星重啟1b nm DRAM設計,應對良率與性能挑戰

近日,據韓媒最新報道,三星電子在面對其12nm級DRAM內存產品的良率和性能雙重困境時,已于2024年底作出了重要決策。為了改善現狀,三星決定在優化現有1b

組成光刻機的各個分系統介紹

納米級別的分辨率。本文將詳細介紹光刻機的主要組成部分及其功能。 光源系統 ? 光源系統是光刻機的心臟,負責提供曝光所需的能量。早期的光刻機使用汞燈作為光源,但隨著技術的進步,目前多采用

三星減少NAND生產光刻膠使用量

近日,據相關報道,三星電子在3D NAND閃存生產領域取得了重要技術突破,成功大幅減少了光刻工藝中光刻膠的使用量。 據悉,三星已經制定了未來NAND閃存的生產路線圖,并計劃在這一生產過

用來提高光刻機分辨率的浸潤式光刻技術介紹

? 本文介紹了用來提高光刻機分辨率的浸潤式光刻技術。 芯片制造:光刻技術的演進 過去半個多世紀,摩爾定律一直推動著半導體技術的發展,但當光刻機的光源波長卡在193

光刻機的工作原理和分類

,是半導體產業皇冠上的明珠。芯片的加工過程對精度要求極高,光刻機通過一系列復雜的技術手段,將光束透射過畫著線路圖的掩模,經物鏡補償各種光學誤差,將線路圖成比例縮小后映射到硅片上,然后使用化學方法顯影,得到刻在硅片上的電路圖

今日看點丨 2011億元!比亞迪單季營收首次超過特斯拉;三星將于2025年初引進High NA EUV光刻機

1. 三星將于2025 年初引進High NA EUV 光刻機,加快開發1nm 芯片 ? 據報道,三星電子正準備在2025年初引入其首款Hi

發表于 10-31 10:56

?843次閱讀

三星電子計劃在2026年推出最后一代10nm級工藝1d nm

三星電子在最新的內存產品路線圖中透露了未來幾年的技術布局。據透露,三星計劃在2024年率先推出基于1c nm制程的DDR內存,該制程將支持高

三星欲提前量產1nm工藝,計劃2026年量產

據悉,三星電子晶圓代工部門將于6月12日至13日在美國硅谷舉行晶圓代工及SAFE論壇,期間將披露其技術發展藍圖以及強化晶圓代工生態系統的相關策略。

俄羅斯首臺光刻機問世

的一部分,目前正在對其進行測試,該設備可確保生產350nm的芯片。什帕克還指出,到2026年將獲得130nm的國產光刻機,下一步將是開發90nm

臺積電A16制程采用EUV光刻機,2026年下半年量產

據臺灣業內人士透露,臺積電并未為A16制程配備高數值孔徑(High-NA)EUV光刻機,而選擇利用現有的EUV光刻機進行生產。相較之下,英特爾和三星則計劃在此階段使用最新的High-NA EUV

三星清空ASML股份,11年盈利超16倍

根據資料顯示,在2012年,為了支持ASML EUV光刻機的研發與商用,并獲得EUV光刻機的優先供應,在2012年,英特爾、臺積電、三星均斥資入股了ASML。2012年7月,英特爾入股ASML獲得15%股權,并出資10億美元支持

三星1nm時代光刻機體積將增加

三星1nm時代光刻機體積將增加

評論