什么是RAM?

RAM(Random Access Memory)中文是隨機存取存儲器。為什么要強調(diào)隨機存儲呢?因為在此之前,大部分的存儲器都是順序存儲(Direct-Access),比較常見的如硬盤,光碟,老式的磁帶,磁鼓存儲器等等。隨機存取存儲器的特點是其訪問數(shù)據(jù)的時間與數(shù)據(jù)存放在存儲器中的物理位置無關。

RAM的另一個特點是易失性(Volatile),雖然業(yè)界也有非易失(non-volatile)的RAM,例如,利用電池來維持RAM中的數(shù)據(jù)等方法。

RAM主要的兩種類別是SRAM(Static RAM)和DRAM(Dynamic RAM)。

SRAM和DRAM的區(qū)別

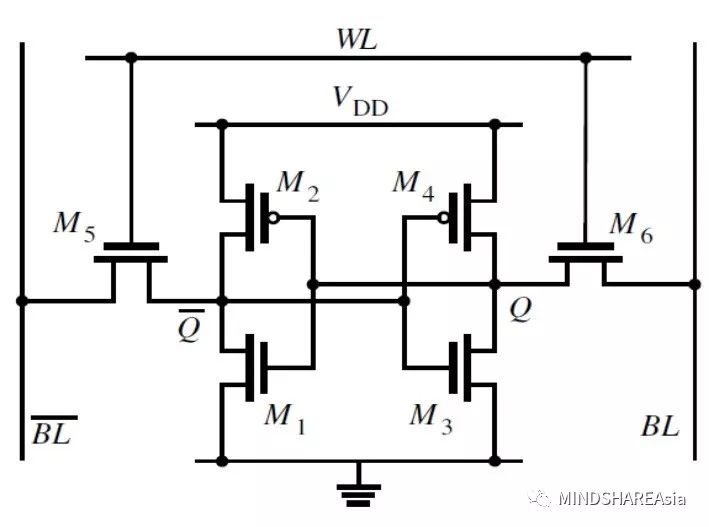

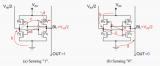

SRAM的S是Static的縮寫,全稱是靜態(tài)隨機存取存儲器。而DRAM的D是Dynamic的縮寫,全稱是動態(tài)隨機存取存儲器。這兩者有什么區(qū)別呢?首先我們看看SRAM的結構,你可以網(wǎng)上搜索一下有很多資料介紹SRAM的,比較出名的是6場效應管組成一個存儲bit單元的結構:

工作原理相對比較簡單,我們先看寫0和寫1操作。

寫0操作

寫0的時候,首先將BL輸入0電平,(~BL)輸入1電平。

然后,相應的Word Line(WL)選通,則M5和M6將會被打開。

0電平輸入到M1和M2的G極控制端

1電平輸入到M3和M4的G極控制端

因為M2是P型管,高電平截止,低電平導通。而M1則相反,高電平導通,低電平截止。

所以在0電平的作用下,M1將截止,M2將打開。(~Q)點將會穩(wěn)定在高電平。

同樣,M3和M4的控制端將會輸入高電平,因NP管不同,M3將會導通,而M4將會截止。Q點將會穩(wěn)定在低電平0。

最后,關閉M5和M6,內(nèi)部M1,M2,M3和M4處在穩(wěn)定狀態(tài),一個bit為0的數(shù)據(jù)就被鎖存住了。

此時,在外部VDD不斷電的情況下,這個內(nèi)容將會一直保持。

下面通過動畫來觀察一下寫0的過程。

寫1操作

這里不再重復,大家可以自己推演一下過程。這里仍然提供寫1過程動畫。

讀操作

讀操作相對比較簡單,只需要預充BL和(~BL)到某一高電平,然后打開M5和M6,再通過差分放大器就能夠讀出其中鎖存的內(nèi)容。

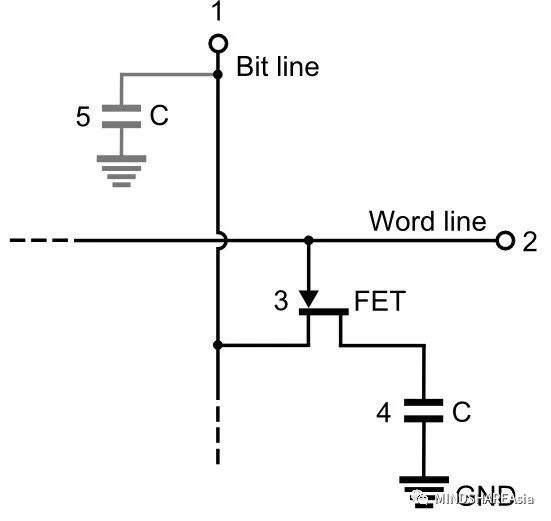

DRAM(Dynamic RAM)是指動態(tài)隨機存取存儲器。與SRAM最大的不同是,DRAM需要通過刷新操作來保持其存儲的內(nèi)容。讓我們先來看看其一個bit存儲單元(Cell)的結構:

其核心部件是4號位的電容C,這個電容大小在pF級別,用來存儲0和1的內(nèi)容。由于電容會慢慢放電,其保存的內(nèi)容將會隨時間推移而慢慢消失。為了保證其內(nèi)容的完整性,我們需要把里面的內(nèi)容定期讀出來再填寫回去。這個操作稱為刷新操作(Refresh)。

其寫操作相對簡單:(我們以寫1為例)

當需要寫1的時候,先將BL(Bit Line)輸入高電平1,然后選中對應的Word Line(同一時間將只有一根WL被選中),打開相應的MOS管,如圖中所示3號位。此時,外部驅(qū)動能力很強,通過一定的時間,4號位的電容將會被充滿。此時,關閉3號位的MOS管。內(nèi)容1將在一定時間內(nèi)被保存在4號位的電容中。寫0的操作與之相反,不同的是將4號位電容中的電荷通過Bit Line放光。然后關閉3號位的MOS管,鎖存相應數(shù)據(jù)。

而讀操作相對來說,較為復雜。我們可以觀察到4號位電容非常小,只有pF級別,而Bit Line往往都很長,上面掛了非常多個存儲單元(cell),我們可以通過5號位的電容來表示。所以當我們直接把3號位的MOS管打開,Bit Line上將基本看不到什么變化。

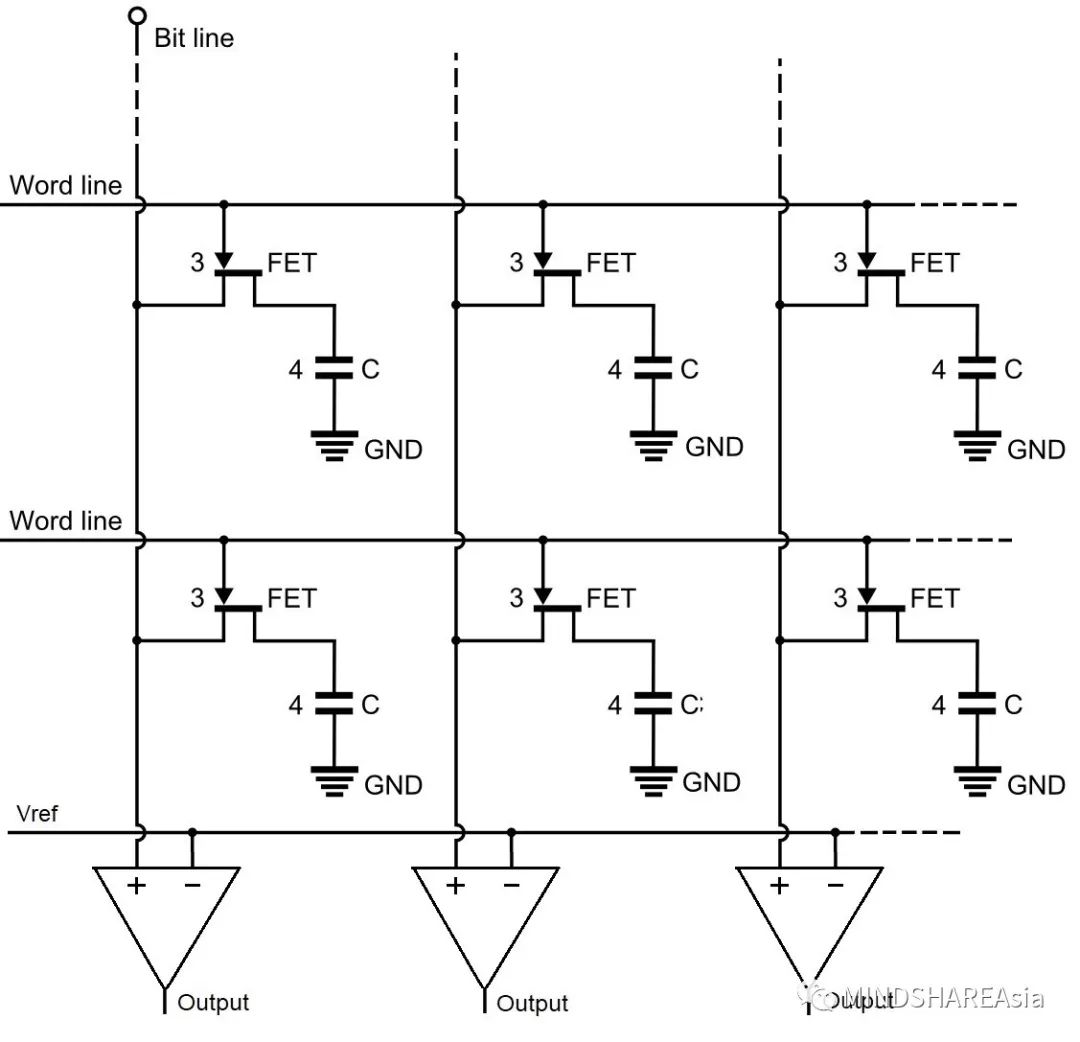

于是有人提出是否能夠采用放大器來放大4號位電容的效果。結構圖如下圖所示:

我們可以定Vref為1/2的VDD電壓,在讀取電容里數(shù)據(jù)之前,我們先將所有Bit Line預充1/2 VDD的電壓。然后,打開Word Line讓選中的電容連接到Bit Line上面,如果原本的內(nèi)容是1,則Bit line的總電壓將會小幅攀升。否則,則會小幅下降。再通過差分放大器,將結果放大從而實現(xiàn)讀操作。

這套方案是可以工作的,但Bit Line的數(shù)量不能太大。否則會導致距離Vref供電處較遠的放大器Vref的值偏低,而導致差分放大器工作異常。同時,對于所謂的1/2 VDD預充,也存在不準的情況。

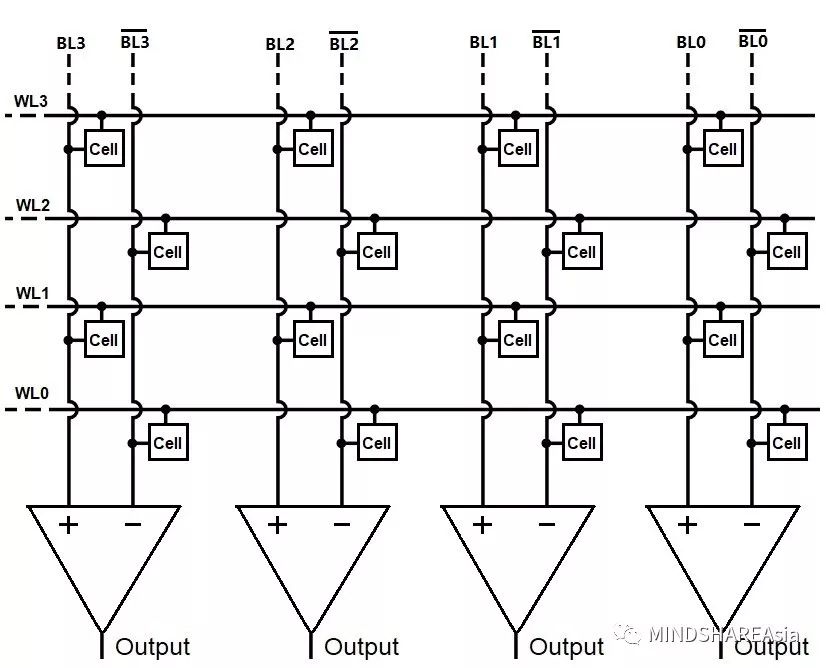

為了解決這個問題,有人提出,不如將原來的一根Bit Line設計成一對Bit Line,當其中一根Bit Line上的Cell被選中時,另一根Bit Line將不會有Cell被選中。從而沒有Cell被選中的Bit Line可以充當放大器的Vref輸入,其長度,負載以及寄生參數(shù)將會和另一根Bit Line十分一致,這樣一來,放大器的工作就更加穩(wěn)定了。結構圖如下所示:

當讀操作之前,我們先將1/2 VDD電壓同時注入到BL和(~BL)上,這個動作被稱為(pre-charge預充電)然后其中一根作為參考,來觀察另一根Bit Line在某個Cell導通后的變化。

最后,我們總結一下區(qū)別:

SRAM成本比較高(6個場效應管組成一個存儲單元)

DRAM成本較低(1個場效應管加一個電容)

SRAM存取速度比較快

DRAM存取速度較慢(電容充放電時間)

SRAM一般用在高速緩存中

DRAM一般用在內(nèi)存條里

-

DRAM

+關注

關注

40文章

2337瀏覽量

184932 -

存儲器

+關注

關注

38文章

7612瀏覽量

165883 -

sram

+關注

關注

6文章

779瀏覽量

115519

原文標題:終于!有人講懂了DRAM和SRAM!

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

AI推理的存儲,看好SRAM?

存儲器IC的應用技巧 【日 桑野雅彥】

S32K312無法使用int_sram_shareable SRAM存儲數(shù)據(jù)怎么解決?

存儲器IC的應用技巧 [日 桑野雅彥]

DRAM基本單元最為通俗易懂的圖文解說

DRAM與NAND閃存市場低迷,DRAM現(xiàn)貨價格持續(xù)下滑

DRAM的基本構造與工作原理

SRAM和DRAM有什么區(qū)別

DRAM存儲器的基本單元

DRAM內(nèi)存操作與時序解析

評論