本文介紹了動態隨機存取器DRAM的基本結構與工作原理,以及其在器件縮小過程中面臨的挑戰。

DRAM的歷史背景與發展

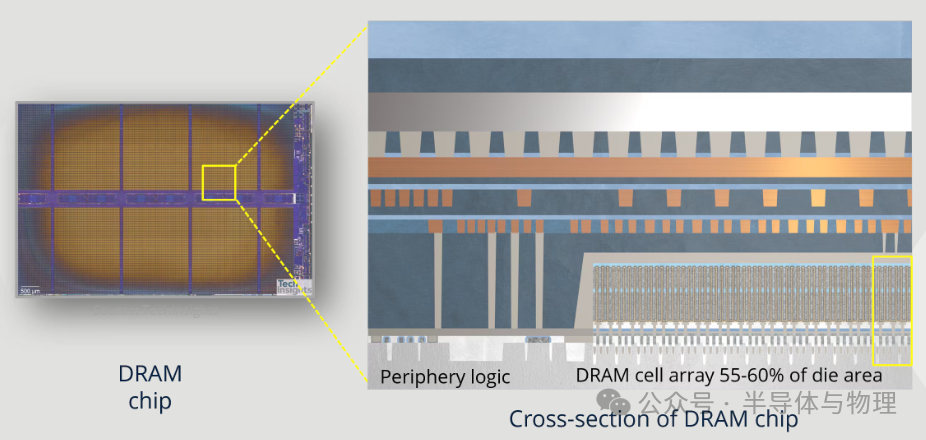

動態隨機存取器(Dynamic Random Access Memory,簡稱DRAM)是計算機系統中用于短期數據存儲的一種半導體存儲器。它由IBM的研究員羅伯特·H·登納德(Robert H. Dennard)于1967年發明,并在隨后的幾十年間成為了計算機和電子設備中最常用的內存類型之一。由于其高密度、低成本的特點,DRAM被廣泛應用于個人電腦、服務器、移動設備等各種計算平臺。

DRAM的基本構造與工作原理

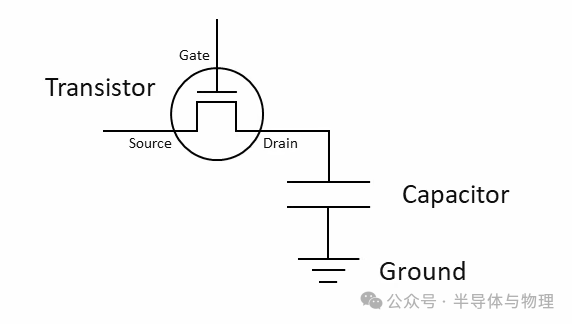

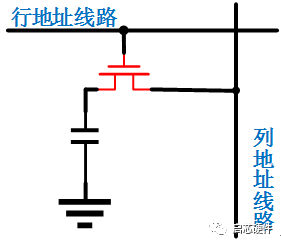

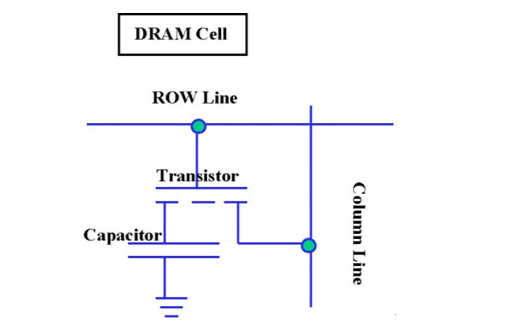

一個典型的DRAM單元包含兩個主要組件:一個作為訪問的晶體管和一個用于數據存儲的電容器。這種設計允許每個存儲單元僅需占用極小的空間,從而實現高密度的數據存儲。

訪問晶體管(Access Transistor):這是一個MOSFET晶體管,負責控制外部電路是否可以讀取或寫入到相連的電容器中。當晶體管導通時,它可以將電荷加載到電容器上或者從電容器中釋放電荷;而當晶體管關閉時,則阻止任何電流通過,保持電容器中的電荷狀態不變。

存儲電容器(Storage Capacitor):電容器是用來實際保存信息的地方。電容器充電代表邏輯值“1”,未充電則代表邏輯值“0”。為了確保數據的正確性,電容器需要定期刷新,這是因為電容器會逐漸失去其上的電荷,這就是所謂的“動態”特性。

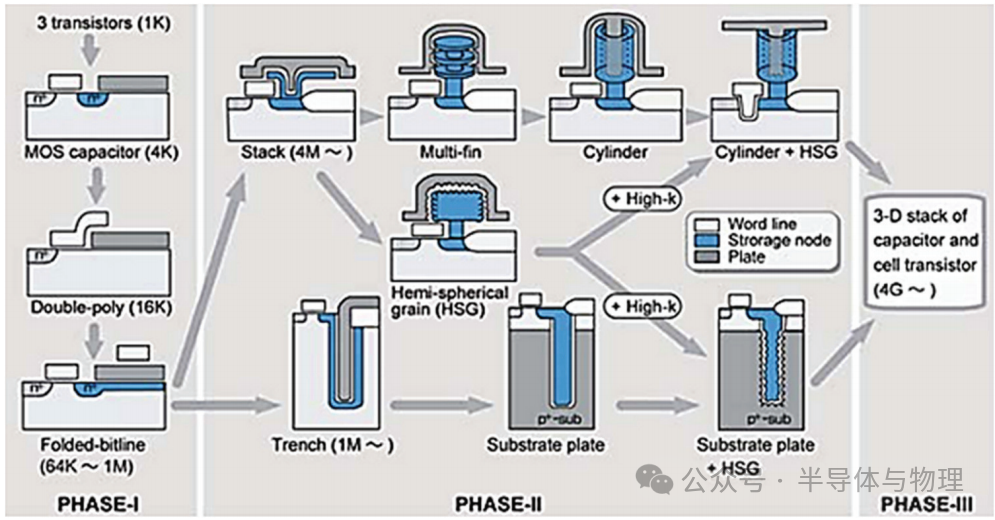

最初,這些器件都是平面型的,使用二氧化硅作為柵極絕緣層和電容器介質。隨著技術的進步,為了在減小特征尺寸的同時保持足夠的電容值C不變,工程師們開始采用高介電常數(high-k)材料如氮化硅來替代傳統的二氧化硅,以及使用氧化物/氮化物/氧化物(ONO)堆棧來解決應力問題。

DRAM三維結構的引入

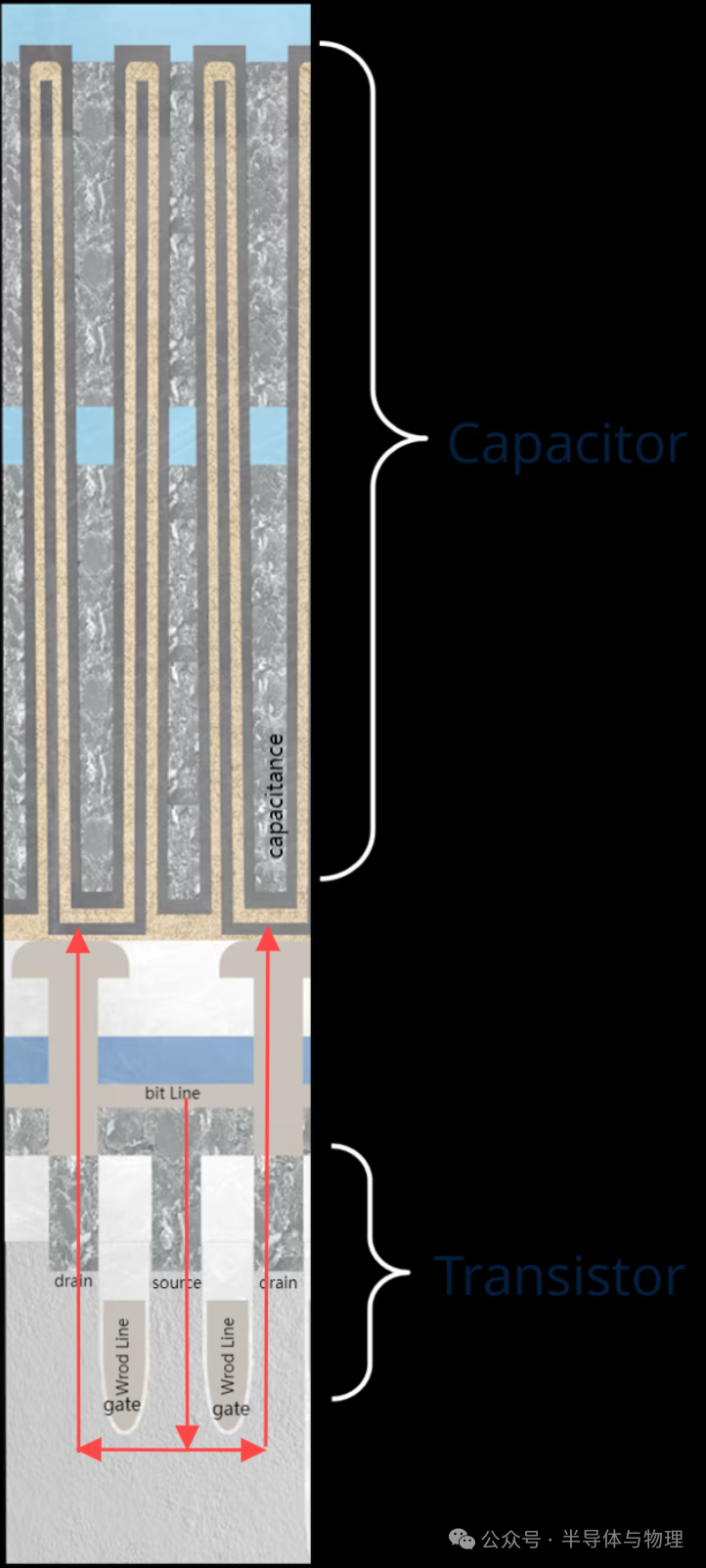

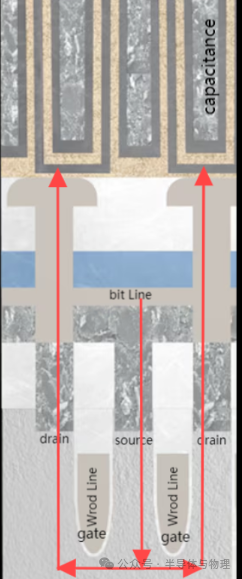

隨著工藝節點的不斷縮小,特別是進入80納米以下后,短溝道效應導致了更高的源漏泄漏電流和更短的數據保留時間。為了解決這些問題,DRAM訪問晶體管從平面結構轉變為三維結構,例如引入了凹槽柵極(Recessed Gate, RG)晶體管和埋入式字線(Buried Word-Line, BWL)技術。這些改進增加了通道長度,有助于減少泄漏并維持數據保持時間,同時通過增加通道寬度提高了驅動電流,且不需要增大器件的特征尺寸。

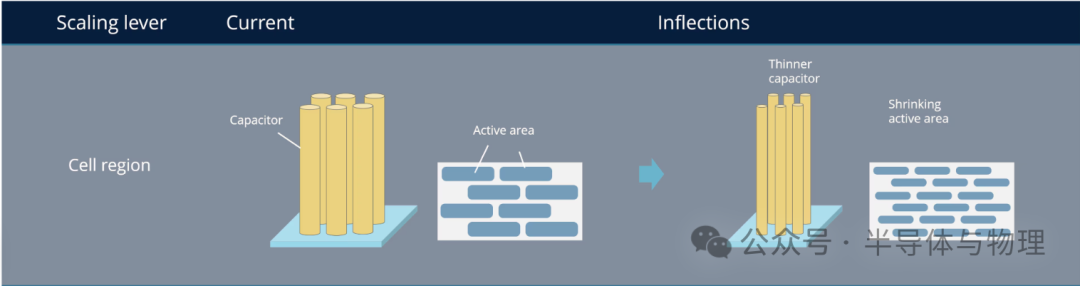

此外,為了進一步壓縮存儲單元面積,人們還開發出了各種形狀復雜的電容器,如深溝槽電容器和堆疊柱狀電容器。前者利用硅片內部的空間構建電容器,后者則是將多個電容器垂直堆疊起來,以此來提高單位面積內的電容值而不必增加芯片的物理尺寸。

縮放挑戰與解決方案 隨著制造技術的發展,DRAM的特征尺寸不斷縮小,但隨之而來的是新的挑戰。例如,當DRAM的特征尺寸按照的比例縮小時,如果要保持電容C、介電常數k和距離d不變,則圓柱形電容器的高度必須相應地增加,以補償直徑上的減少。這意味著長寬比(aspect ratio)會加倍,給制造帶來了新的挑戰。因此,研究人員一直在尋找具有更高介電常數的新材料,以降低所需電容值,并優化晶體管的設計以減少關閉狀態下的泄漏電流。

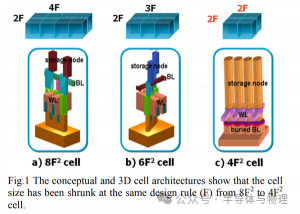

6F2架構DRAM簡介

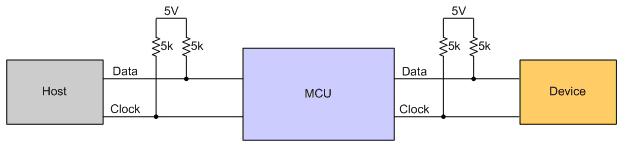

如今業界所制造最先進的DRAM采用的是6F2架構,就是每個最小bit的單元占6倍最小線寬的的平方面積。即一個BitLine可以為兩個電容充電,如下圖紅色箭頭bit Line電流從source由Word Line gate流向drain,從而對電容進行充電或放電。

參考文獻:[1]DRAM [2]3D IC devices, technologies, and manufacturing / Hong Xiao.

-

DRAM

+關注

關注

40文章

2316瀏覽量

183589 -

存儲器

+關注

關注

38文章

7507瀏覽量

163963

原文標題:DRAM(動態隨機存取器)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DRAM的工作原理 DRAM存儲數據和讀取數據過程說明

【內存知識】DRAM芯片工作原理

電磁繼電器的構造及工作原理

MOS管的構造/工作原理/特性

DRAM存儲器的工作原理詳細介紹

硬盤的工作原理和內部構造

DRAM的基本構造與工作原理

DRAM的基本構造與工作原理

評論